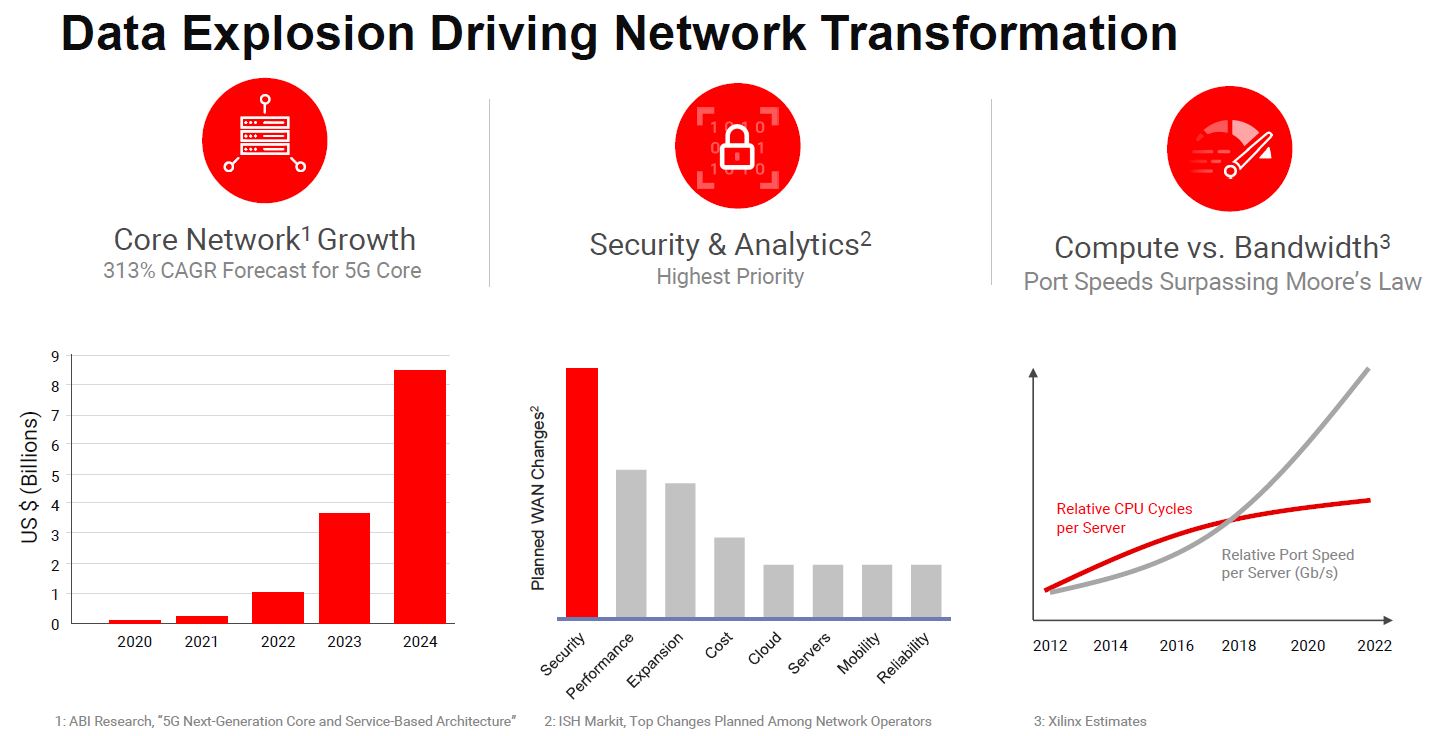

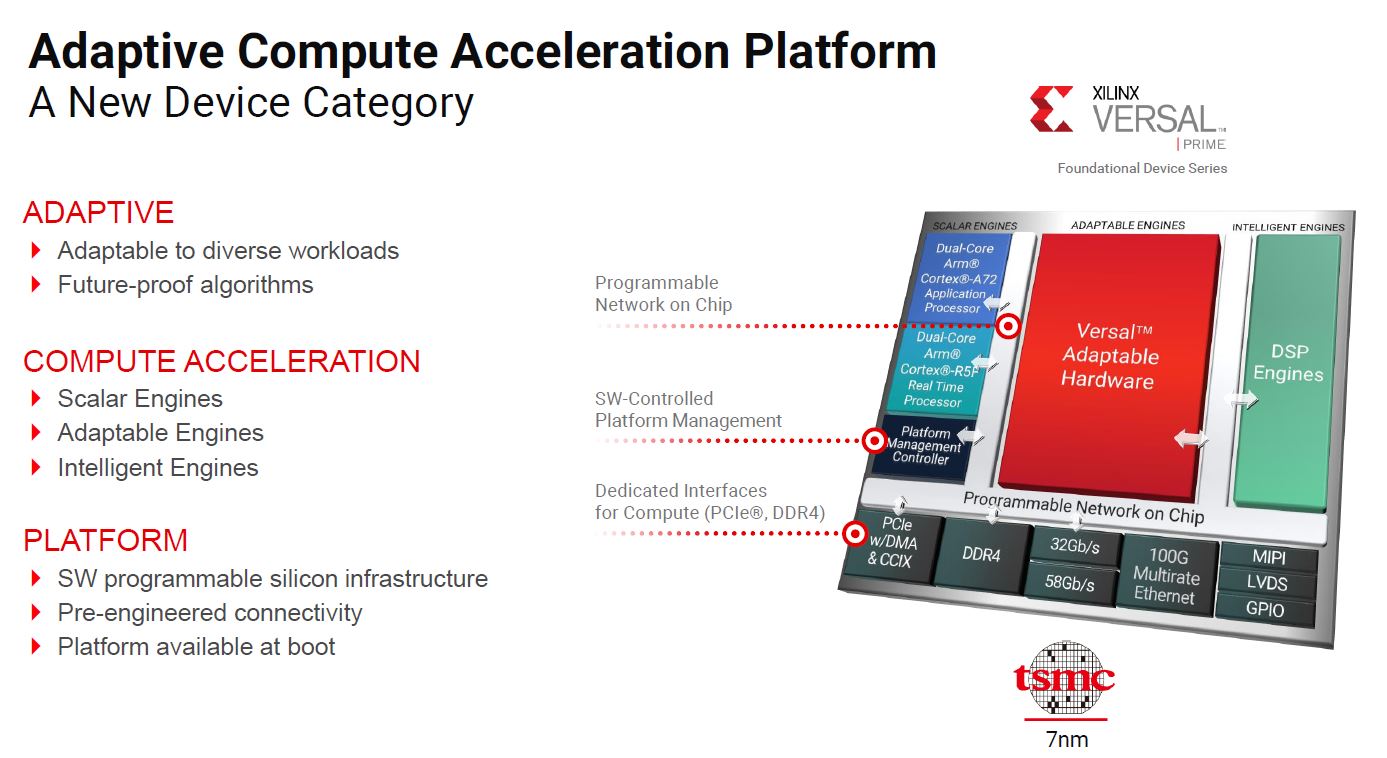

The new Xilinx Versal Premium is an I/O optimized next-generation FPGA platform Xilinx calls an ACAP. It is primarily designed to deal with bandwidth growth and increased traffic density coming with 5G. Since our readers like to see some of these predictions, Xilinx also said that it is expecting a 313% CAGR for 5G core network growth. Against that backdrop, Xilinx is launching Versal Premium.

Xilinx Versal Premium Overview

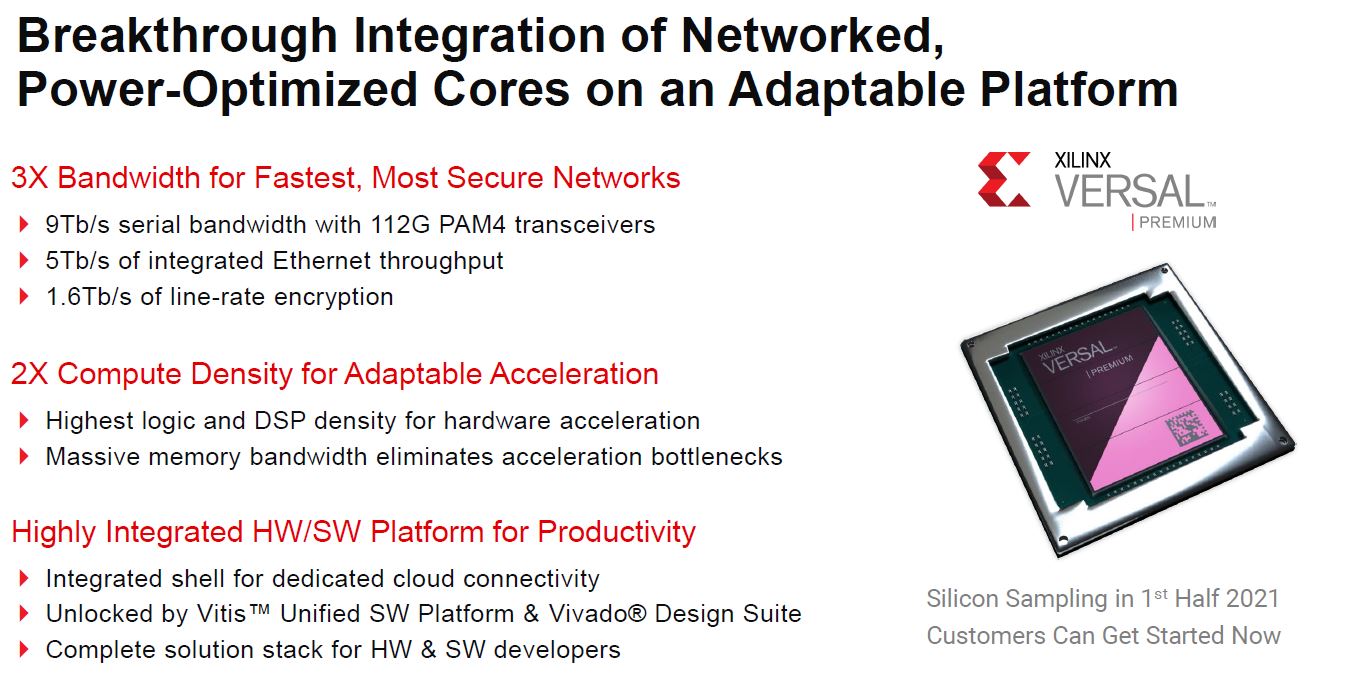

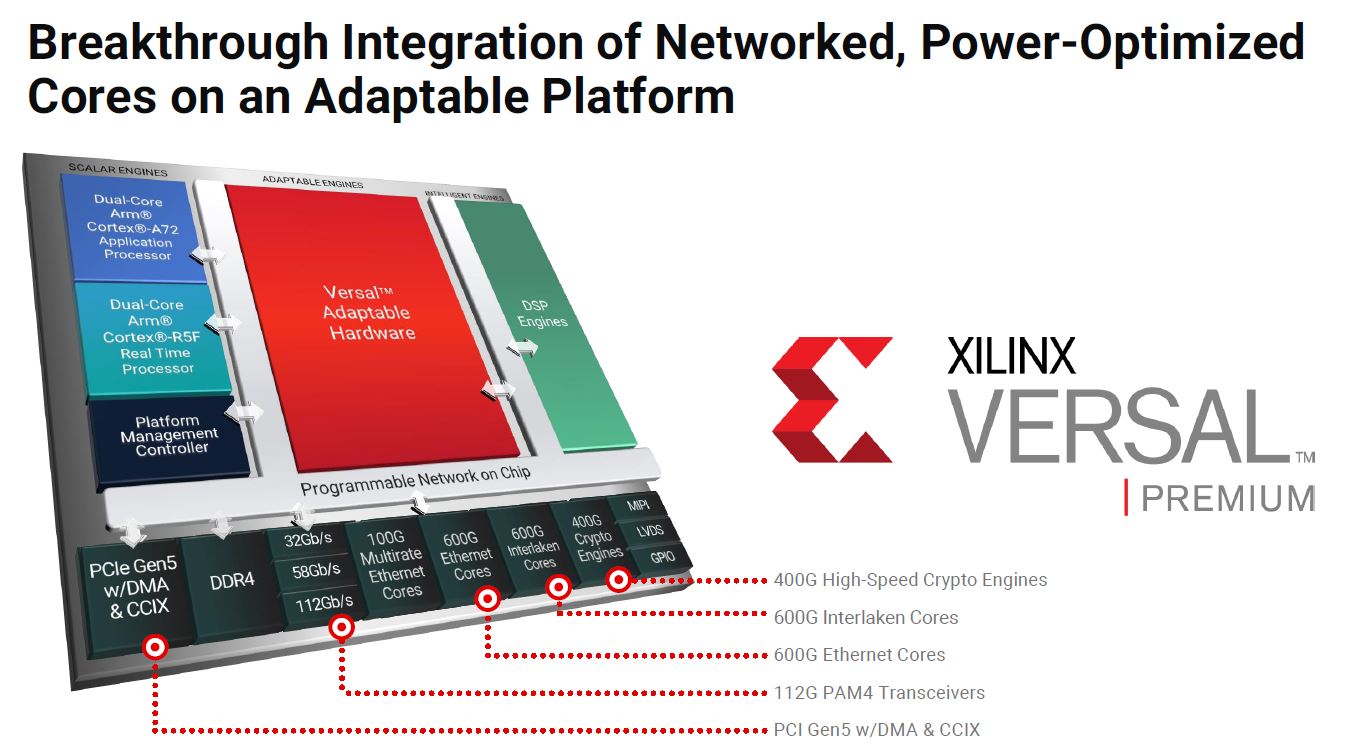

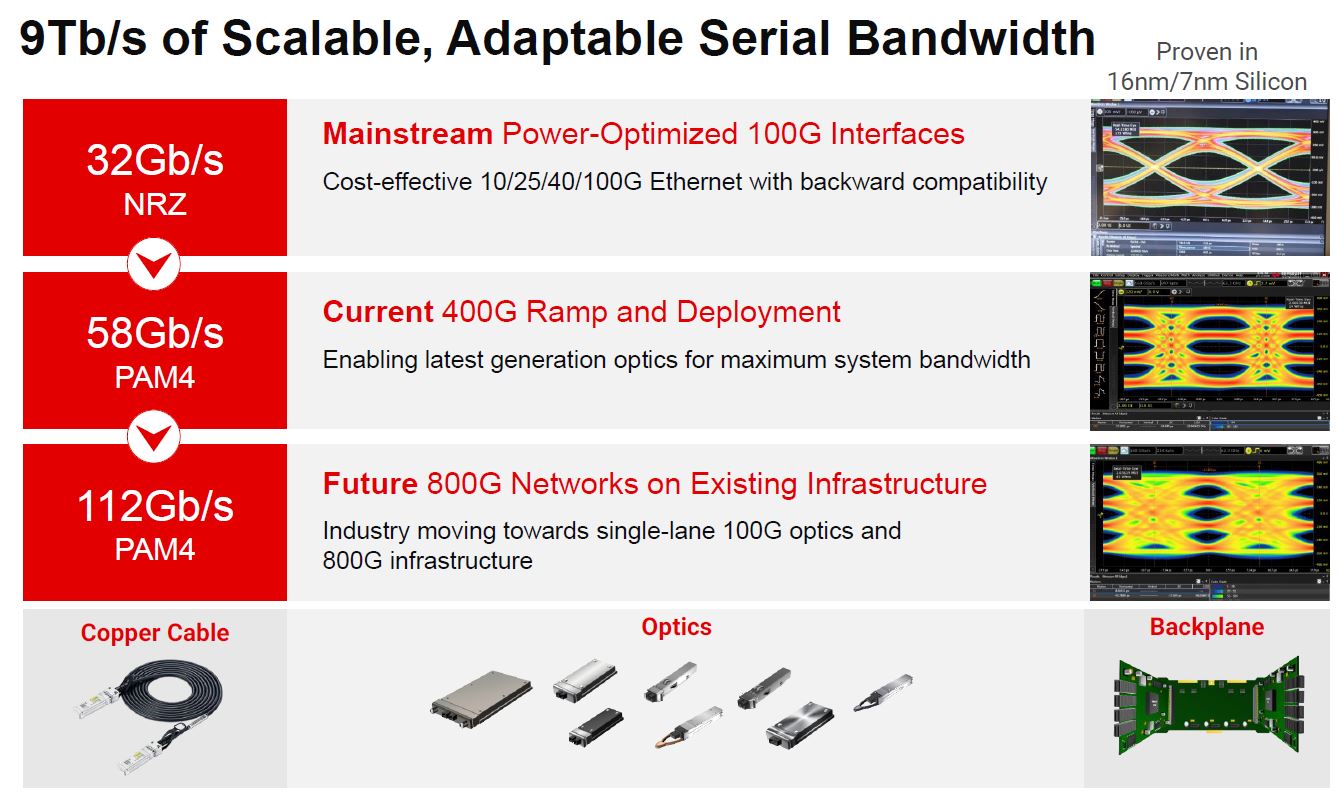

The new XilinxVersal Premium is in ACAP with three times the bandwidth and twice the compute density of its previous generation. There is a roadmap in the line to provide 112G PAM4 transceivers, 5Tbps of Ethernet throughput, and up to 1.6Tb/s of encryption throughput.

If you need an ACAP recap you can read our piece Xilinx Versal ACAP Launch Presentation from XDF 2018. We should note here that Xilinx announced the ACAP in 2018 and here we are in 2020 with a product that will be sampling in 2021. Versal AI Core and Prime have been shipping since mid-2019 but this is still far from a quick rollout.

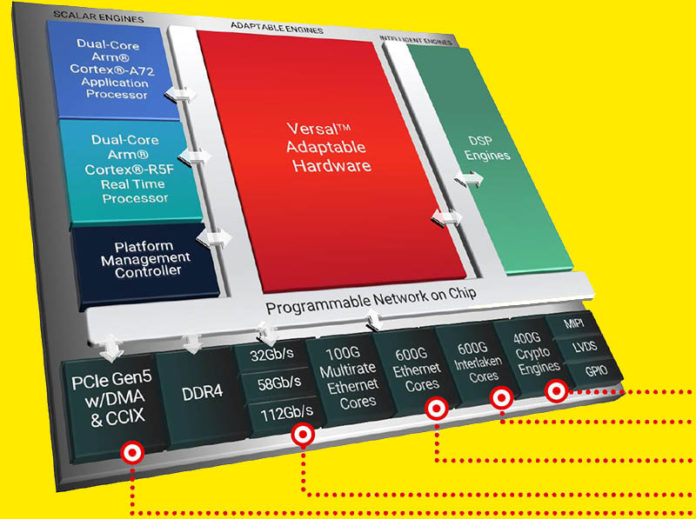

Part of the Xilinx Versal strategy is to add additional hardened I/O and logic for large markets. This is a trend that has been happening for years. There are some items that you want flexibility and some that it is fine to make assumptions that increase efficiency.

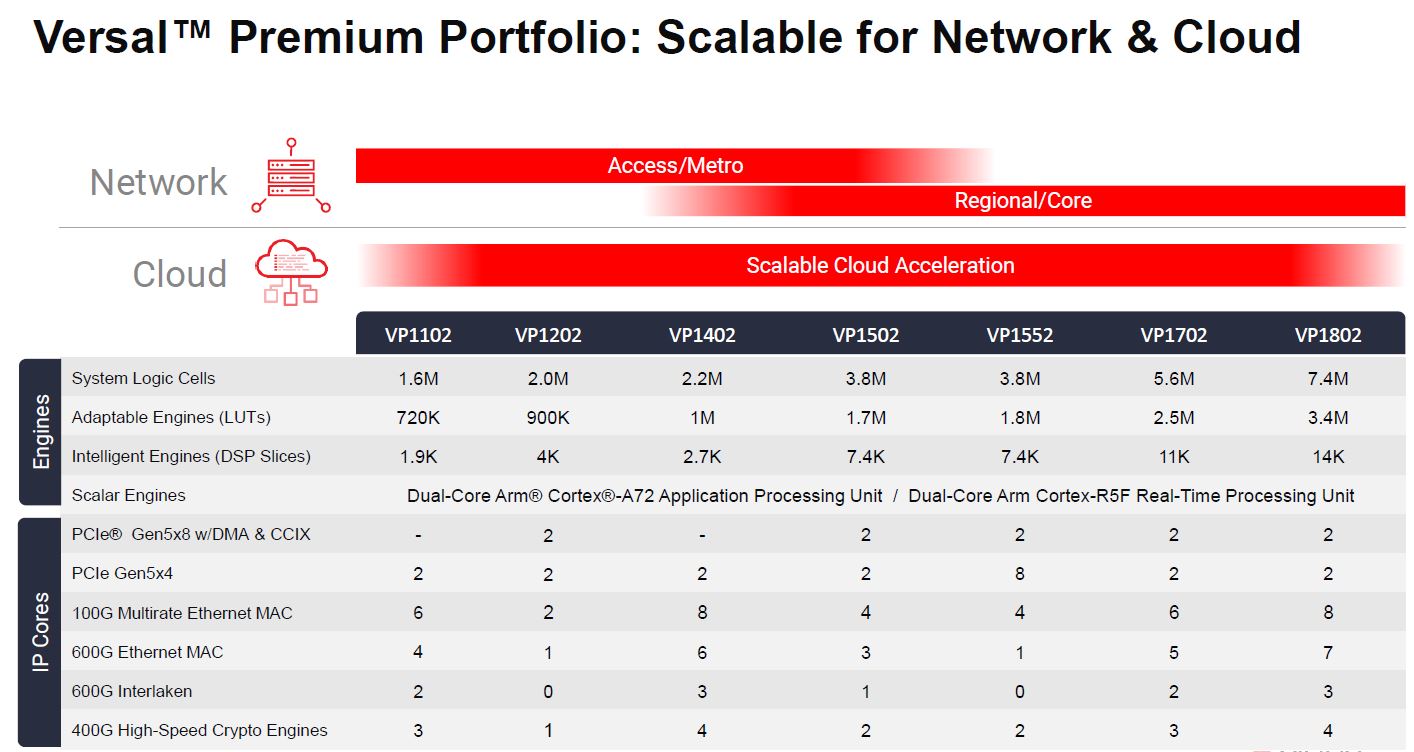

Features will include PCIe Gen5, 112G PAM4, 600G Ethernet and Interlaken Cores, 400G high-speed crypto for security. Along with PCIe Gen5, Xilinx says this will support both CCIX and CXL. Here is the product family table so you can see the SKU stack. That Xilinx VP1802 has a lot going on.

One of the areas that Xilinx is pushing here is large amounts of serial bandwidth, specifically up to 9Tbps. This is designed to service next-generation core networks.

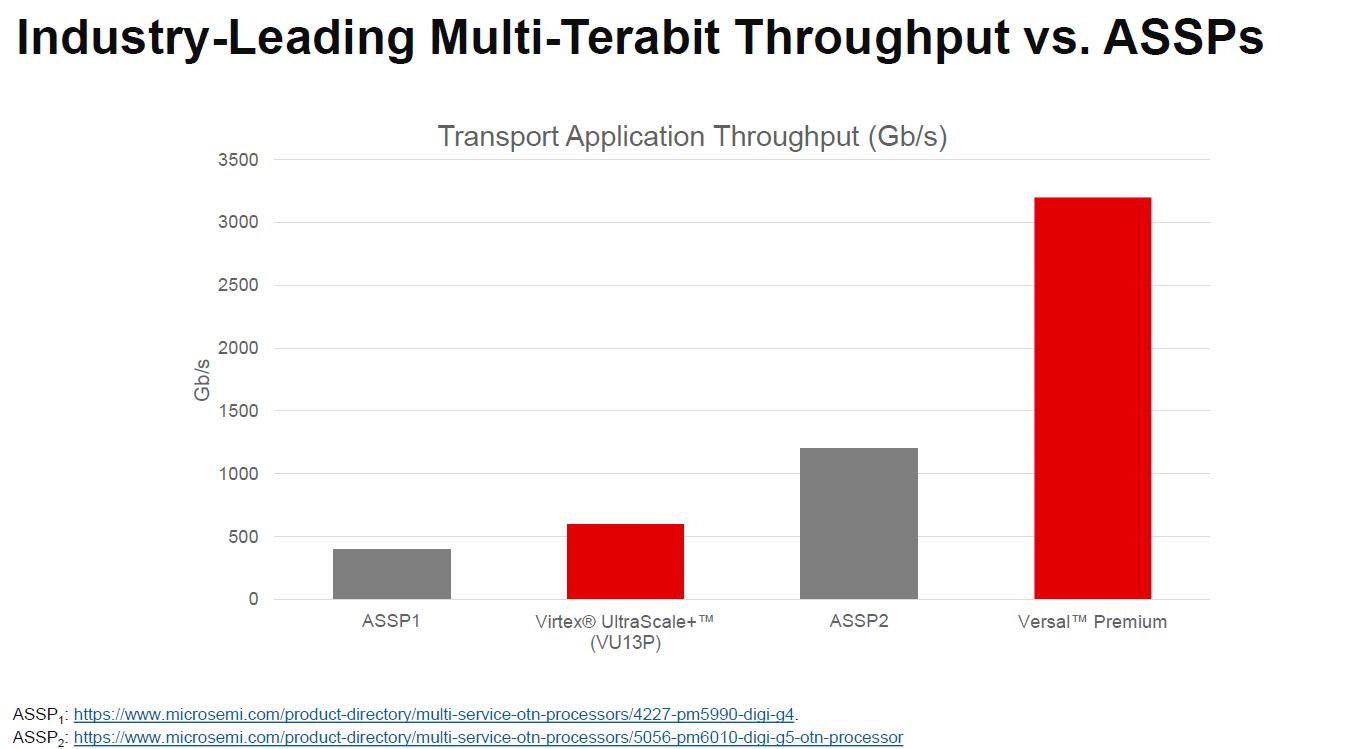

Here Xilinx is showing competitive performance versus the Microchip multi-service OTN processors.

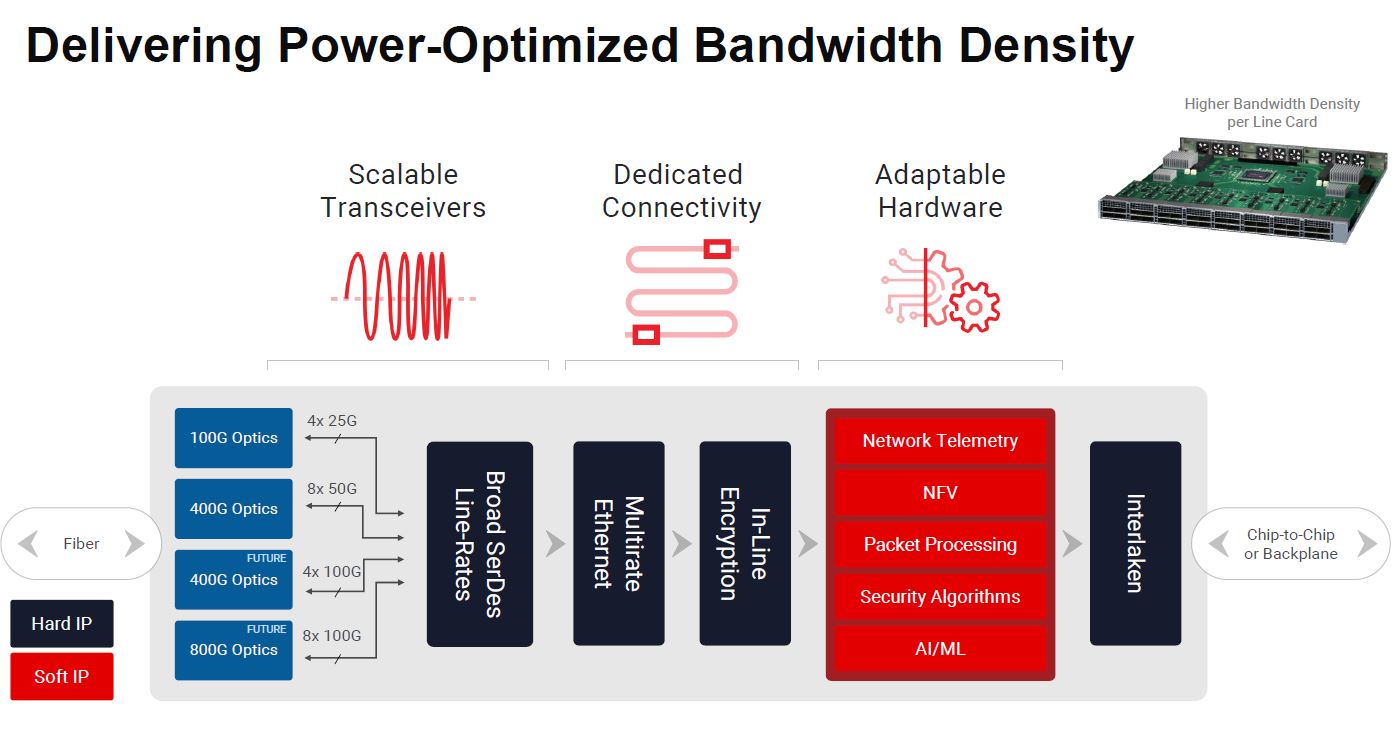

Part of the ACAP design is being able to use both the hard IP along with the flexible FPGA logic elements to build efficient and flexible pipelines. Here is a simplified example for a line card pipeline.

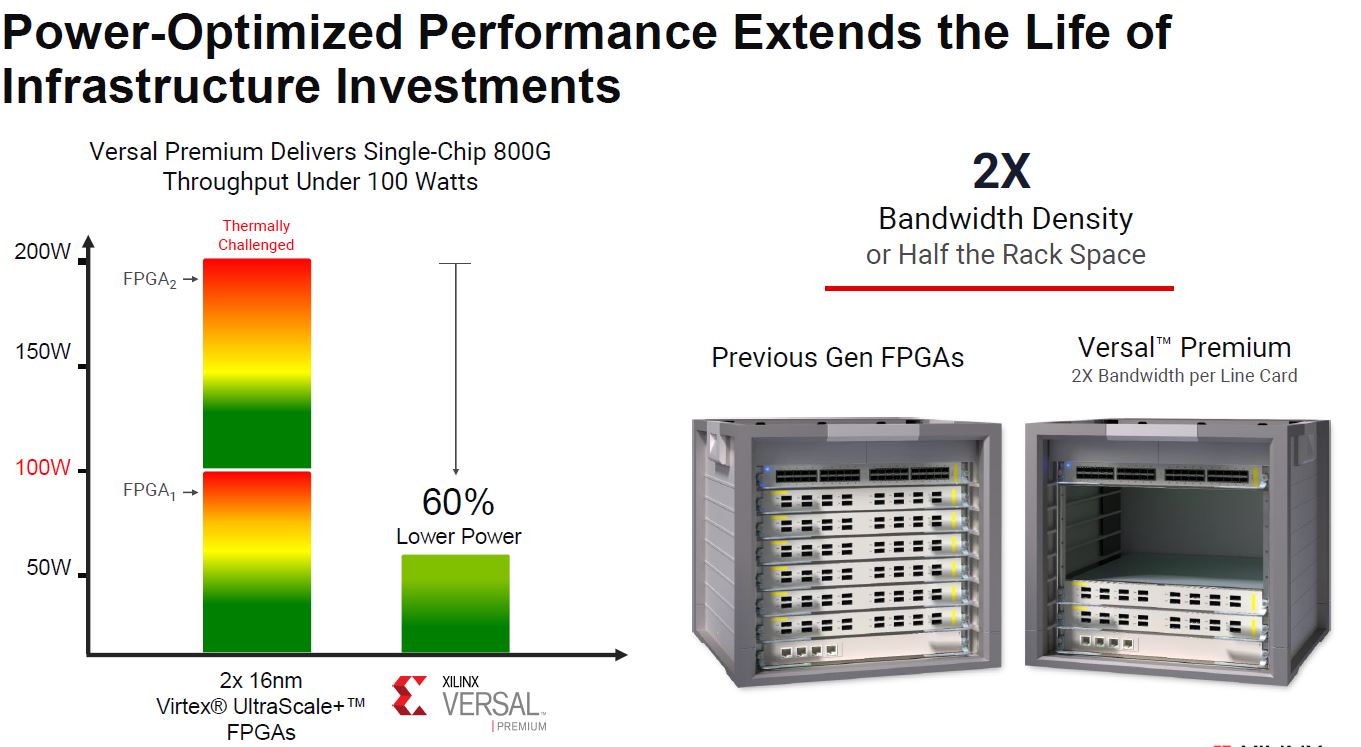

With these new features, Xilinx thinks that it can achieve over a 2x increase in performance per watt which means higher densities.

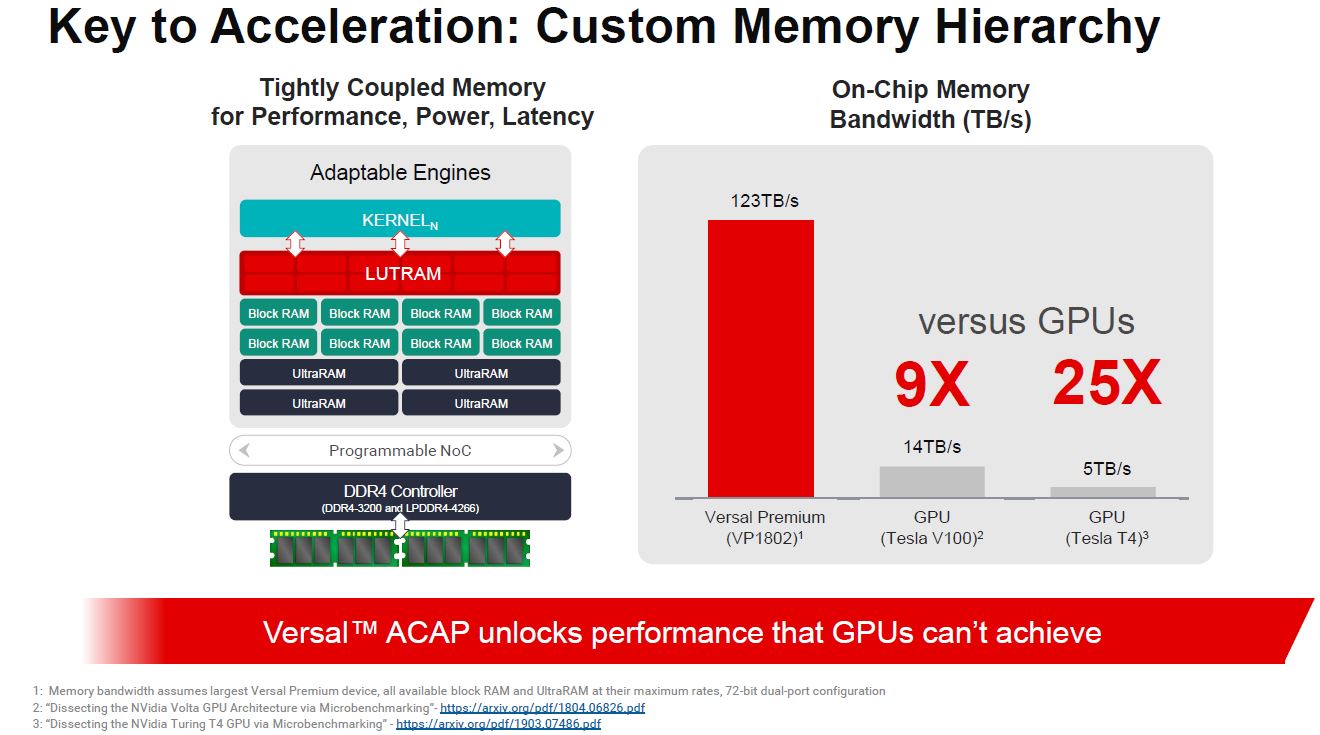

Xilinx also notes its memory hierarchy. In the ACAP FPGA memory is distributed on the chip’s fabric so one can get higher bandwidth than for GPUs where memory sits off-chip. This is similar to what we see AI companies push like Cerebras Systems.

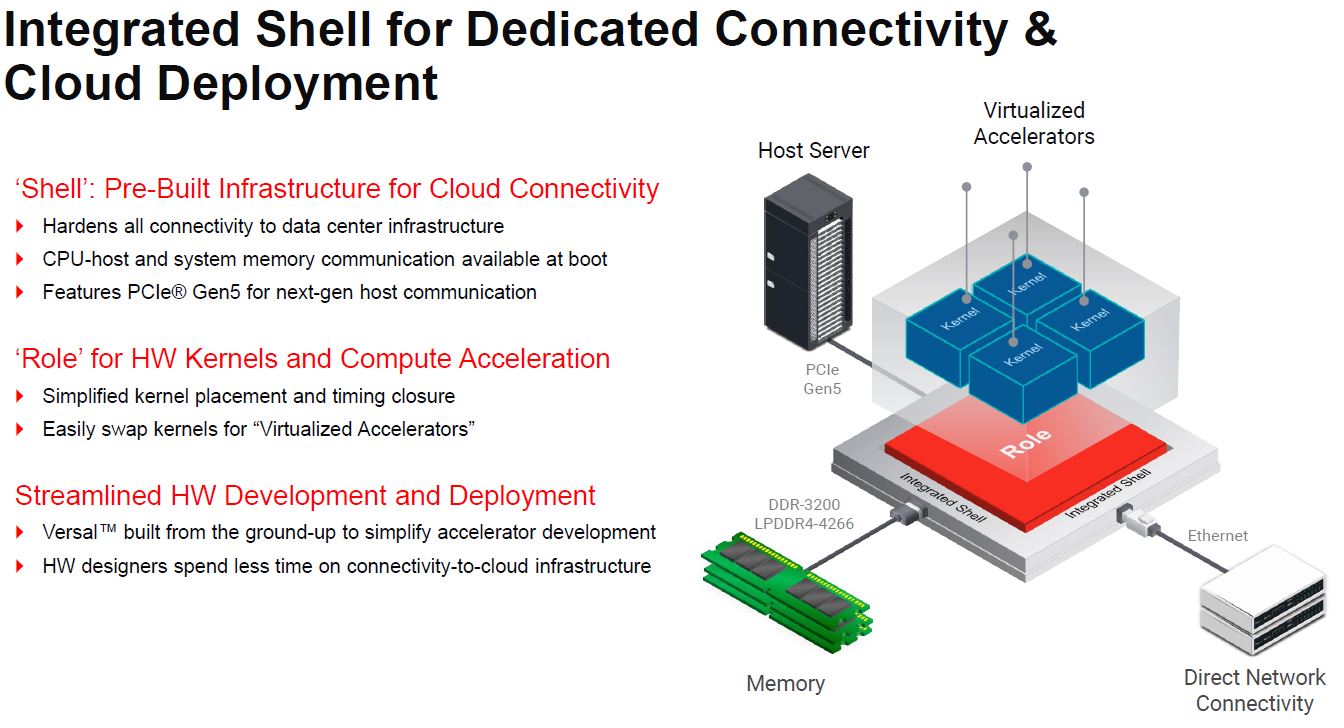

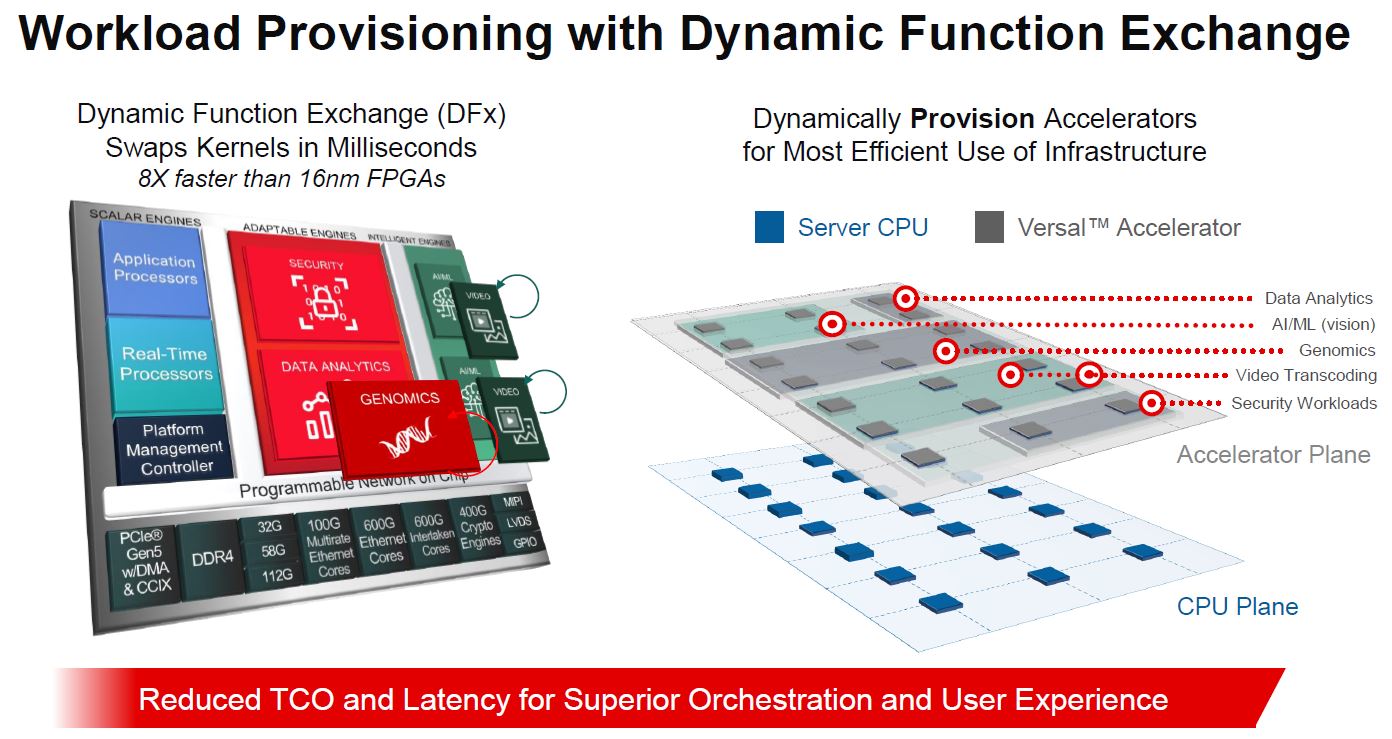

One of the other aspects that Xilinx is pointing to with the Versal Premium is that the FPGA has a pre-built infrastructure that allows basic connectivity to be in place for kernels to take advantage of without having to do basic connectivity work.

That shell combined with the Dynamic Function Exchange (DFx) means that one can swap kernels relatively quickly using this overall shell.

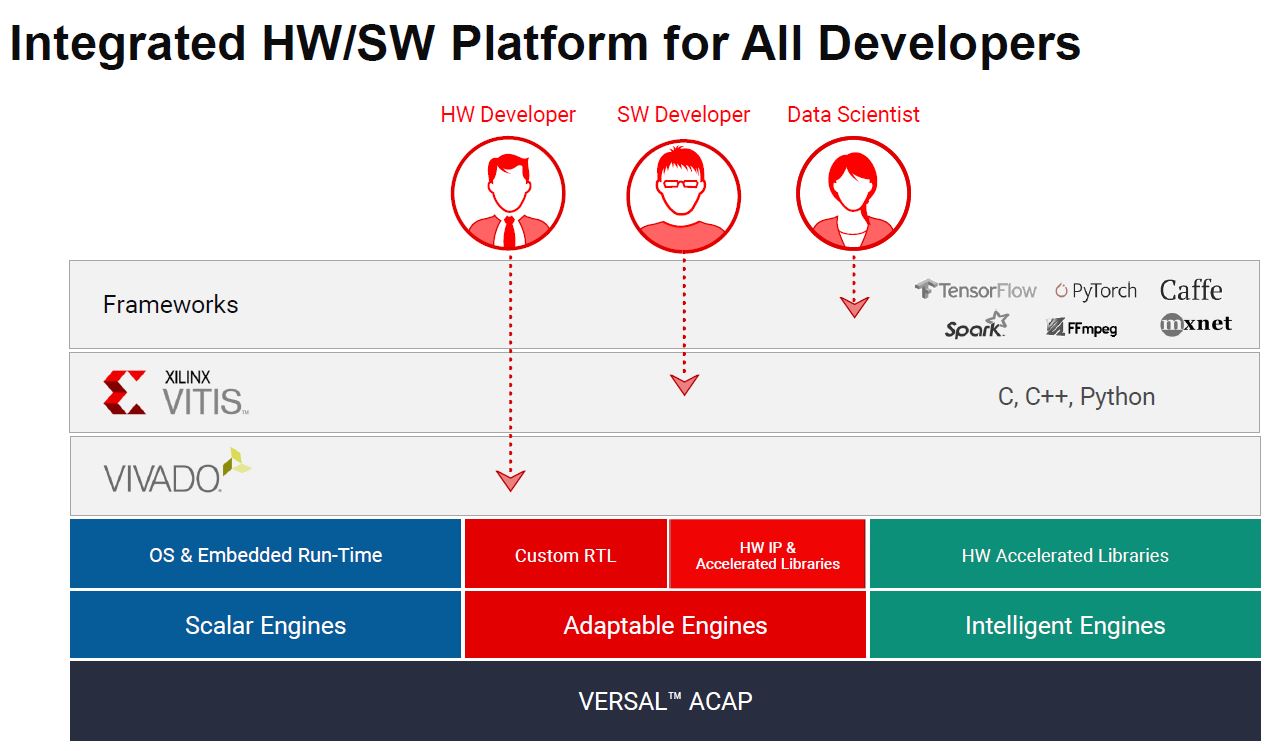

In the ease-of-use category, Xilinx has been working to provide tools beyond Vivado and higher-level tools like the Vitis Unified Software Platform Launched to make its ACAPs more accessible.

This is one of those areas that Xilinx is investing in to give more markets and developers access to its hardware.

Final Words

There are a few questions we are sure our readers will have. We asked about support for CXL with PCIe Gen5. Xilinx did not confirm CXL support in our pre-briefing questioning but confirmed both CXL and CCIX support just a few days before the announcement went live. We also asked about an Alveo version to bring these chips to a PCIe form factor for easy integration. Xilinx did not make an announcement but we got the sense that this is highly likely given the company’s direction. We need to wait until 2021 for this technology, so there is still a lot of time between the announcement and when hardware will start to ship.