In a highly anticipated move ever since the Xilinx acquisition of SolarFlare was announced for SmartNIC capabilities, we finally have a card resulting from that acquisition. Specifically, the Xilinx Alveo U25 SmartNIC is the company’s latest Alveo product and one we are extraordinarily excited about. 2020 will be the year that the SmartNIC market heats up, and this is will be one of the key entries into the market.

Xilinx Alveo U25 SmartNIC Overview

The new Xilinx Alveo U25 is a platform based on a Xilinx FPGA designed to bring high-performance networking to servers.

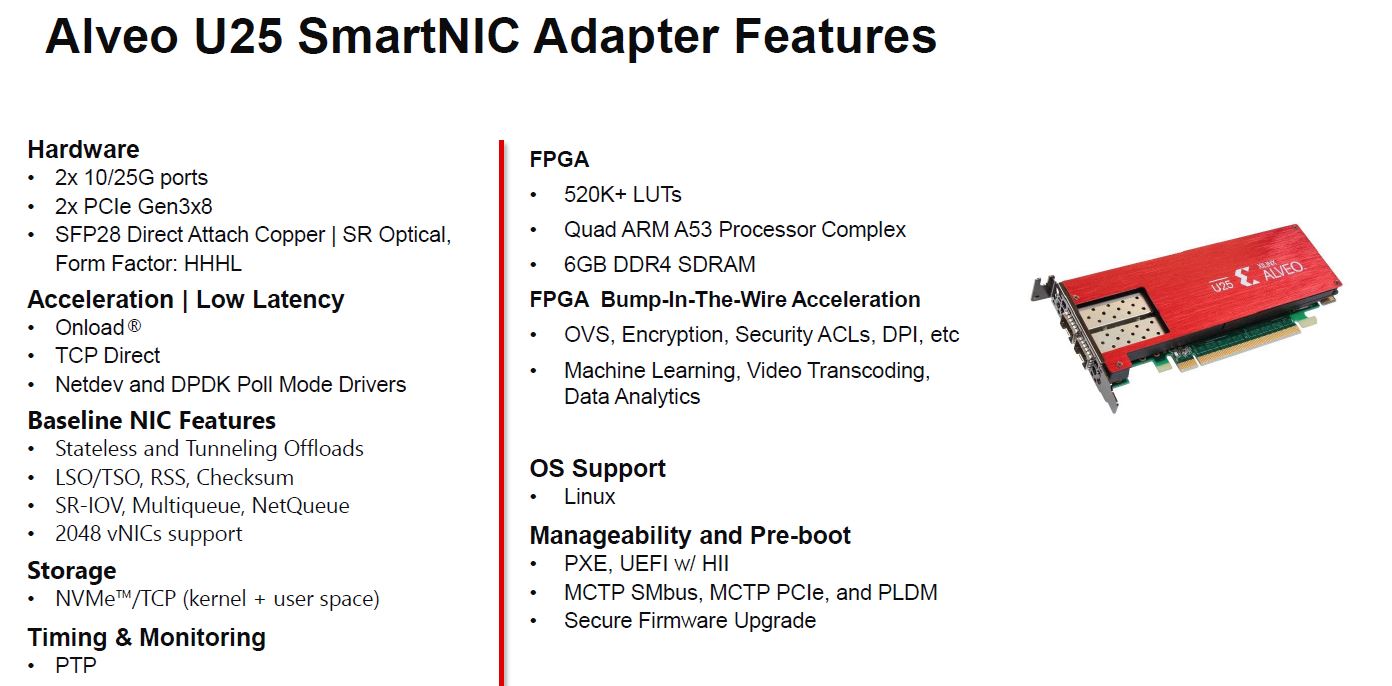

The NIC itself is a PCIe Gen3 x8 NIC with dual 25GbE. The FPGA has over a half million LUTs as well as a quad-core Arm A53 processor. Arm is dominating the SmartNIC space at this point since having low-power cores helps the programmability of the solution as well as running control planes. The card also has 6GB of DDR4 memory onboard, much higher than many of your lower-end NICs but important to increase the domain addressability of the solution.

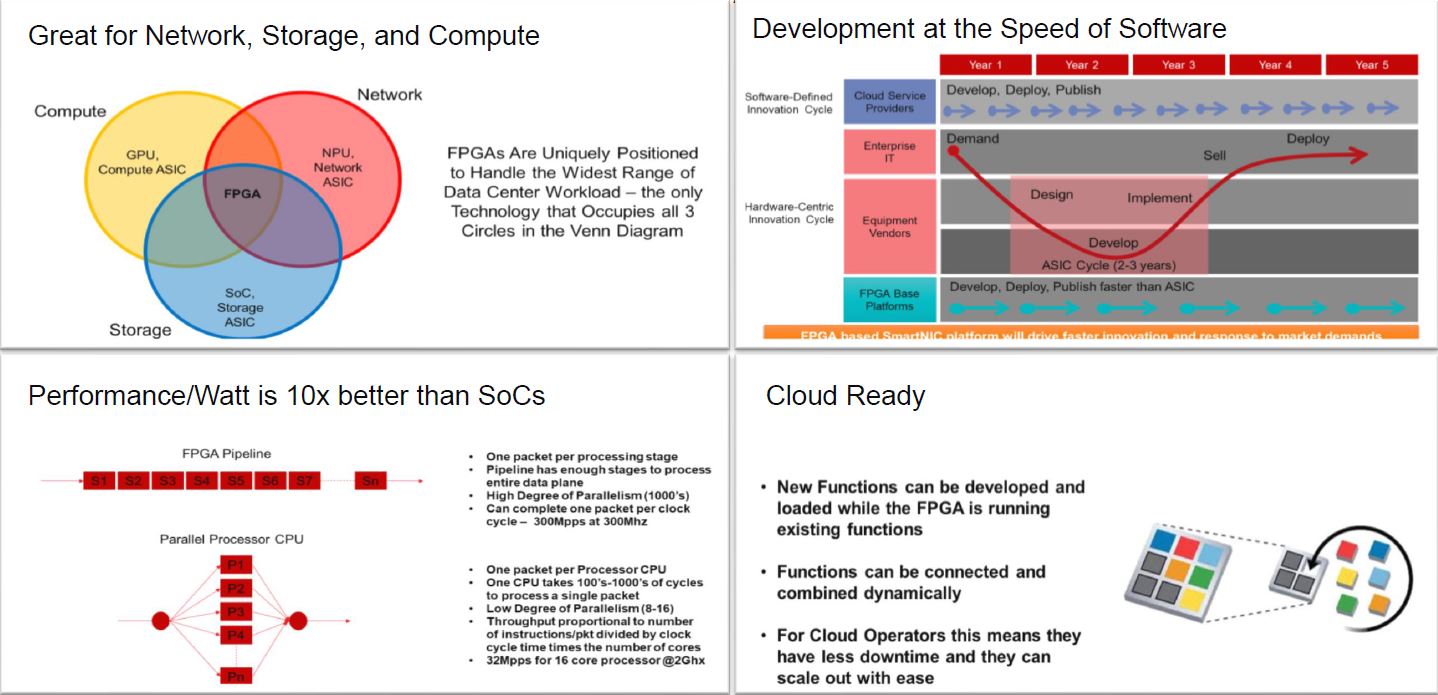

Xilinx is pushing offload features as well as the flexibility and programmability of the Alveo U25 to offload tasks from expensive CPU cores. For cloud providers such as AWS and Microsoft, this offload helps lower tasks a cloud server’s primary CPUs need to handle. In turn, this increases the CPU cores available in a server. When you are a cloud provider and you meter your product by CPU core availability, this has a direct impact.

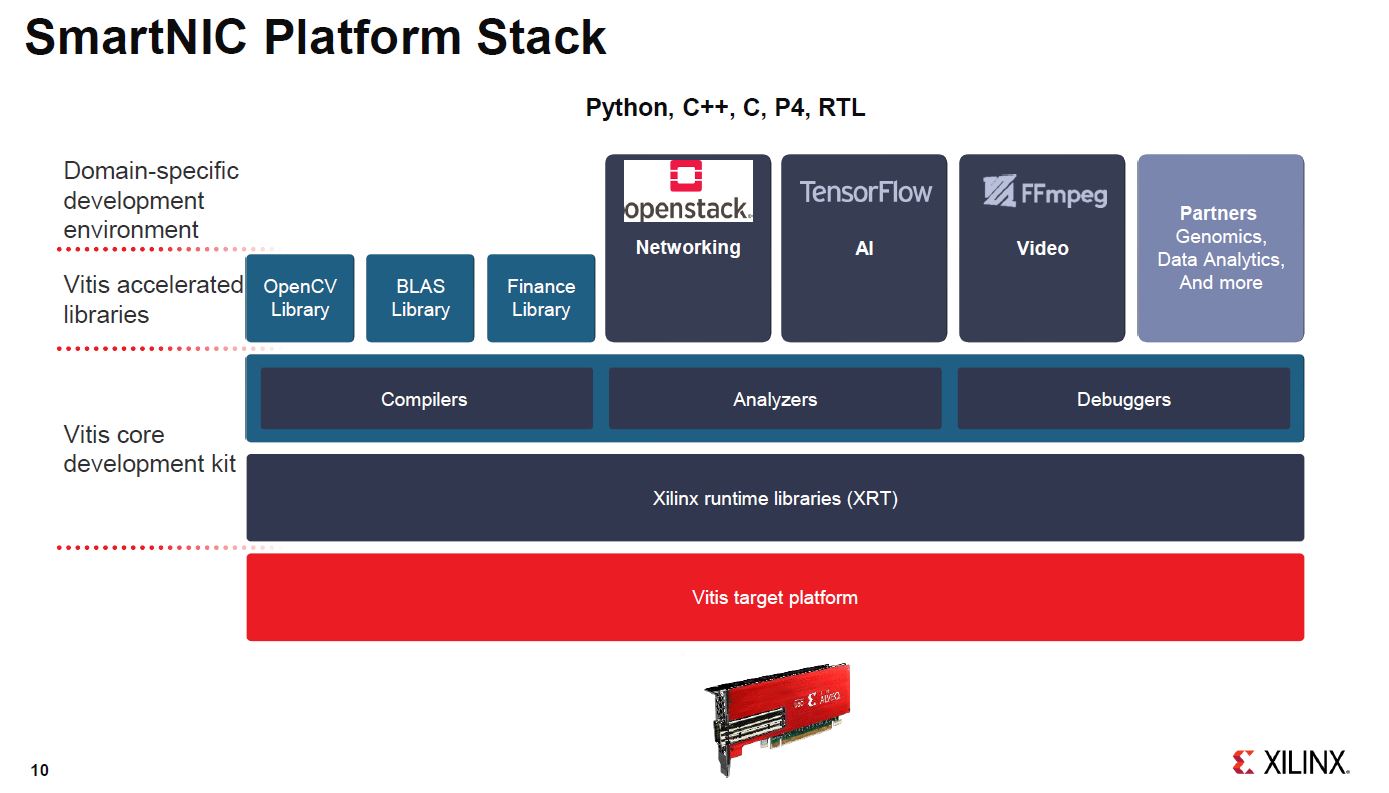

By utilizing customized pipelines in the FPGA, one can create efficient network processing that is also flexible. Many SmartNIC solutions pass network processing tasks to an array of general-purpose Arm cores, so Xilinx sees this as more efficient. The Alveo U25 also incorporates Solarflare technology from the acquisition.

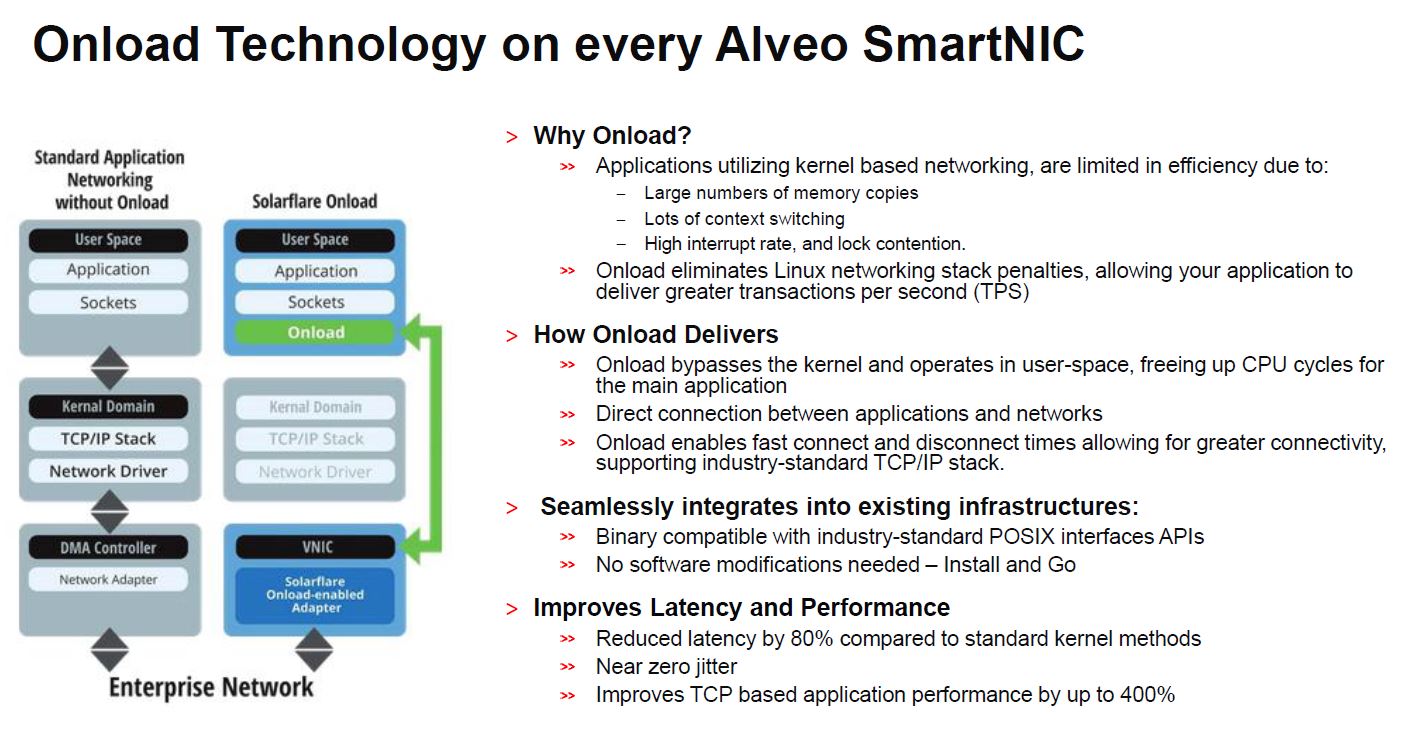

Perhaps the gem, from a technology perspective, of the acquisition is Solarflare’s Onload Technology. Solarflare’s (not Xilinx’s) Onload Technology bypasses the Linux kernel and networking stack to increase performance and lower overheads. The reason Solarflare was able to build a successful NIC business in the midst of giant companies in the networking space was by going after high-performance segments such as trading houses using this technology. Onload is one of those pieces of technology that those who use it generally think it is a game-changer rather than a marginal improvement.

The U25 can take advantage of Vitis and other FPGA programming tools as one would expect.

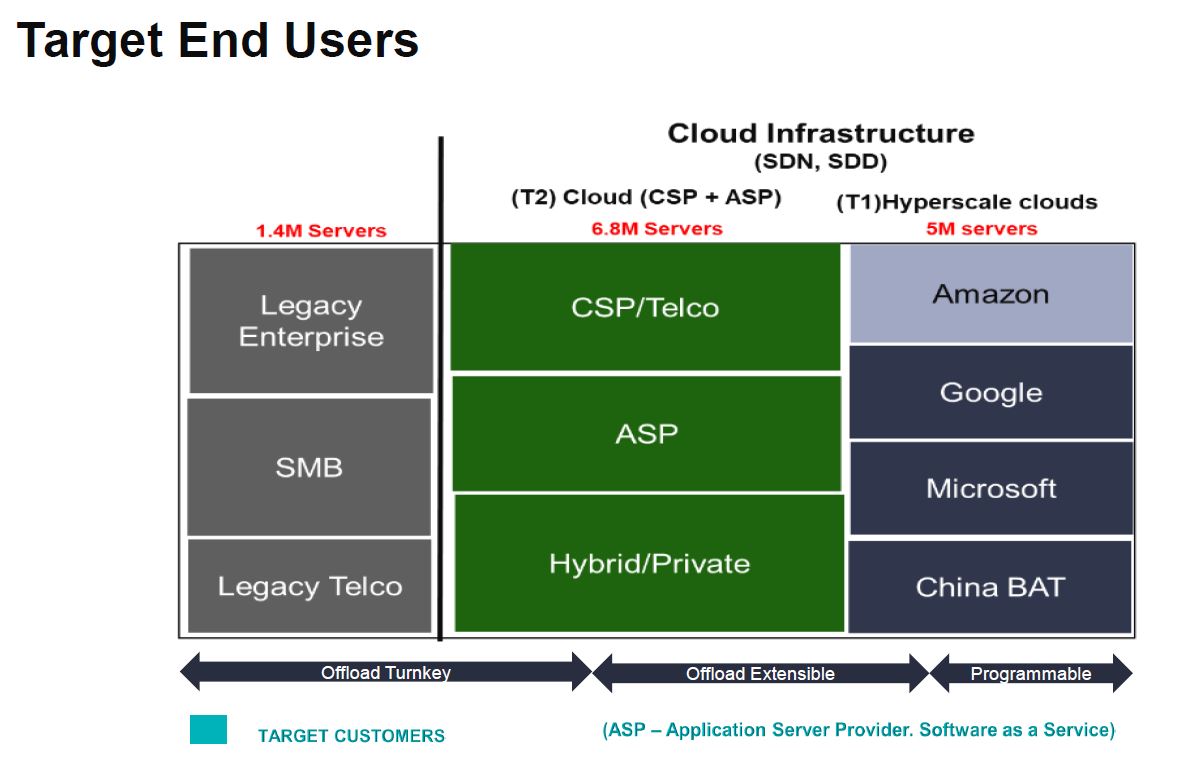

The company thinks this is a solution for perhaps not the largest hyper-scalers, but instead for the Tier 2 CSPs and some of the enterprise markets.

What you may notice along the bottom of this chart is “Offload Turnkey” which should raise an eyebrow.

Xilinx Alveo U25 Turnkey Solutions

While FPGAs are great for flexibility, and big cloud players can leverage that flexibility, sometimes all one wants is out-of-box performance. Xilinx plans to have a number of turnkey accelerators. The first is for Open vSwitch (OVS) offload and acceleration that it says offloads 90% of the overhead and improves throughput by 5X.

Xilinx is not stopping there. It sounds like IPsec offload and acceleration will be the next turnkey solution. There will also be out-of-box acceleration solutions for SSL/TLS, AES-256/128, distributed firewall, and AI inference acceleration in the future as Xilinx releases those solutions.

Final Words

A new SmartNIC is a big deal in the industry, especially in segments where Solarflare-based Onload is coveted. Perhaps the biggest part of this announcement goes beyond the Alveo U25 (which is exciting in its own right.) Two years ago one would purchase a Xilinx FPGA, design a PCB for it, design logic to run on that PCB, and put it in your product. The U25’s model is Xilinx will make a standard PCIe card you can plug into a standard server, and will have multiple out-of-box accelerated solutions that one can purchase without needing to program the FPGA. From a business model perspective, this is absolutely a game-changer for Xilinx making their products more accessible as one can get the benefits without needing to do the design work.

We did not get pricing information but expect these will be coming out in the next few months.

Xilinx is making a FPGA you can actually plug in and use? Do tell. Only took them decades

Review now.

Having worked with and programmed Servernet, been part of the IBTA during the 1.0 and 1.1 days, and being quite familiar with RDMA, I am not convinced “onload” is a good direction. I would like to see a good comparison of the performance and security trade offs between the technologies.

I understand the application of the FPGA to network processing.

OTOH this card puts compute in the form of the FPGA very very close to the network, so is this thing also useful as a compute accellerator? Otherwise why give it so much high performance memory.

Am I out to lunch here?

North,

Terible assumptions are made by traders to the surety of premature baldness if you still have hair, mine preemptively revised itself upon the NT3.1graphics driver kernel installation and sends postcards ever more rarely incredible volume is driven by buddies in penthouses paying consulting fees like two New Russians

@emerth I would think Xilinx went with fast onboard memory so it can access domain tables (ip address and stuff) as quickly as possible. Speed and efficacy are the name of the game. Also I’m sure there are other factors but regardless I would think with ddr4 is the “lowest ram” standard actively in use it would not make since to use anything slower cost wise. The cost different between 6 gigs of ddr3 and ddr4 is not much.

@Fob, thanks!