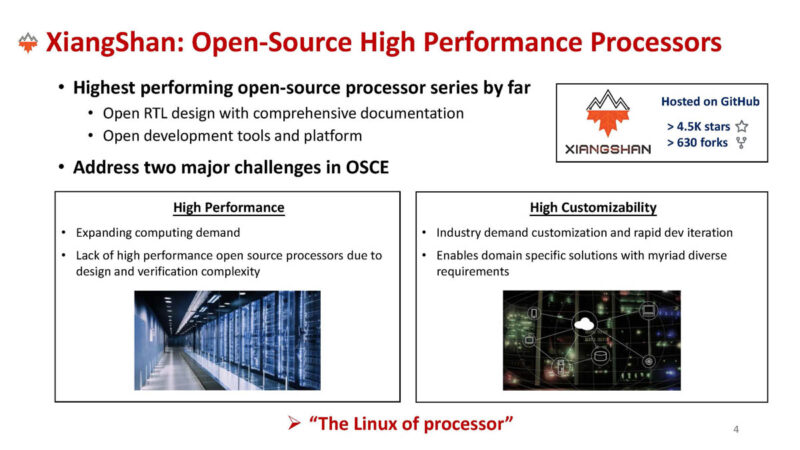

XiangShan is a RISC-V CPU project out of China, and now hosted on Github. This is a high-performance CPU design, instead of lower performance designs that we have seen from others.

Please note that we are doing these live at Hot Chips 2024 this week, so please excuse typos.

The chip project is a RISC-V project run by folks at Chinese universities.

XiangShan High-Performance RISC-V Processors at Hot Chips 2024

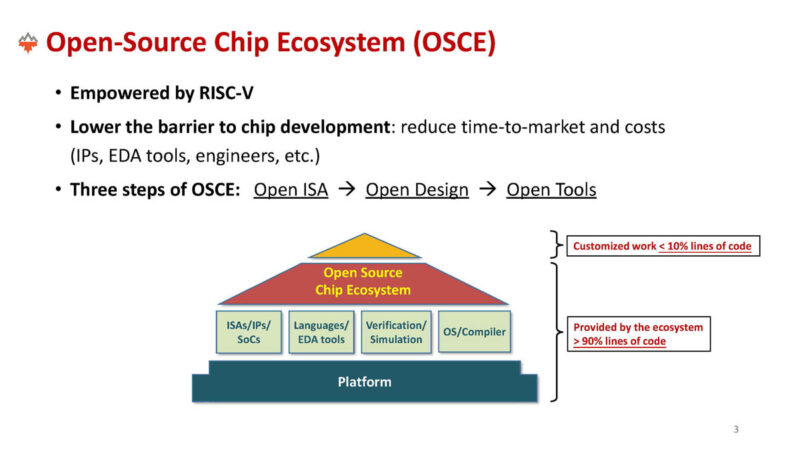

The vision is that this is a RISC-V architecture with open tools and designs.

This is also designed as a high-performance rather than a low-performance core.

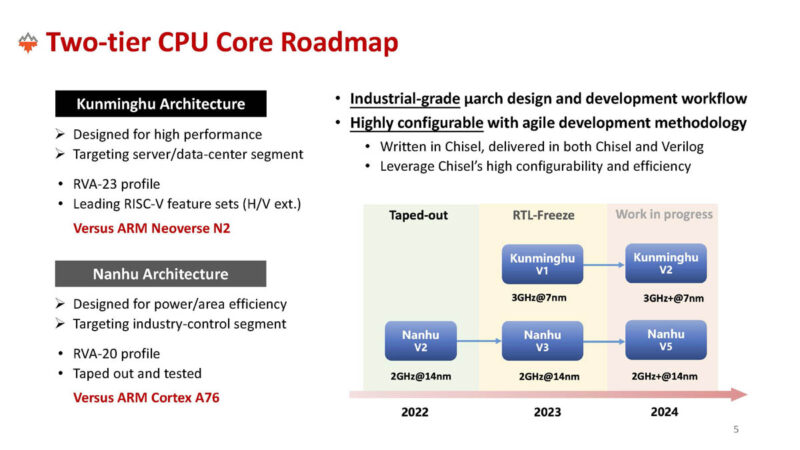

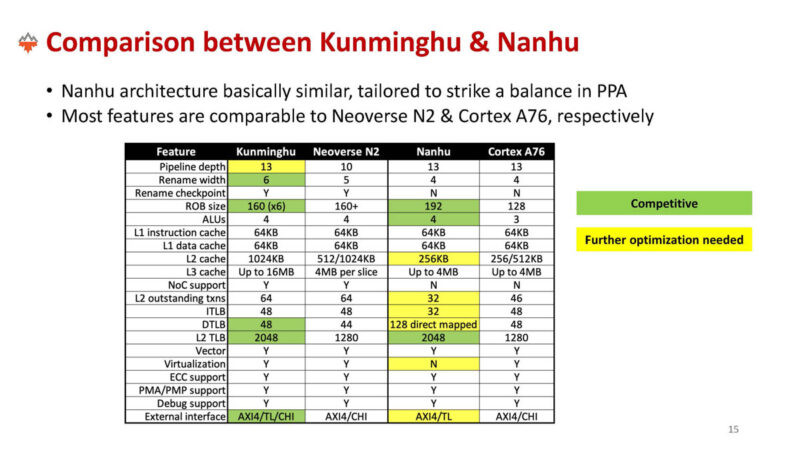

XianShan is targeting the Arm Neoverse N2 with Kunminghu and the Arm Cortex A76 with the Nanhu line, and these are being built.

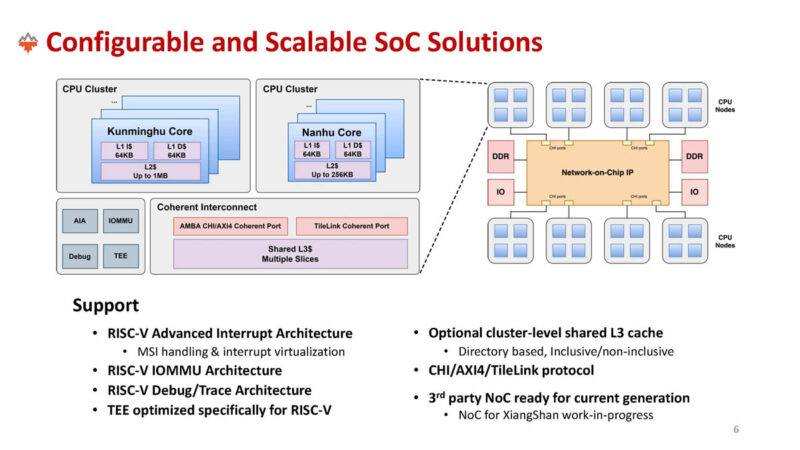

In addition to cores, the goal is to allow for larger clusters for higher-performance chips. That also includes integrating both the Kunminghu and Nanhu core. The project also includes the coherent interconnect and other parts of the left side of the diagram.

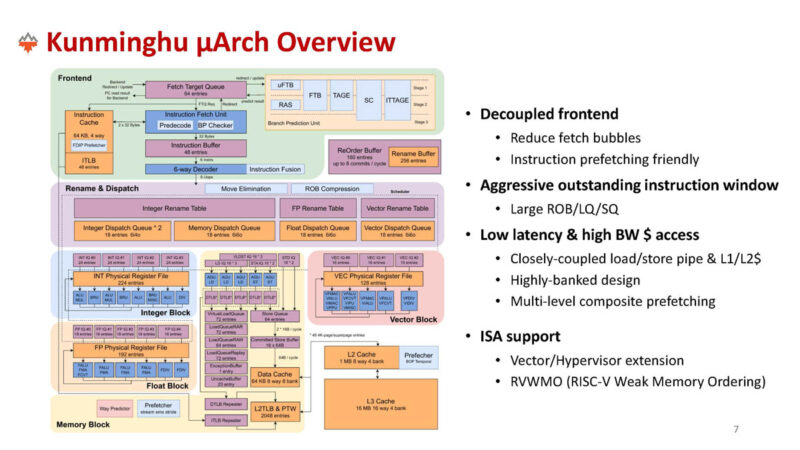

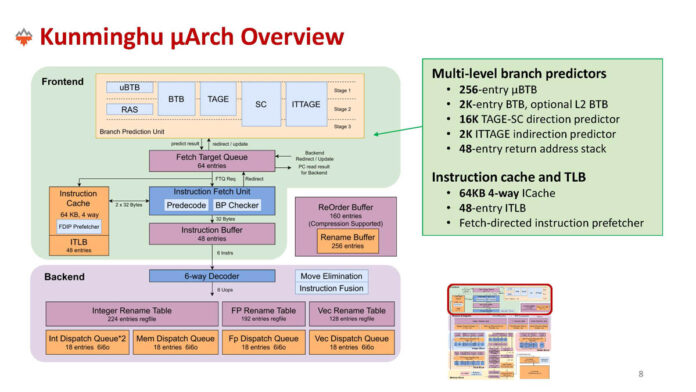

Here is a look at the Kunminghu microarchitecture. This includes vector and hypervisor extensions.

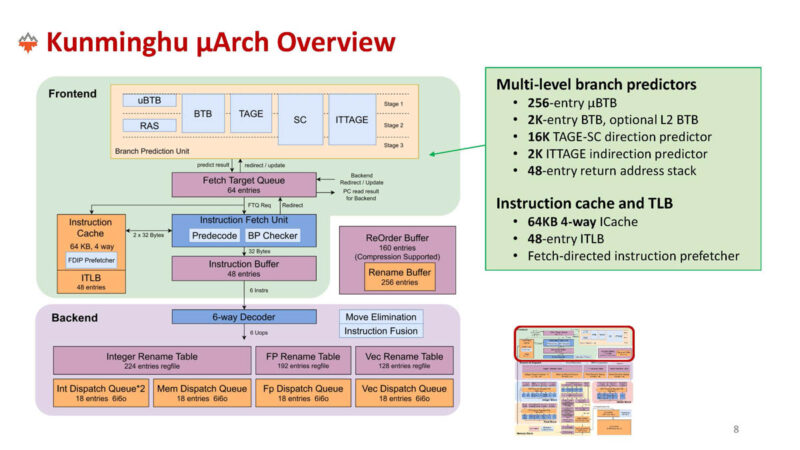

Here is a look at the branch predictors and the instruction code/ TLB on the frontend.

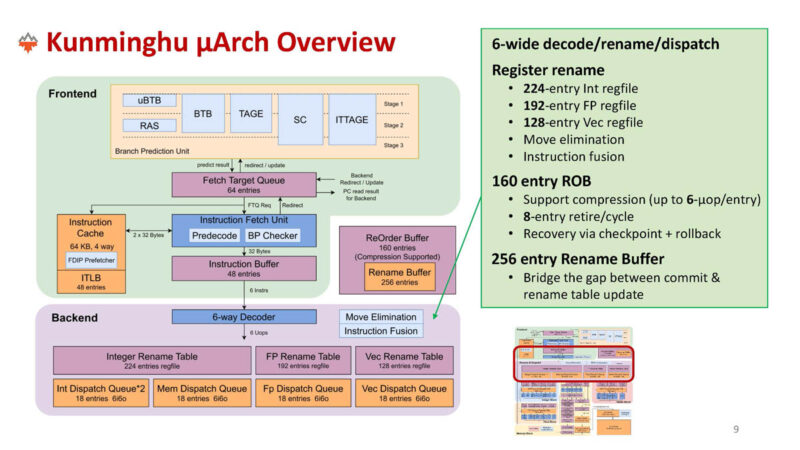

There is a 6-wide decode/ rename/ dispatch on the backend.

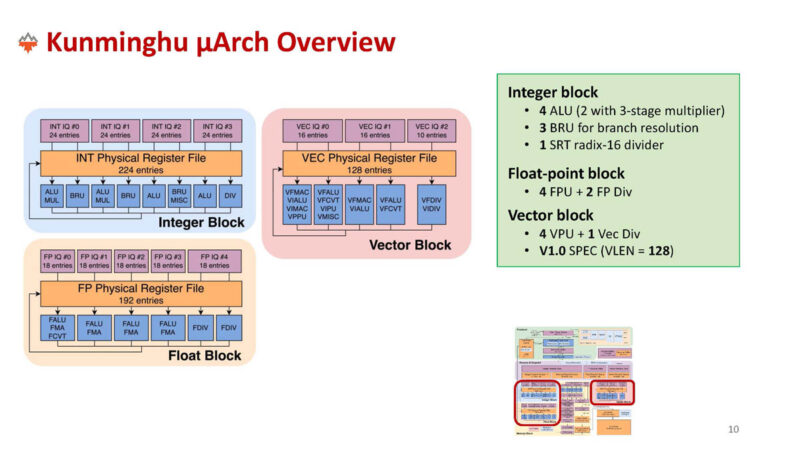

The integer block is a 4 ALU design and the design also has floating point and vector blocks as well.

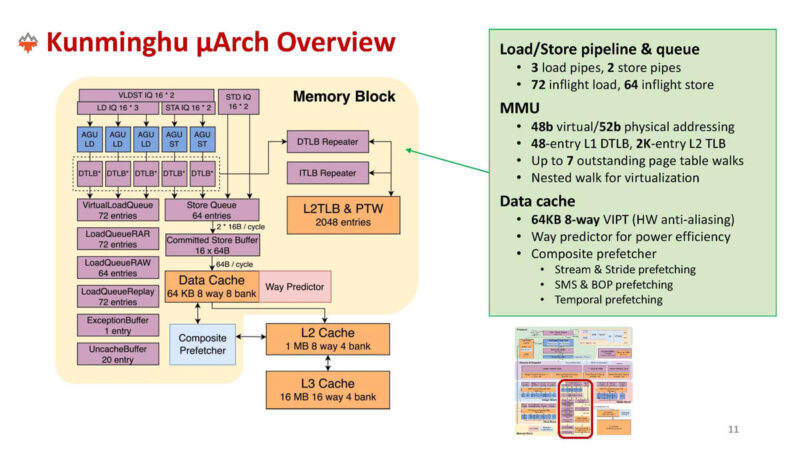

Here is a look at the memory block with the load-store pipeline, MMU, and data cache.

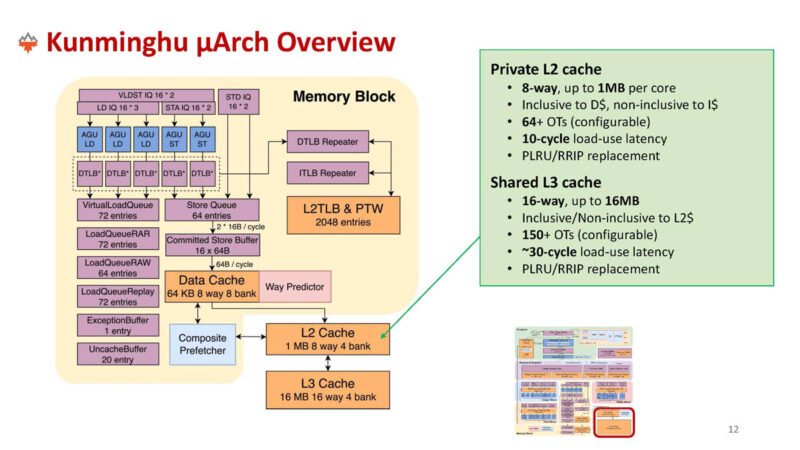

Cores have private L2 caches up to 1MB and there is a shared L3 cache. 16MB shared L3 may look small compared to modern large server CPU designs, it is fairly good if you think in terms of a Neoverse N2 device.

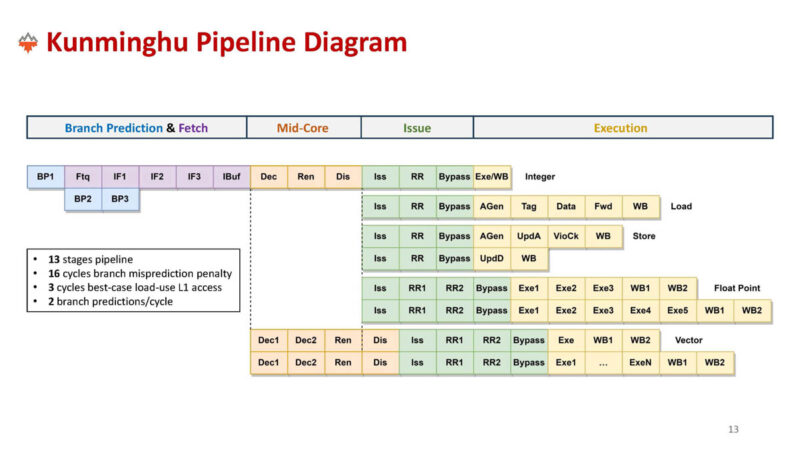

Here is the pipeline diagram across the 13 stage pipeline.

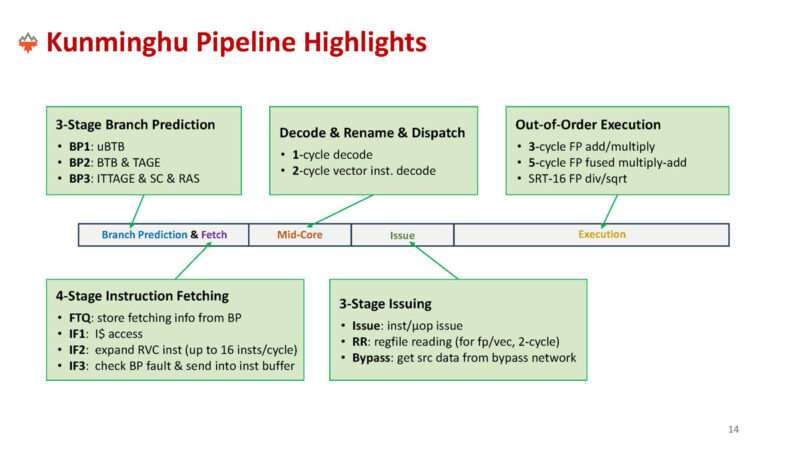

Here are some of the highlights that we will let you read through.

Here is a look at the Kunminghu and Nanhu versus the Arm Neoverse N2 and Arm Cortex A76.

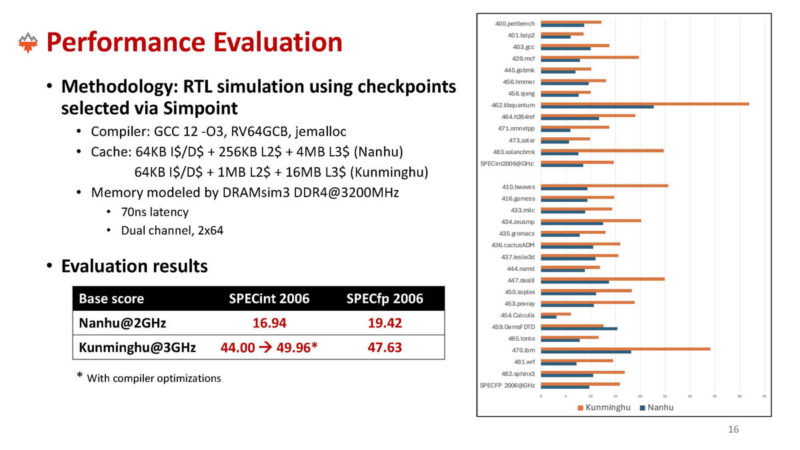

In terms of performance, SPEC CPU2006 is a bit older, but it is fairly well-known.

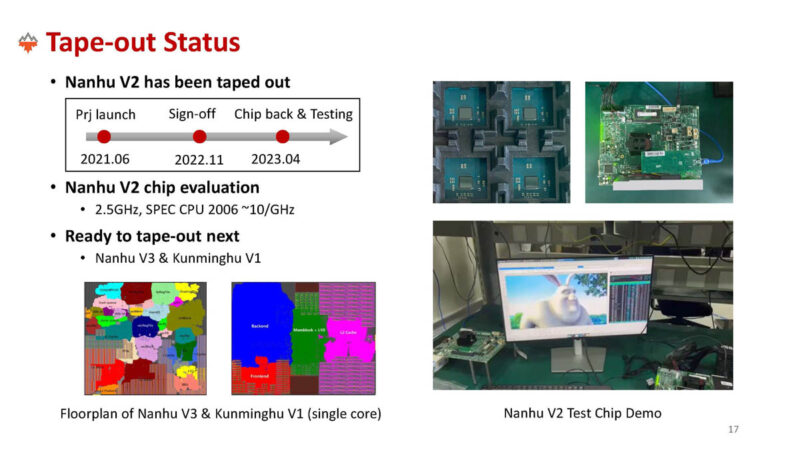

Here is a real chip, board, and a real video running on the chip.

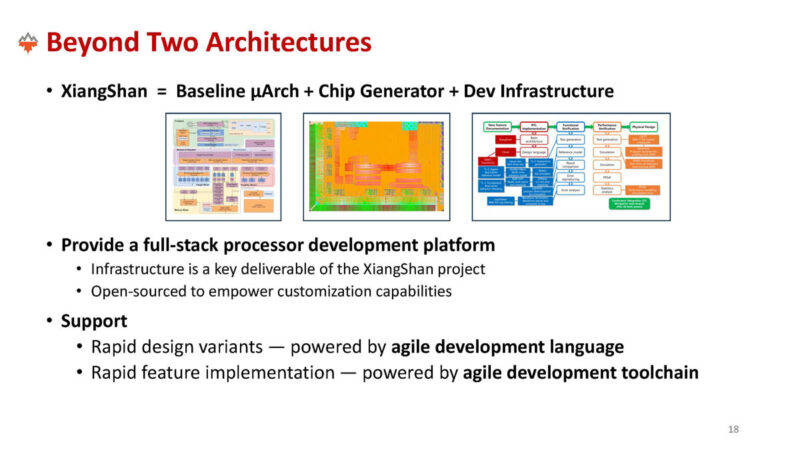

Beyond the first two architectures, there are additional open source tools going along with the initial designs.

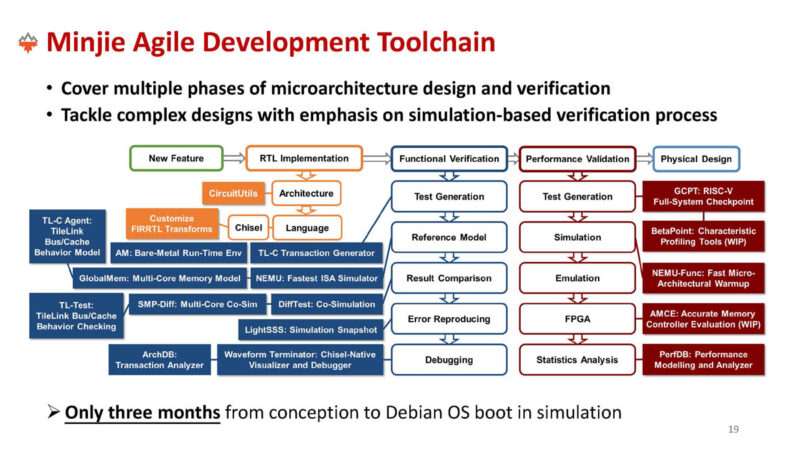

Minjie is the agile development toolchain being used.

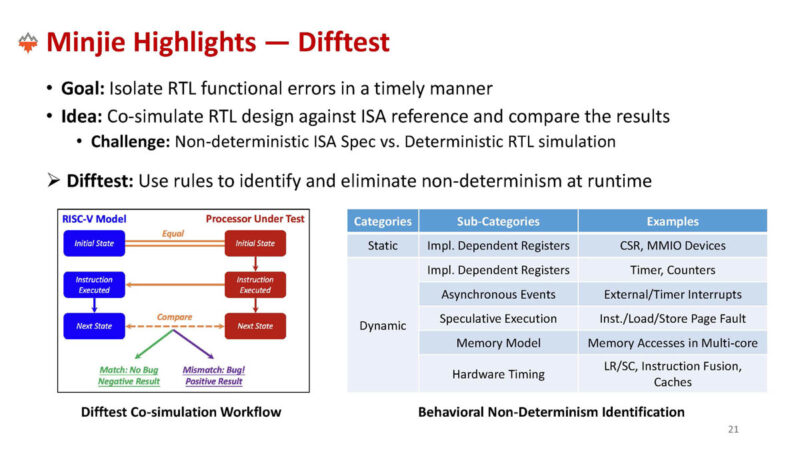

Here is a look at the difftest, which is used to find the RTL errors in a timely manner.

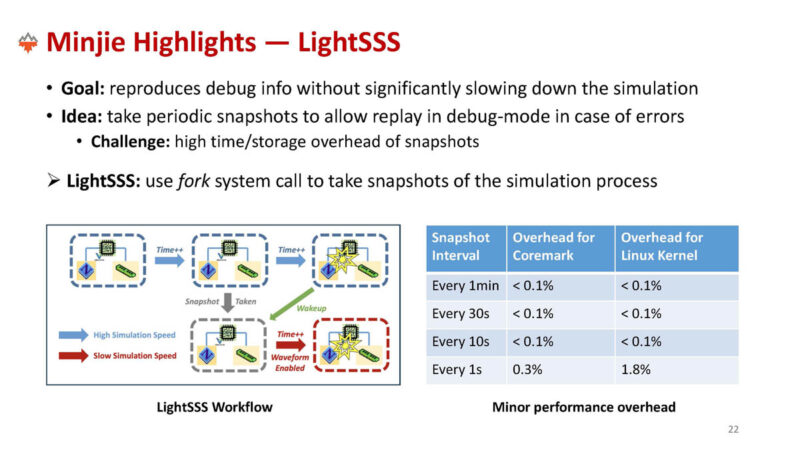

There is also LightSSS, which reproduces debug information in simulation. These are not things that end users would normally run. Instead, these tools help build usable chips through testing before going to fabs.

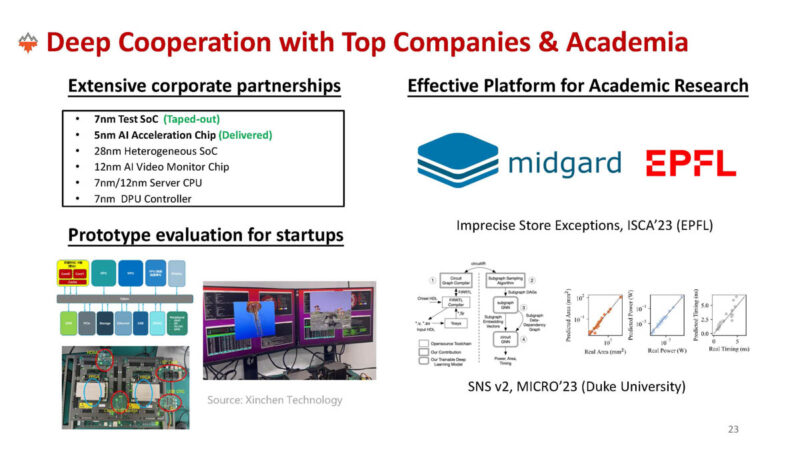

Here are some of the highlighted collaborations, including for a server CPU, a 5nm AI acceleration chip, and a 7nm DPU.

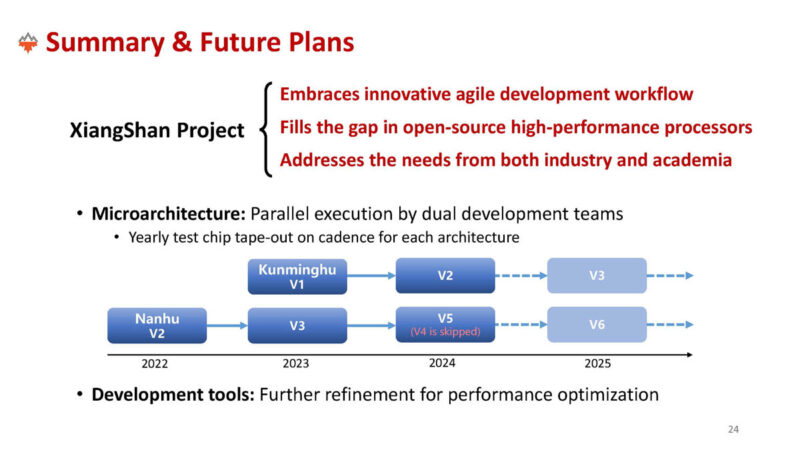

Here is the summary and some of the roadmap.

With two teams running in parallel, the project hopes to keep creating new designs and tape out a new chip every year.

Final Words

It is cool to see what is essentially two RISC-V projects out of China directly targeting the performance and product segments of two Arm CPUs. We often see customized RISC-V designs, but these are more general-purpose chips.

open source is good but can be bad when others use it for its own good

Closed source is bad but can be good when others use it for its own bad.