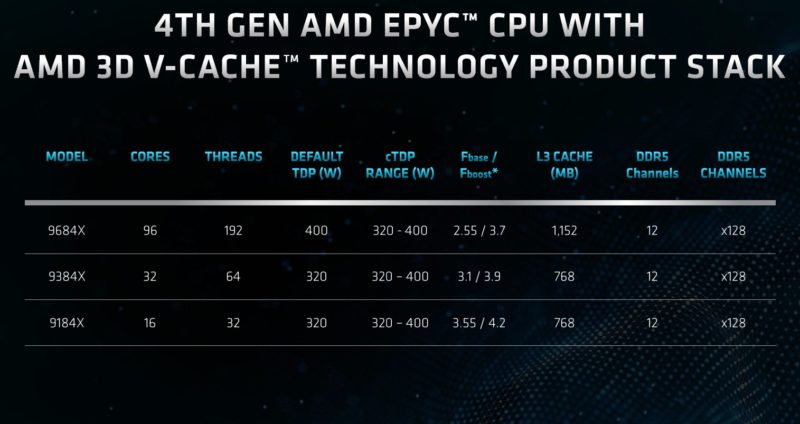

AMD has three new SKUs as part of its newest high-cache chip lineup. What might surprise our readers is the core counts as AMD is going after two very different markets with the new AMD Genoa-X series. While many may expect a 96 cores 1.1GB of L3 cache behemoth, others may not be expecting a part with 48MB of L3 cache.

AMD EPYC Genoa-X SKU List

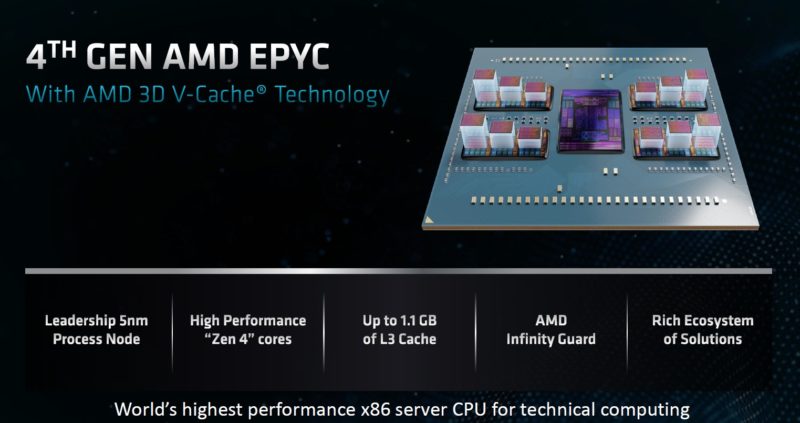

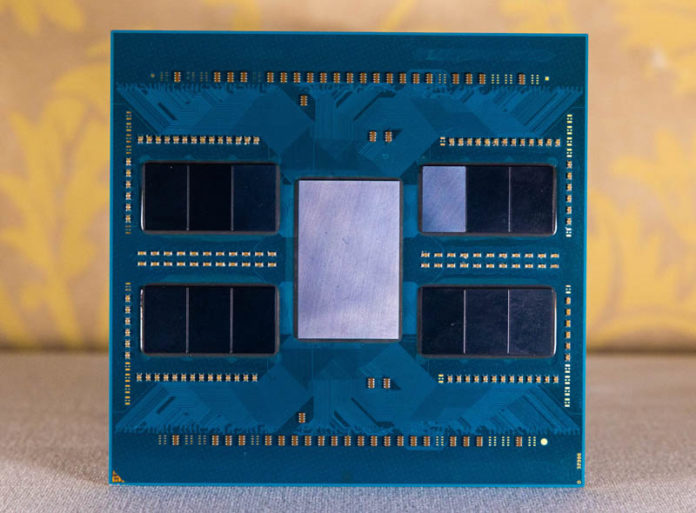

Still built around the same Zen 4 architecture that we saw with the original AMD EPYC Genoa, the new chips add 3D V-Cache. For folks wondering, this is very much in line with the AMD EPYC Milan-X.

The high-end 12x CCD version is the AMD EPYC 9684X at $14,756 list price. This 96-core chip has 1152MB of L3 cache which may even not be the craziest.

AMD also has two chips, seemingly made for per-core licensing (e.g. 16 cores for Windows Server and 32 cores for VMware.) The AMD EPYC 9384X is a 32-core part with 768MB of L3 cache at $5529. Perhaps the crazier one is the AMD EPYC 9184X which has the same 768MB of L3 cache for a total of 48MB of L3 cache per core. The $4928 list price of that part may seem like a lot, but if you are optimizing on per-core performance, that extra L3 cache can have a huge dollar impact.

Final Words

AMD has a strategy where it now has three server CPU lines in the same socket. The mainstream Genoa, the high-core count, Bergamo, and the high-cache Genoa-X. As we have mentioned previously, the big win will be a future part combining reduced base-die cache / high core count chips with L3 cache stacked. We think it is at least a generation away, but Bergamo-Next-X is going to be a fascinating part.

As you would expect, we will have a full review with benchmarks when the embargo lifts.

“The AMD EPYC 9384X is a 32-core part with 768GB of L3 cache”

768GB of cache per CPU is certainly very, very impressive! (and quite likely should have the G replaced with an M)

I’ve been curious about this since AMD first launched the -X lineup:

What would application performance look like if they stacked HBM memory (maybe even not a full stack) on top of the IO die. Whether that replaces the L3 cache or is an L4 cache.

Think bigger. What about a MI300 variant with only CPU Chiplets.

Could be a 96 Core 3D CPU with 196GB HBM and Infinity LLC in Base Chiplets.

Compatible with Genoa Socket.

Sorry, 192 GB HBM Like MI300X.

How long before we see Genoa/Bergamo X3D variants using 3DVcache like their desktop counterparts, or are those already out?

DUHHH, if only I had paid closer attention to the slides in the article I would have seen that THESE here ARE the 3D V-cache variants of Genoa. DUHHHH. I’m stupid. I’ll go back to work now.

Is it known how the cores are distributed on the low core count/high cache models?

Can cache be stacked on a CCD with no live cores; and the part be just 2-4 8 core CCDs with the rest just doing cache? Does every CCD need at least one live core in order to stack cache on it; with the parts being fully loaded with CCDs that have almost all their cores disabled?

I would love to be able to run an OS in the L3 cache without any RAM, although I know it’s not possible and would probably be very much pointless. But it would be really cool.

The 9184X part is very interesting not just because of the massive amount of L3 cache per core but also the relatively high clocks for a server part. Per core performance should be very, very good here.

What is still missing are the 24 and 48 core variants with 1152 MB of L3 cache. AMD is heavily focused on parts with 8 CCD instead of the 12 CCD design used for the 96 core parts. Pretty much if you have 12 CCD’s you have either an 84 core or 96 core part.

So in Genoa 16 core land (for those of us stuck with Windows Server), options are now:

Model speeds TDP MSRP

9124 3.00/3.70 200W $1,083

9174F 4.1 /4.40 320W $3,850

9184X 3.55/4.2 320W $4,928

Reference Zen 3 Threadripper for clocks:

5955WX 4.0/4.5 280W ~$1,100 street

@Uwe – then package it as a SOC, no RAM required!