At STH, we rarely cover earnings releases, but after listening to the Intel Q4 2020 earnings call, I thought it may be prudent to discuss a few parts. Earnings announcements and summaries are laboriously crafted. As a result, they carry specific messages both in what they discuss, and what they omit. We wanted to discuss a few key messages from this week’s announcement.

The Quick Intel Q4 2020 Summary

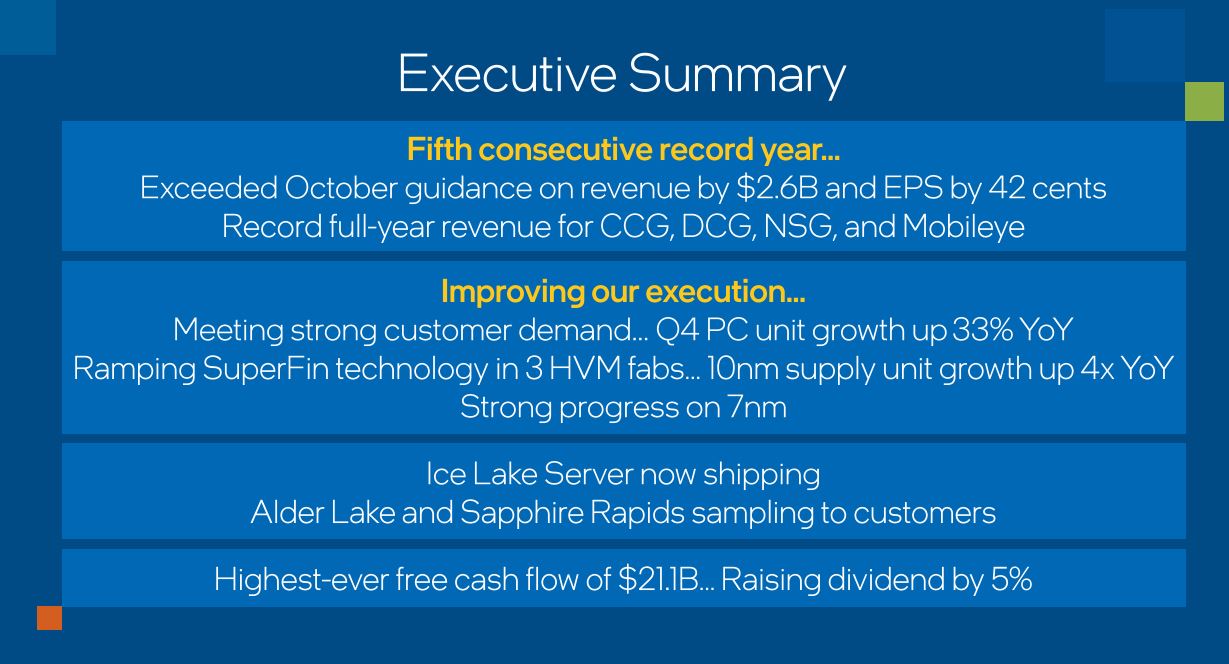

First off, reports of Intel “dying” is a bit exaggerated at this point. In terms of a business, Intel is still making money and a lot of it. Intel’s management tone has certainly incorporated the notion that there is room for improvement, but increasing revenue and earnings also means Intel has resources. It is better to have resources when you need to pivot a company than not have them.

Intel mentioned Ice Lake is “shipping”. This is likely D1 stepping Ice Lake, not “retail” D2 stepping if they are discussing meaningful quantity. Perhaps the most fascinating part of this slide is not what is on the slide even with Sapphire Rapids, Ice Lake, Habana Goya2, and Xe GPUs on there. Instead, one may ask, where are the FPGAs? That was billed as a growth center when the acquisition was announced. Given Q4 had the AMD to Acquire Xilinx news, it is notable that FPGAs did not make the “Our Priorities” slide. FPGAs are leading 10nm parts and one of Intel’s main rivals is making a big bet in the space, yet FPGAs are not a priority for Intel. Around the time of the Altera deal’s announcement, Altera was around $2B in revenue, and it is perhaps Intel’s best XPU story currently.

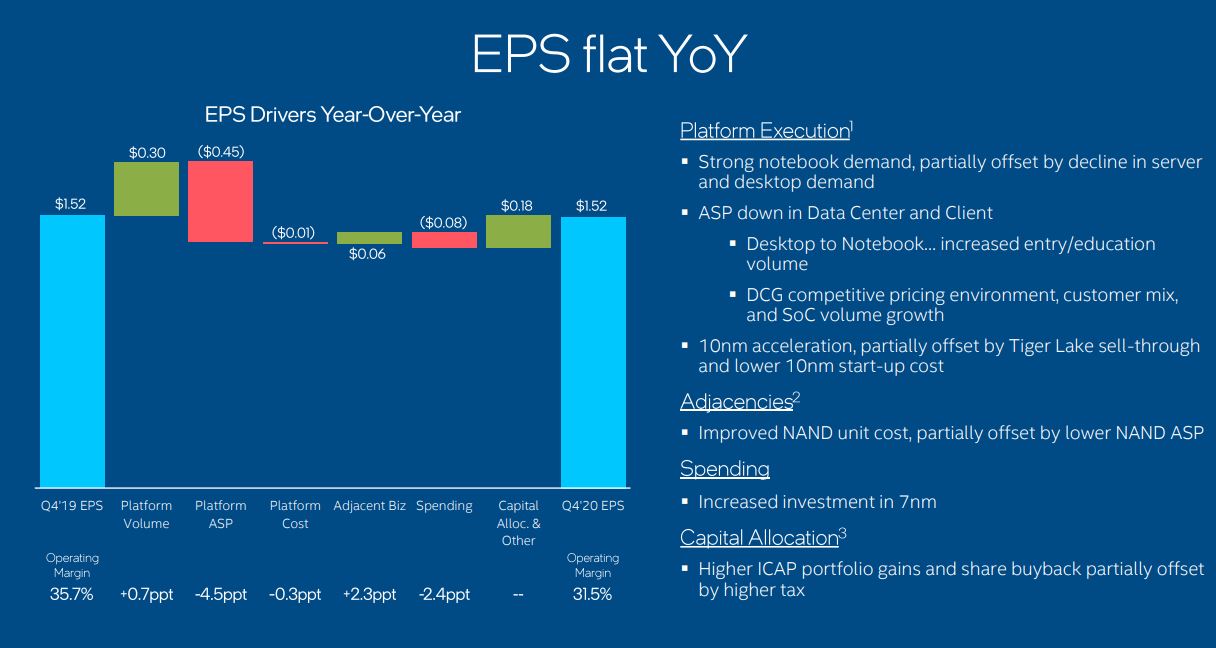

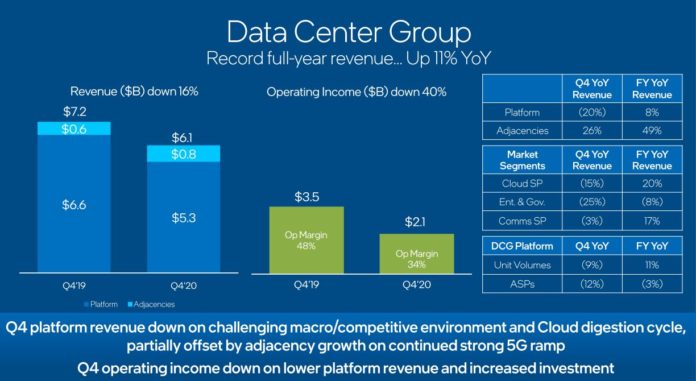

On the EPS waterfall, the note is are interesting. We see “DCG competitive pricing environment.” AMD, and cloud providers that are now building Arm CPUs are ratcheting up competition for Intel. This was not the case only a few years ago.

ASPs (average selling prices) declining in DCG is only part of the story since unit volumes are down too. Let us get to some notes from the call.

Cloud “Digestion” or Indigestion?

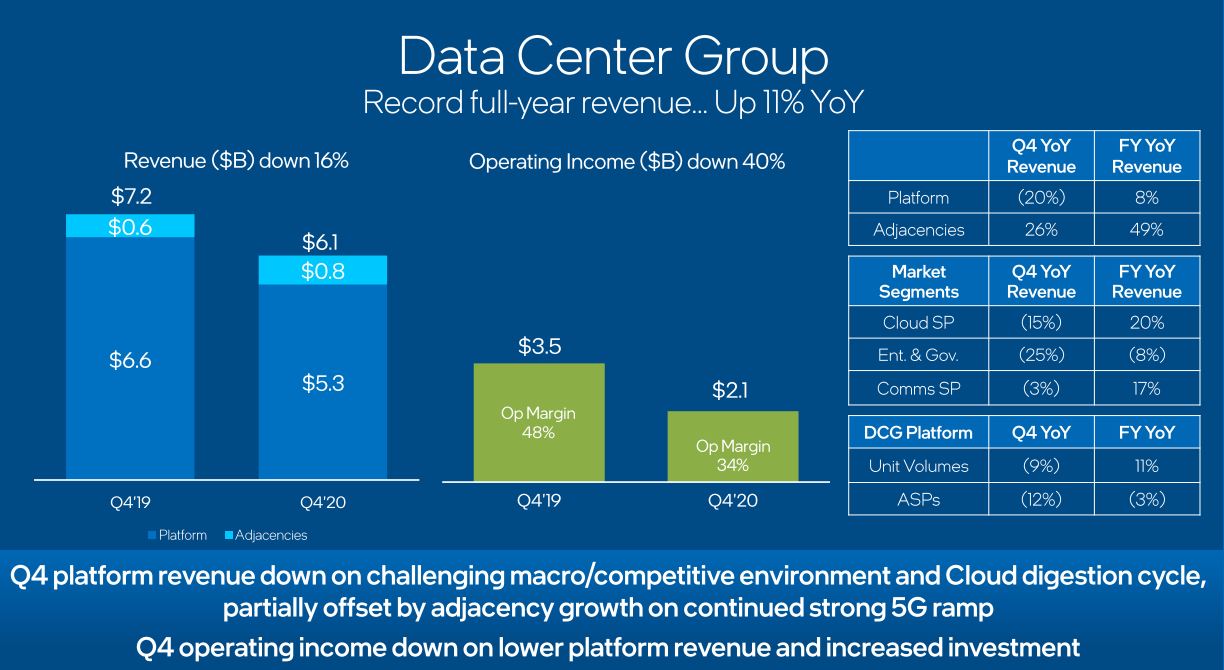

First, cloud customer “digestion” is an interesting concept. Intel said that part of the Q4 cloud segment softness was due to customers digesting purchases from earlier in the year. We know that cloud customers are buying AMD EPYC Milan. Ice Lake is headed to clouds as well. Also, cloud service providers had excellent growth in 2020 due to shifts in the market. As more folks were staying home, IT and data centers served as the virtual offices and even trade shows.

Cloud providers continued healthy growth in 2020. We would expect that more revenue is driven by more consumption whether that is a bare instance or a platform delivered on infrastructure. Spending several quarters in a “digestion” cycle seems odd. The cloud market is concentrated into a small enough customer base that the major players all having a similar built out is not good for the industry. Many of the hardware providers that are making servers operate in the low single digit percent margin range. Having all providers build-out/ update at the same time, then effectively stop would be terrible for their business.

The term “digestion” may have a different meaning here. Our sense is that it likely means that the cloud providers knew Ice Lake was coming, and slowed purchases for the new hardware. After-all, if you are Amazon AWS and want to have a new instance type, you likey would plan that instance type to coincide with a new chip being deployed. Perhaps “digestion” means that customers continued to purchase additional capacity based on needs for existing instances, but did not turn lifecycles with a new architecture as they waited for the 10nm Ice Lake ramp. If that was the case, then maybe the better term is “indigestion” or fasting before a feast.

Intel saw revenue up 11% Y/Y while top cloud providers saw revenue up in the 30-40% range Y/Y. Assuming these cloud providers purchased more than they needed earlier in 2020, and were still working through it, it seems like we would have seen higher than 11% increases. Instead, it seems like Intel is feeling pressure from competitive sources (AMD) or competitive customers (Arm designs by cloud providers such as AWS Graviton2) or both. Unit volumes seem like they were down less than ASPs which means Intel is giving more discounts to sell its product in a more competitive market.

For those STH readers who are non-native English speakers, terms like these are used often to obfuscate or to avoid describing the actual condition.

Intel 7nm Update

One of the interesting parts of the earnings call was that Intel pushed a plan for 7nm and also discussed a 2023 roadmap. They said that the team had been doing work since the July earnings call, which prompted our The 2021 Intel Ice Pickle How 2021 Will be Crunch Time article. In the end, they have been working on not just improving yield on 10nm parts but also 7nm.

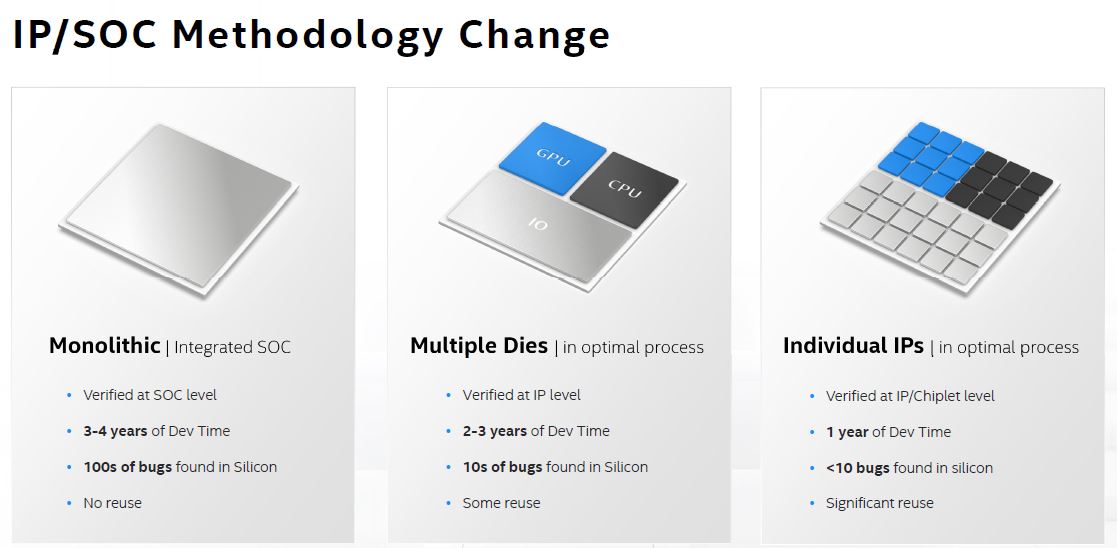

A valid question was posed on whether Intel would be competitive at 7nm. TSMC will be starting to move from the 5nm it is employing now and onto 3nm. Intel’s direction was that they think it is important that Intel not only gets back to parity but also gets back to the leading manufacturing process. When 14nm was launched, Intel was ahead of the pack with the Intel Xeon E5-2600 V4 launch in 2016. Now, Intel is behind due to its 10nm delays. 14nm may have been improved, but a 5-year 14nm product cycle is extremely long. What had financial analysts worried was that not only was 10nm slipping, but 7nm was as well. It seems like 7nm is being de-risked from a production standpoint and also through using other foundry partners. Intel even discussed future chips in terms of “tiles”. For those that may remember our SoC Containerization A Future Intel Methodology piece, Intel is looking at tiles:

Effectively, this allows Intel to build tiles on chiplets on the best foundry and then integrate them into products. This is our sense of how Intel is looking at its future roadmap with internal/ external fabs. The future “Individual IPs” is a next generation of how AMD is building chips today such as its EPYC CPUs where chiplets from multiple fabs with different functions are integrated onto a single package. Again, Intel is looking at something more advanced, but this is more lower-risk chiplet and less high-risk monolithic die. Ice Lake Xeons may be better than EPYC Rome, but EPYC Rome is going to be out around six quarters before Ice Lake largely due to this strategy.

A Jab at AMD?

Something that I noted a few times on the call was the emphasis on having the internal manufacturing capacity to deliver chips that customers want. My initial reaction is that this is a jab at AMD.

More than a few times over the past month or two I have heard folks, non-specifically quip “if AMD could make more CPUs” or “if AMD had CPUs” or some version of that. After the third or fourth party that says that in different contexts, one gets the sense that AMD may be capacity constrained.

If we look at the Zen 3 desktop segment with the Ryzen 5000 series we see not a lot of stock around, and the same is true for its GPUs. AMD EPYC had a subtle marketing message shift in 2020. At AMD Financial Analyst Day 2020, the company said it would be shipping the EPYC 7003 “Milan” series in 2020.

By SC20, we got the update that volume shipping would happen in Q4 2020 with a launch in Q1 2021.

We know that AMD EPYC “Milan” was in-production at least by September 2020 for major cloud customers and not in the engineering sample markings.

So what we have as data points:

- AMD is shipping Zen 3 both desktop and server

- The desktop chips are in tight supply

- AMD’s new GPUs, also built on TSMC are in tight supply, so it is not just an architecture-based supply constraint

- Cloud customers are getting non-ES Milan

- We have heard vendors quip that EPYC CPUs are in such demand that supply is tight

- Intel on its earnings release is making statements that its internal plus external fabs can supply the volume customers need

On that last item, when you see Xeon unit volume dive, it does not seem like that is talking about its own 14nm server CPU production. We know Intel can make 14nm Xeons at higher quantities.

This was not explicitly stated, but if you are in the industry, my initial reaction was that these comments were a jab at AMD having products the market demanded but being supply-constrained.

Time will tell perhaps on the next AMD conference call. It would be a major change of tone for Intel to highlight that its competitor has products that the market has demand for that outpaces supply.

Final Words

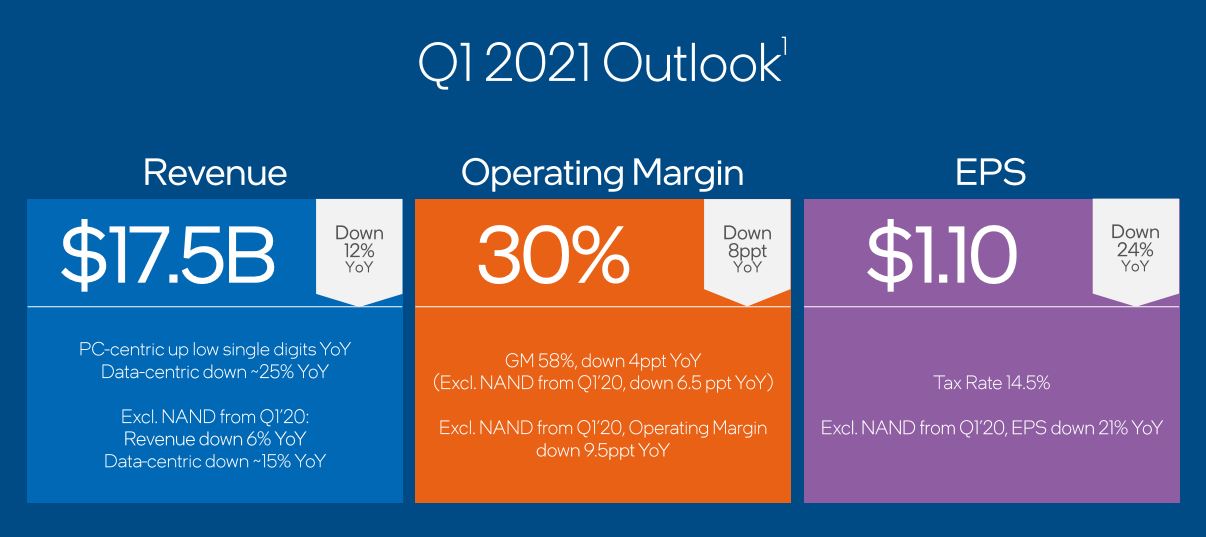

We are now a few weeks into the quarter and guidance is clearly down. Data-centric being down 25% / 15% Y/Y (excluding NAND that is being sold to SK hynix) is not a great outlook.

To us, this looks more like guidance we would expect if Ice Lake Xeons and the Xeon-based PCIe Gen4 ecosystem uplift was about to happen, but not yet hitting in Q4. Cloud providers will likely continue to grow this quarter so continued weakness means Intel is not selling new chips, in huge volumes, at large premiums.

Still, we need to take a step back, and this is part of why Intel is a diversified, and diversifying business. Intel has moved from its CPU strategy of having 97%+ of a smaller CPU market to its XPU strategy where having a smaller share in more silicon processor markets helps when a part of the business is challenged. From an anti-trust perspective, Intel likely would prefer to be 50% of dozens of markets than 97%+ of the server/ desktop CPU markets. Technology is one part of the equation, but Intel as a company has a duty to its shareholders, and often that brings broader considerations into play. Intel needs to execute and that is why bringing in Pat Gelsinger as CEO may just be the right catalyst for change.

2021 is set to be a fascinating year in the server space. You can read more about it in The 2021 Intel Ice Pickle How 2021 Will be Crunch Time.

Does anyone know why Intel keeps calling Ice Lake 3rd gen Intel Xeon Scalable processor? Cooper Lake was 3rd gen.

> it is notable that FPGAs did not make the “Our Priorities” slide.

This is a good point, and worrisome. Intel has hinted at big FPGA opportunities for a while and we’ve seen nothing, unless I missed it. An outside observer would think there would be opportunities in radio, Xeon coprocessors and even Atom wireless/embedded markets.

Intel has historically tied their cell libraries tightly to their design needs. I worry that as intel ports designs, their in-house fab advantage will diminish if designs are generalized. Maybe it will be a net positive, but fab processes tightly coupled to design goals seems like a substantial competitive advantage in a world with few leading node fabs.

FPGA is a tough market.

A $150 Basys-3 dev board is the best thing to happen to hobby electronics since the Aduino, it’s like owning the factory in Maynard, MA where DEC made minicomputers.

With a $7500 dev board you can make cutting edge systems for networking, signal processing, even XML parsing. Trouble is that $7500 FPGA does the job of a $75 ASIC and somewhere between 1,000 and 10,000 units it is worth going to a foundry and making an ASIC.

The FPGA market is some small number of chips per applications times a small number of applications because FPGA development is still a hassle compared to CPU, GPU, DSP and such — for specialized functions where an FPGA could destroy alteratives in performance it may well be limited by memory bandwidth which is at best going to be the same as a mainstream system.

I went with Xilinix because it seemed easy to get started with, but if Intel greased the skids from beginner to “fab ASIC profitably in 1/10 the time and cost” then that would move the needle for what people can do with electronics. The U.S. Military is very interested in that sort of things because it thinks it spends too much on FPGA.

@chris.london I think Intel prefers to pretend Cooper Lake never existed (for the majority of people)

@ssnseawolf

> Intel has historically tied their cell libraries tightly to their design needs. I worry that as intel ports designs, their in-house fab advantage will diminish if designs are generalized. Maybe it will be a net positive, but fab processes tightly coupled to design goals seems like a substantial competitive advantage in a world with few leading node fabs.

I think you have it backwards here; it seems to have been more the case that Intel design goals were tightly coupled to fab processes. That produced what they produced and design just figured out what they could make work, hence (one of the reasons) why custom foundry floundered and Altera struggled for a while.

I think you missed some details by just looking at the presentation and not listening to the call:

“We will qualify Alder Lake desktop and notebook for production and begin our volume ramp in the second half of 2021 and we expect production qualification of Sapphire Rapids at the end of 2021.”

So they are not even really expecting “Initial production shipments” of Sapphire Rapids in 2021 like you talked about before.

I listened to the call. Hopefully, the new Pat G regime will be more concise on how they communicate what stage each processor is in.

chris.london

Cooper Lake is 4-8 Sockets and is 3rd Gen

Ice Lake SP is 1-2 Sockets and is also 3rd Gen

Sapphire Rapids will cover 1-8 sockets with a single arch.