The Oracle Sonoma platform is targeted at brining a high-level of feature integration to a lower price point than previous generations. Recently, Oracle has focused its attention on x86 compute with the majority of systems supporting x86. It has been years since we have seen a lower-end SPARC refresh. Hyperscale vendors are actively looking for alternatives to Intel’s x86 processors, if just to give Intel some competition. Meanwhile, IBM, Oracle and others are looking at finding new avenues to sell more of their non-x86 chips. IBM’s OpenPower is a clear step in lowering the entry pricing for its systems to make them more attractive to hyperscale players. Oracle Sonoma is likewise a step towards lowering the costs of its processors as it showed at Hot Chips.

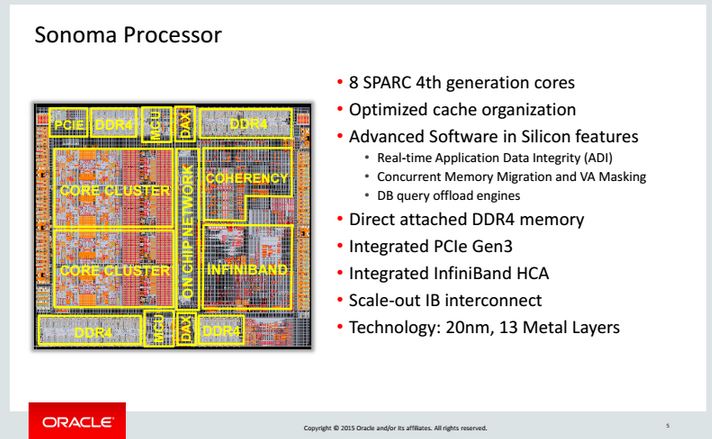

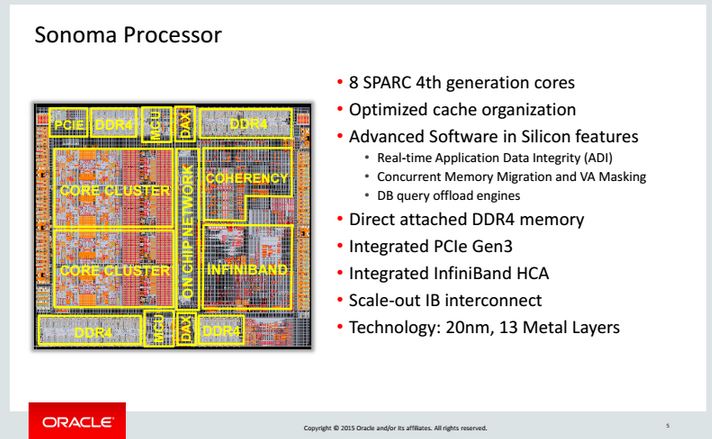

The die shot and map of the new chip is enough to give us an idea where Oracle is focusing. We see two core clusters each with four cores and associated cache. There is a huge amount of the die below marked as Infiniband. This generation of Oracle SPARC is going to have a focus on integration and interconnects.

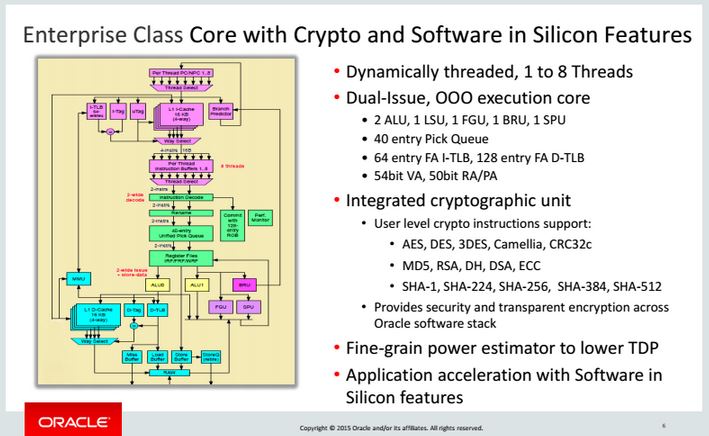

The next slide Oracle presented showed some of its key differentiators. Key here (aside from some of the great SPARC execution features) is the cryptographic acceleration. Gone are the days where it is considered “OK” to run a cloud or internal application with network and storage unencrypted inside your firewall. In today’s architectures everything is encrypted and having hardware crpyto has made that possible. Whereas (hardware supported) crypto used to be expensive six years ago, it is considered virtually free today.

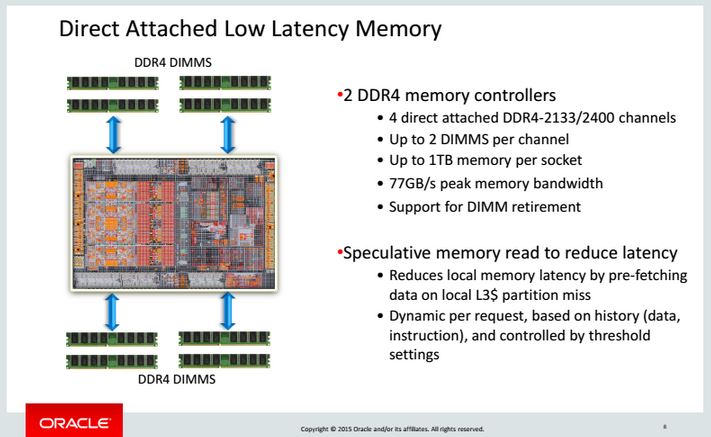

Since Oracle touts in-memory analytics, database caching and storage caching Oracle applications tend to be memory hungry. Feeding this one has an on die memory controller that can support up to 1TB per socket. Interesting here is that we see DDR4-2400 support, a speed which we will soon see as the replacement for DDR4-2133.

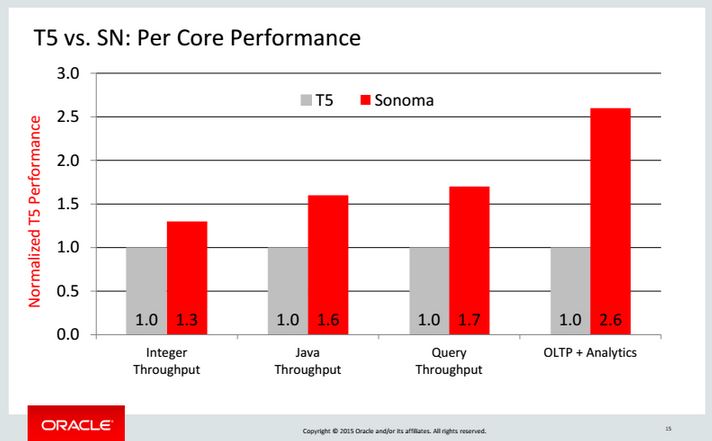

As with each new processor generation, the Sonoma chip is going to be faster than what we saw with the T5 released a few years ago.

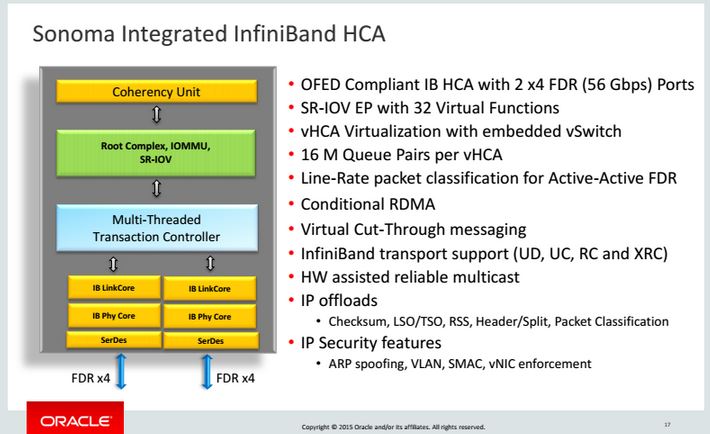

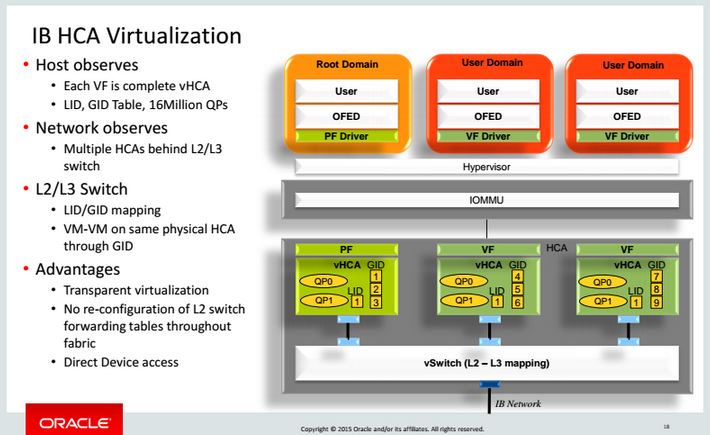

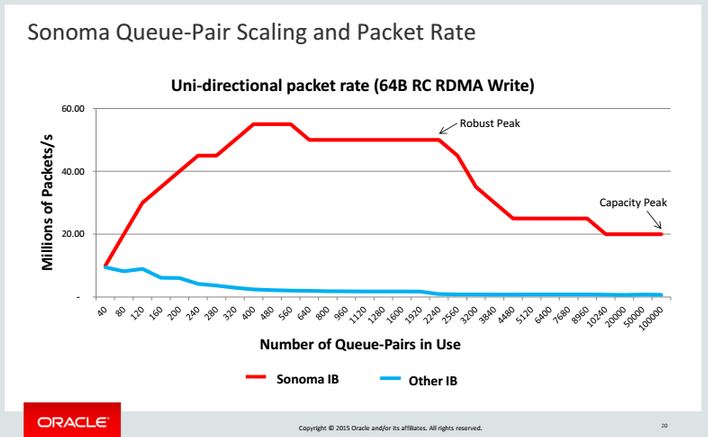

Probably the biggest trend we are seeing today is integration of the interconnect layer. We see low end SoC’s integrate networking, including most of the ARM vendors. Intel has integrated Ethernet networking with the low-end Xeon D-1500 series and even the older Atom C2000 series chips. We also see Intel offering integrated Omni-Path in Knights Landing and future 14nm Xeon E5 processors. Oracle is a major user of Infiniband so we see a dual port integrated FDR Infiniband controller on-die.

It is a bit interesting that Oracle is integrating FDR (56Gb) Infiniband given we are now seeing EDR (100Gb) Infiniband emerge. Still integration on die has a few major implications. One of those implications is that there will no longer be a need for external PCIe Infiniband cards which take up space and more power in dense servers.

Infiniband is used in a number of storage and compute architectures now and is focused on getting high bandwidth and low latency. As a result of this focus, we have seen a lot of investment on building out the feature set to provide higher-end networking features.

Bringing the interconnect on-die means that Oracle does not need to go to a traditional PCIe bus lowering power but also providing higher speed access to the interconnect.

Hopefully we can get one of these boxes to test and see exactly how fast this integrated interconnect is. The key trend we are seeing is a continued integration of software features and interconnects on-die and on-package. The Oracle Sonoma platform follows this trend and will hopefully bring prices down to more x86-like levels. The Sonoma will be built on a 20nm node so there is still a large gap to what Intel has from a process perspective, however by integrating more functionality on-die Oracle’s Sonoma processor may be competitive from a performance per watt perspective.