As part of today’s Compute Express Link CXL 2.0 announcement, Microchip is starting its ecosystem enablement efforts with PCIe Gen5 and CXL 2.0 retimers. These are not necessarily the types of components that get big press, but they are very important for enabling an ecosystem. For those not familiar with retimers, these are devices that effectively act as signal boosters for signal transmission for PCIe and CXL.

PCIe Gen5 and CXL 2.0 Retimers Context

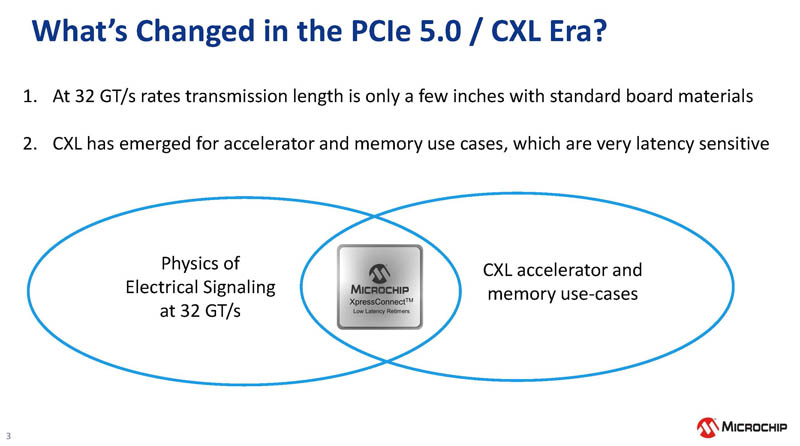

With PCIe Gen5, we get 32GT/s transmission rates. As a result of that higher speed, signal integrity degrades faster as well, limiting how far the signal can be reliably received. Also, with CXL, we have a fabric designed to support CPUs, memory, and accelerators so latency must be minimized.

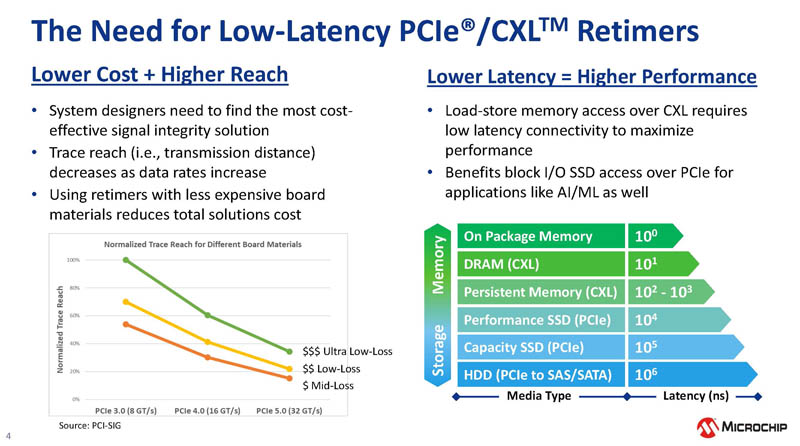

One of the more interesting slides in Microchip’s pre-briefing materials is the discussion on different PCB quality and signal loss. Higher quality PCB means more cost so vendors do not just use ultra low-loss PCB unless they need to. In the PCIe Gen5 era, even that ultra low-loss PCB cannot support as long of traces as we saw from relatively inexpensive mid-loss PCB in the PCIe Gen3 generation. Going up a level of PCB quality generally adds well over a hundred dollars to the BOM costs which is a big deal if you need to support lower-cost configurations such as a low-end CPU and a single SSD and DRAM stick. With the AMD EPYC 7002 Rome generation, we saw manufacturers need to move to higher-quality PCB in order to support the new chips which added cost to the motherboards and systems.

There are a lot of options to address this problem. We are seeing more cabled solutions such as in the Dell and AMD Showcase Future of Servers 160 PCIe Lane Design that you can see a video of here:

In that system, Dell is using cables to extend the range of PCIe Gen4, but also provide flexibility. Often in these systems we are also seeing PCIe retimers. If you saw our 4 solutions tested: Add 2.5″ SFF NVMe to your current system article, you can see a bit about PCIe switches and re-timers being used in the PCIe Gen3 era.

The bottom line is that the industry will need to find ways to address extending trace lengths of PCIe Gen5 and CXL in order to aid in system design. Servers are a fairly standard size and signals need to move to different areas of a chassis.

Microchip XpressConnect PCIe Gen5 and CXL 2.0 Retimers

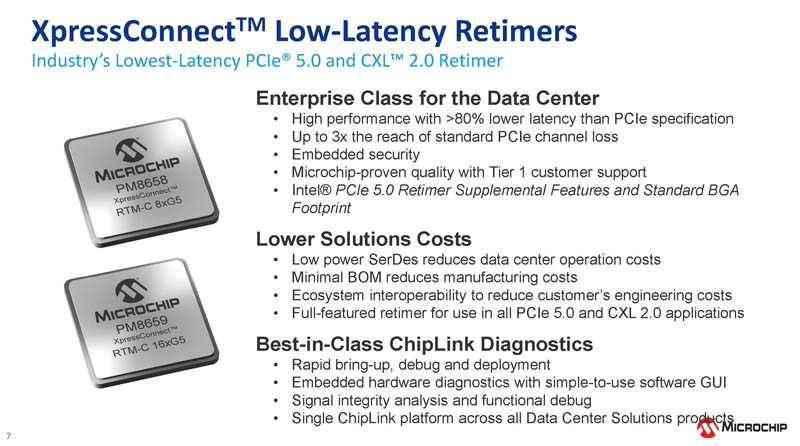

To address this, Microchip XpressConnect PCIe Gen5 and CXL 2.0 retimers are being launched today. Think of these as signal boosters for next-gen servers.

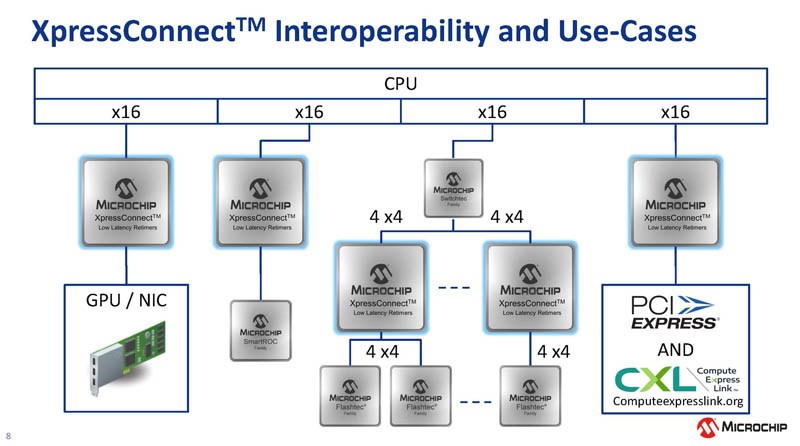

Some of the use cases are going directly to devices such as GPUs or storage accelerators. These retimers can also be used to bifurcate lanes. This allows for multiple devices to operate in a single x16 root. Of course, these work with both PCIe Gen5 and CXL which sits atop the Gen5 physical layer.

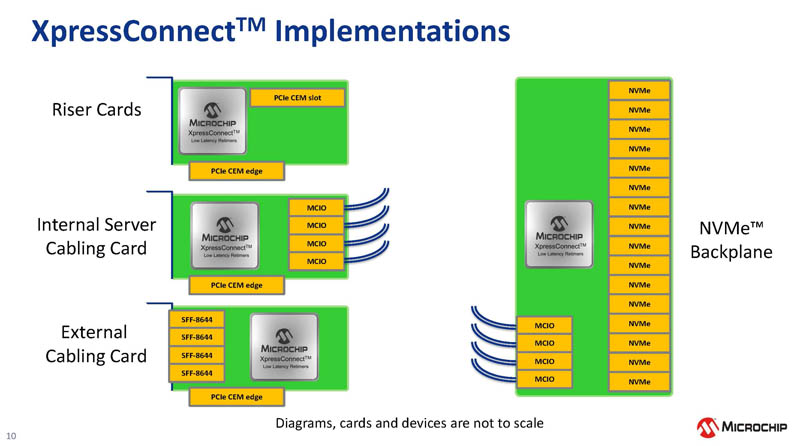

We often see PCIe retimers in risers, but one use case that Microchip highlighted was for external and internal cabling. One can have two re-timers in a chain to effectively give 3x the reach. In the example below, Microchip is showing off how one can have a card with a retimer and a NVMe backplane with a retimer and span the distance of an entire server chassis using cabling.

Since this is effectively adding a bump on the wire, there is a latency impact. Microchip told us it is on the order of 10ns so it fits into the latency profiles of most applications. We also wanted to point out that Microchip is supporting the CXL 2.0 security features that were announced alongside the new spec.

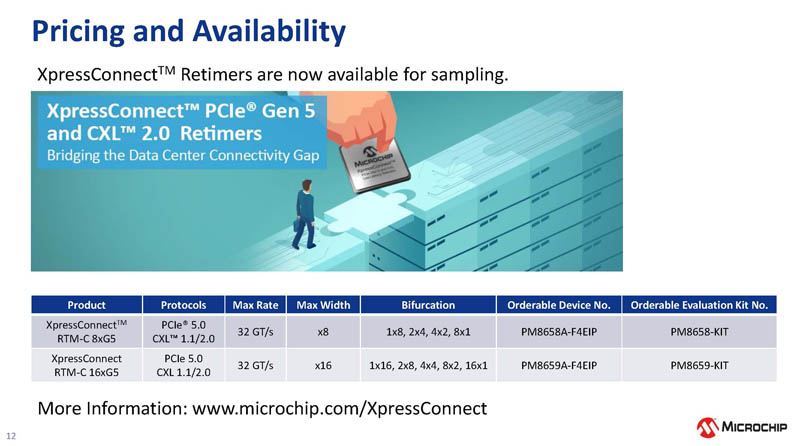

In terms of pricing, these are available to systems manufacturers now in x8 and x16 variants. Since the slide was titled “Pricing and Availability” we asked about pricing but Microchip politely declined to give even a list price.

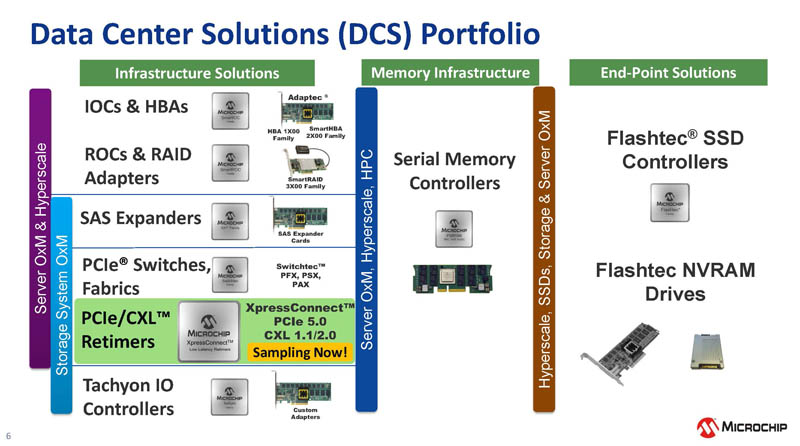

While Microchip is announcing the XpressConnect retimers today, it has a larger portfolio for the data center. Some, like this retimer, you are interested in more as a system builder than as a system customer. Others, you will be very interested in as a system customer.

For the record, we are waiting for an OMI serial memory controller to be announced from Microchip for PCIe Gen5 and CXL 2.0 since that product makes a ton of logical sense. We asked and Microchip politely declined (again) to comment on future products. Still, it would be a huge miss if Microchip does not make this so we feel like at some point we are going to cover that announcement in the coming years.

Final Words

Generally on STH we do not cover components such as retimers. These products have a very limited audience. At the same time, I wanted to cover these Microchip XpressConnect PCIe Gen5 and CXL 2.0 retimers because I think they are an important step in getting to a completely new paradigm of data center computing in the 2023-2025 timeframe (hopefully.) Of course, we shall see how this plays out, but these are simply part of the ecosystem we need to build that next generation. Many will look to the switching aspects of the new CXL 2.0 spec, but adding retimers is an important step to building the systems as well.

Great article with clear path to PCIe 5.0 bus & higher interconnect speeds. The question is how many sources for these functions, since we need competition to keep prices reasonable.