Here is a fun one. At OCP Summit 2024, Marvell showed off a functional PCIe Gen7 SerDes running at 128GT/s. This is already working in 3nm process for next-gen chips. Or perhaps better said, next-next-gen chips.

Marvell Shows off 3nm PCIe Gen7 SerDes at OCP Summit 2024

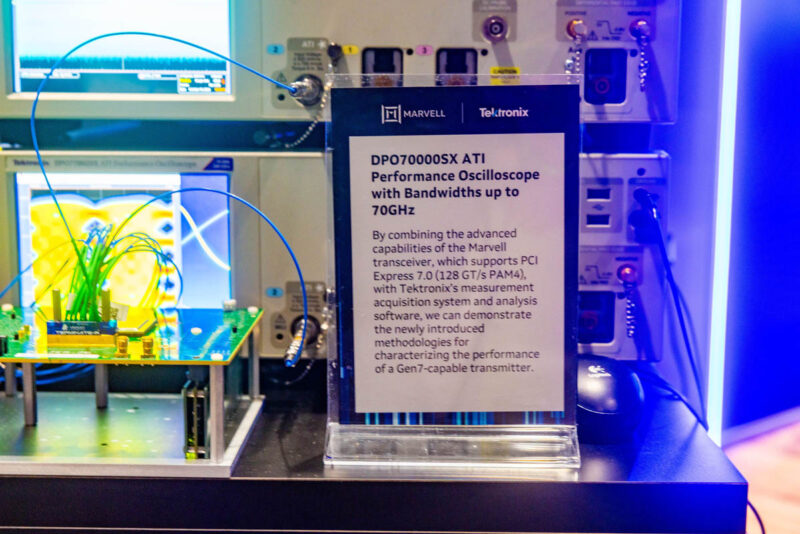

The Marvell part was running alongside a Tektronix box to validate the PCIe Gen7 operation at 128GT/s. The industry is moving to PAM4 for these connections to support new generations of PCIe.

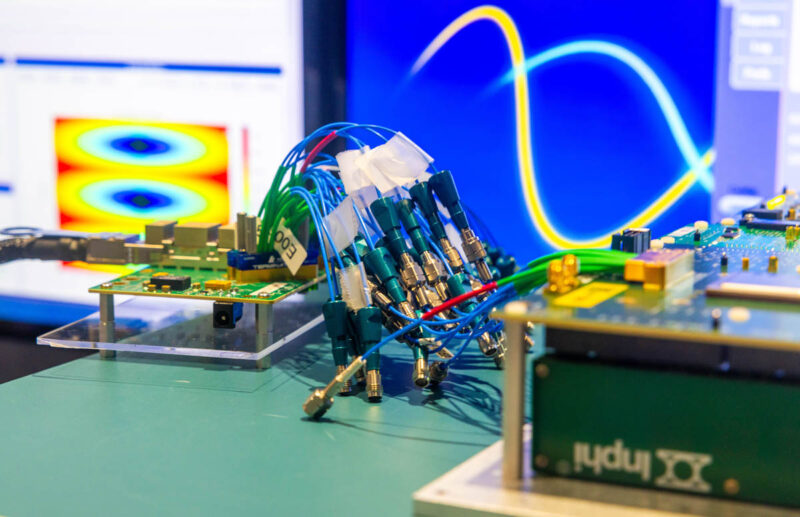

The companies were showing off the eyes as well as some of the test data.

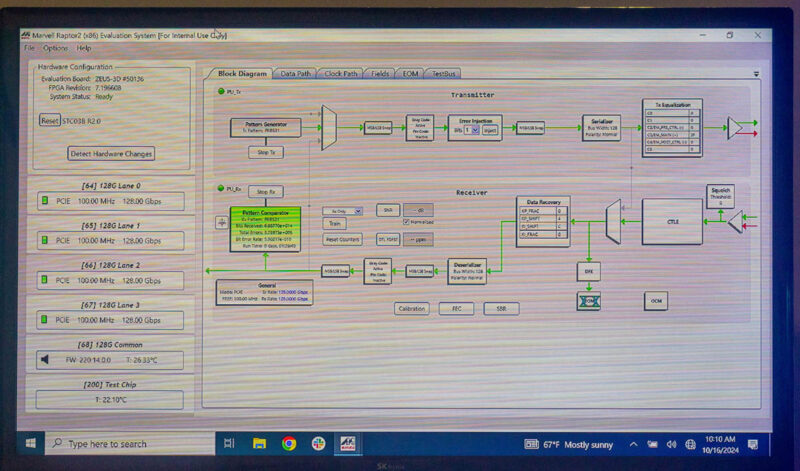

Here is another shot showing the 128Gbps lanes running. The screens did not photograph well with the Canon R5 II.

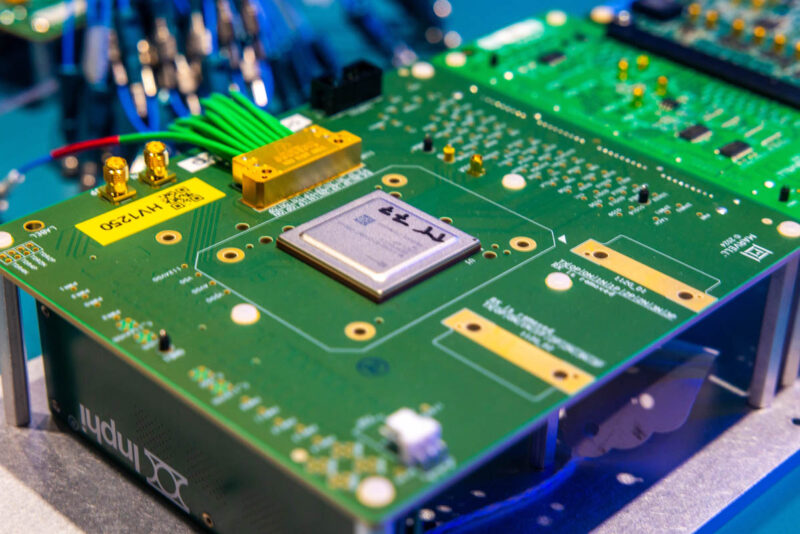

The setup was not just a single board, and the demo was running and showing the eye diagrams live, so it was thoroughly a test setup.

Still, this is 3nm SerDes, which is really neat to see.

Current generations of PCIe Gen5/6 devices and switches like the Marvell Teralynx 10 51.2T Switch we see today often use 5nm, so seeing a higher speed in a new process node is exciting.

Final Words

The PCIe world is rapidly evolving. Instead of generations spanning the better part of a decade, like PCIe Gen3, hyper-scalers are pushing to faster generations of PCIe. We should see PCIe Gen6 next year and then expect PCIe Gen7 to be not far behind. As process nodes shrink, I/O tends to be much harder to scale. Seeing a SerDes running a live demo on a show floor today is a good sign that organizations will figure out PCIe Gen7 in time.

> “The screens did not photograph well with the Canon R5 II.”

https://photo.stackexchange.com/questions/21294/whats-the-best-way-to-take-a-picture-of-an-lcd-or-crt-screen/21299#21299