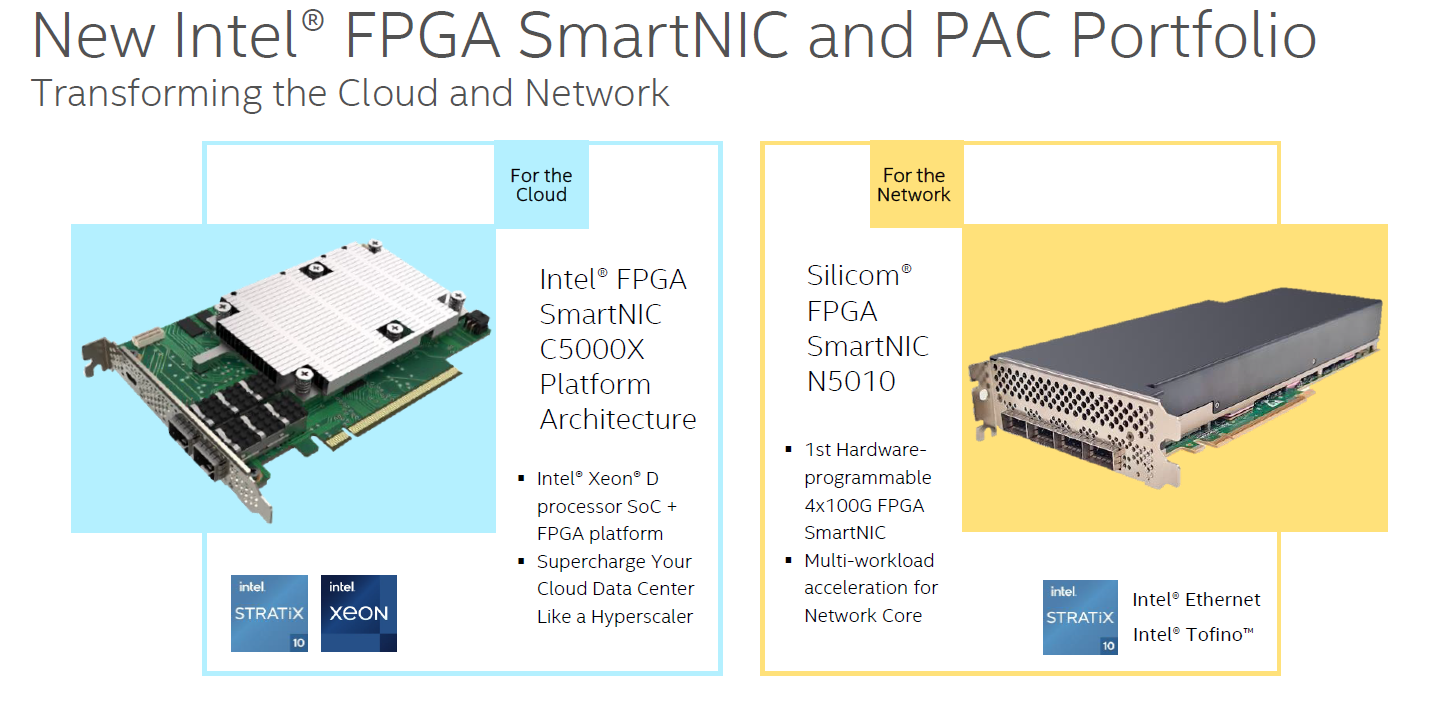

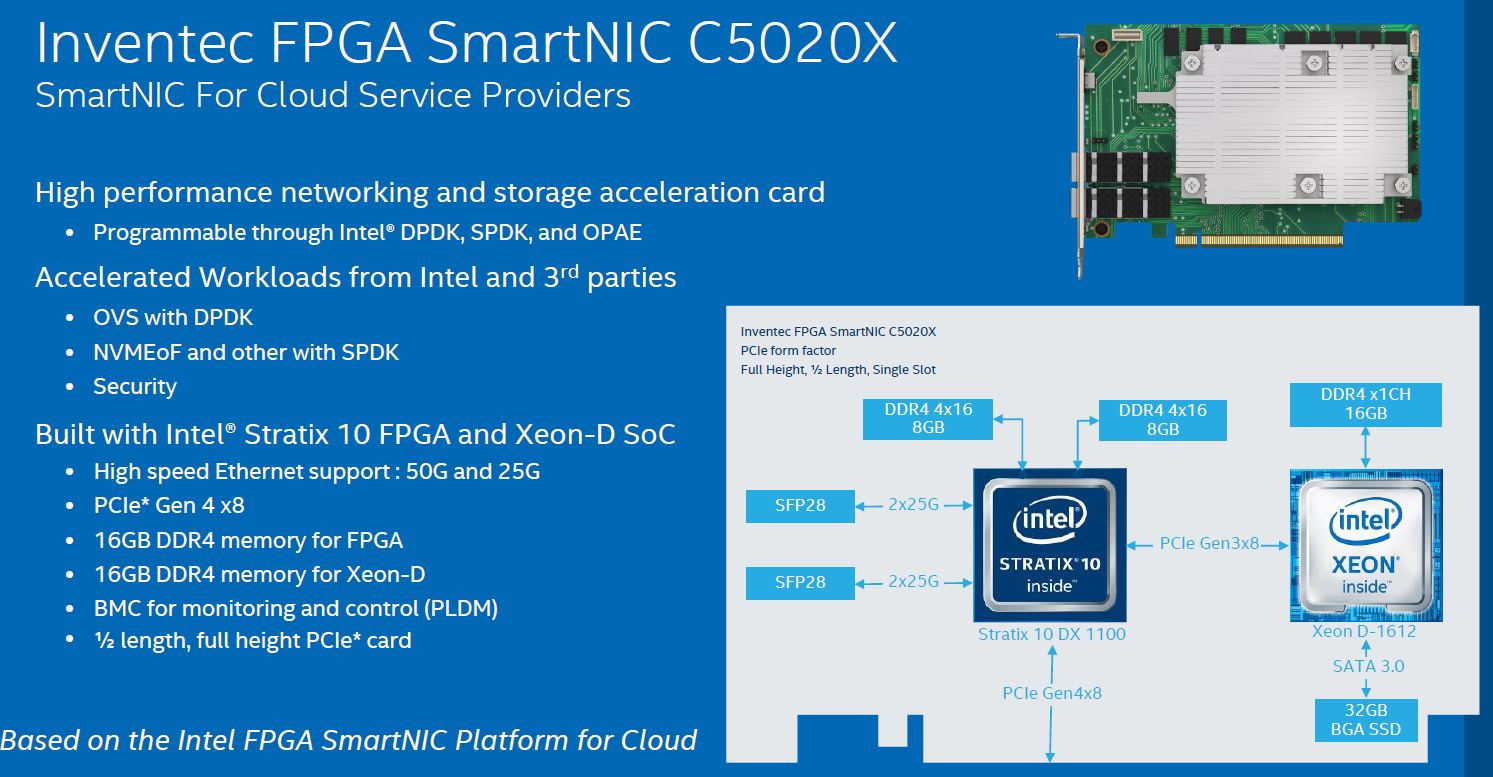

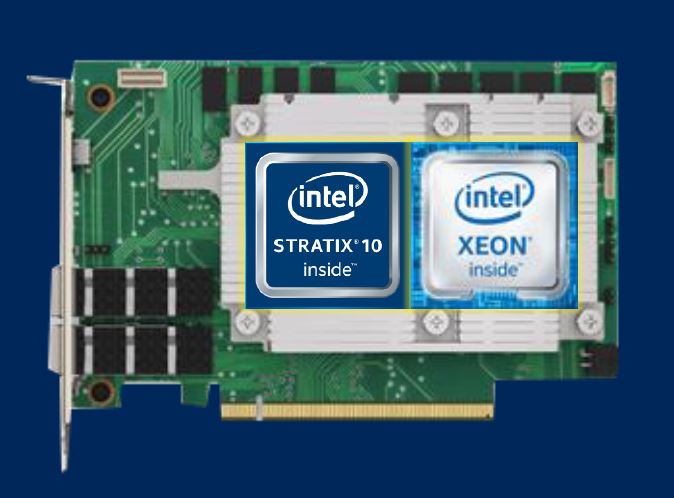

Today on STH we are featuring a duo of new SmartNICs based on Intel FPGAs. The first is the Inventec FPGA SmartNIC C5020X which combines an Intel Xeon D processor with an Intel Stratix 10 FPGA for what Intel calls a cloud FPGA SmartNIC platform. In this solution, Intel provides the main pieces of silicon while Intventec packages the silicon into a solution that can be sold to customers.

The Intel FPGA SmartNIC Strategy Context

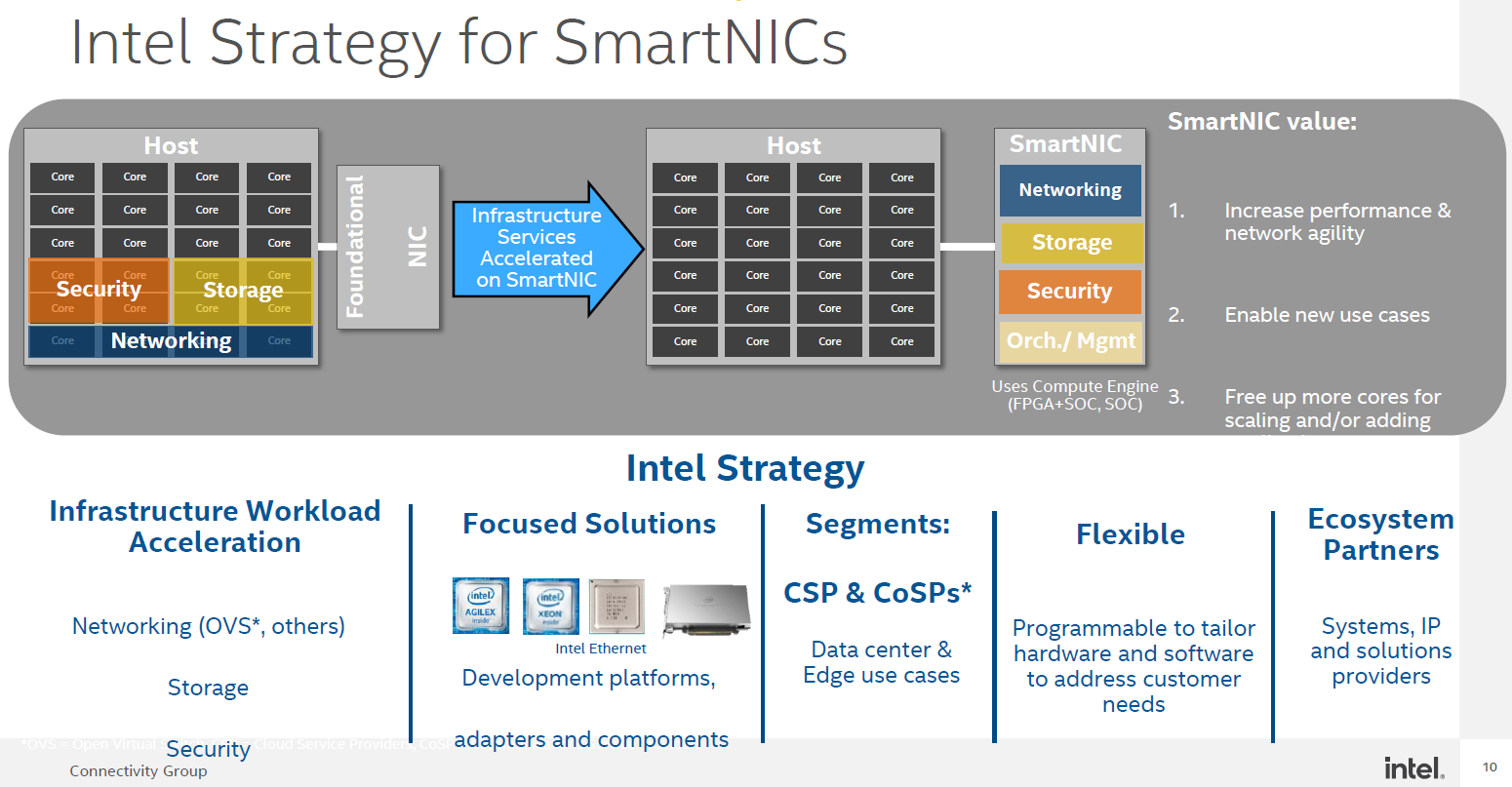

The world of network interface cards is getting more intelligent. This is the next step in data center disaggregation. Having more capabilities at the NIC-level allows for more efficient utilization of x86 cores while delivering higher-end features and better security.

The Inventec FPGA SmartNIC C5020X is part of today’s duo of card announcement from Intel and is designed more for the cloud server. The other announcement is another NIC designed for heavy network workloads. You can see more on the Silicom announcement here.

As we are going to see, the Inventec FPGA SmartNIC C5020X borders on what we would consider a DPU. We are going to discuss why it sits on the edge later in this article.

Inventec FPGA SmartNIC C5020X

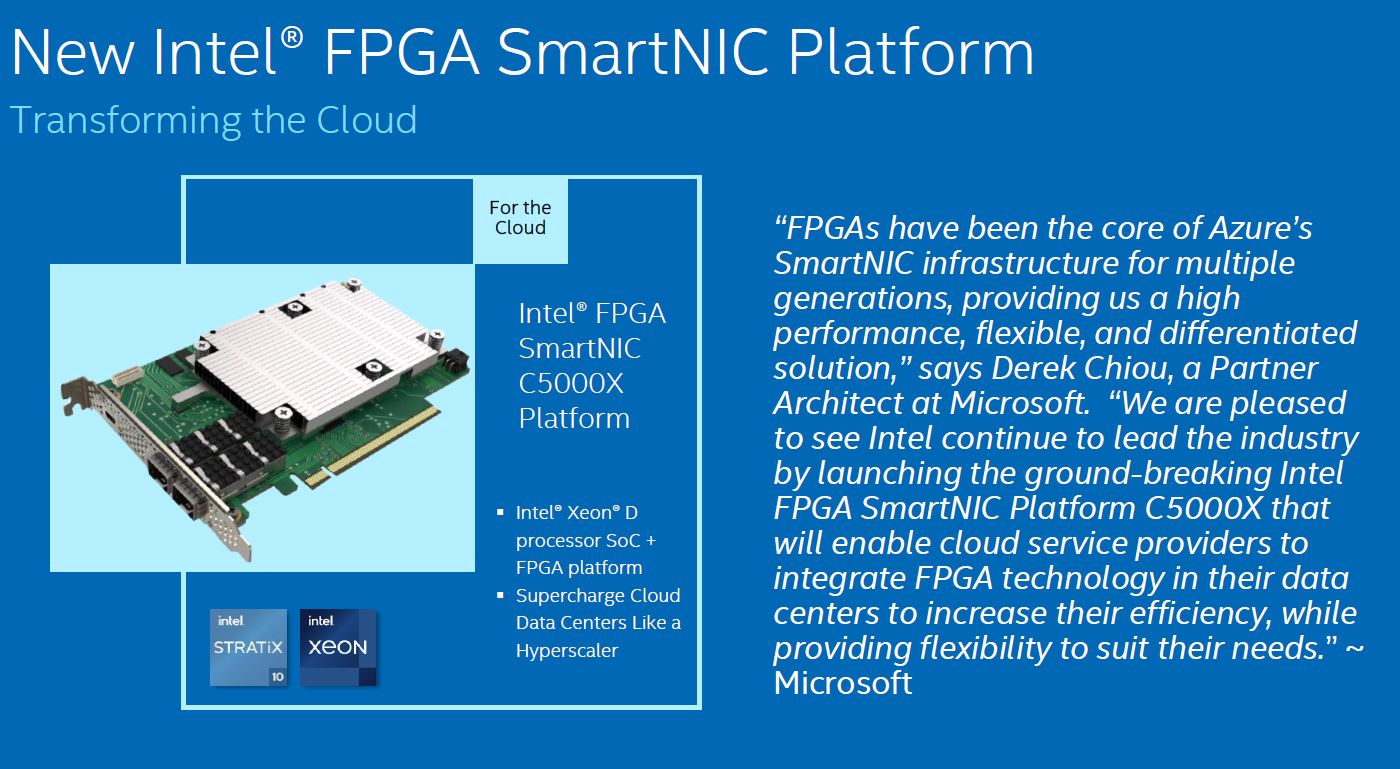

The Intel FPGA SmartNIC platform is designed to offer FPGA-based offloads to the cloud service providers. At STH, we have covered Microsoft Azure’s use of FPGA NICs in pieces such as Microsoft Debuts Project Brainwave Access to Intel FPGAs for AI. We will note that Microsoft’s quote is not specifically saying this is the product they are deploying.

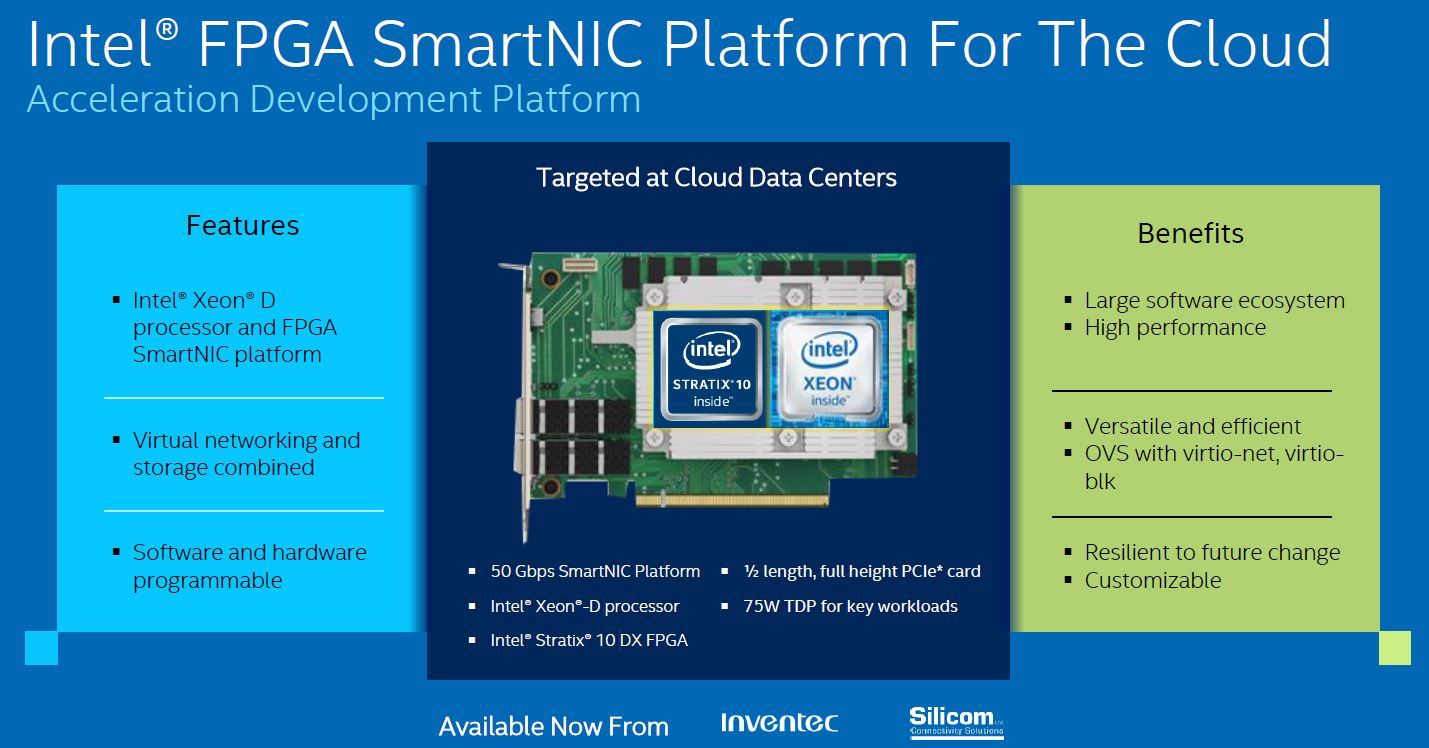

The key parts of the Intel FPGA SmartNIC platform for the cloud are that it combines an Intel Xeon D processor along with a Stratix 10 FPGA onto a single PCB. This is not a new packaging technique that Intel has been discussing for years although that is a possibility for future generations.

One of the great features is that we get the details around the Inventec FPGA SmartNIC C5020X. Here we can see that we have an Intel Xeon D-1612 with a 32GB SSD and 16GB of DDR4 memory. We have a PCIe Gen3 x8 connection to the Intel Stratix 10 DX 1100 FPGA. That Stratix 10 FPGA has its own 16GB of DDR4 along with providing 25/50GbE connectivity as well as PCIe Gen4 x8 connectivity.

As a quick note here, Inventec also has an Arm-based solution. The Inventec X250 utilizes an Arria 10 GX660 along with a Broadcom Stingray BCM8804 NIC which has a similar form factor and also fits in the 75W TDP envelope. For some organizations, keeping everything on x86 including SmartNICs simplifies deployments so a key value proposition of this over the X250 is also the ability to manage the solution using x86 rather than having another architecture in the mix, leaving the fact that the Stratix 10 DX has Arm A53 cores inside for management.

Inventec FPGA SmartNIC C5020X DPU or SmartNIC?

The big question here is whether this is indeed a DPU. In our piece, What is a DPU A Data Processing Unit Quick Primer we noted current solutions have a few common features:

- High-speed networking connectivity – Here the networking falls below the common 200Gbps in an aggregate threshold we use for this

- High-speed packet processing with specific acceleration and often programmable logic – With the FPGA, we can say that there is programmable logic to provide acceleration

- A CPU core complex – here we have the Intel Xeon D-1612 so this is met

- Memory controllers – here both the FPGA and Xeon D have DDR4 memory controllers so we can consider this met

- Accelerators – This is the weakest link in the chain. The Xeon D-1612 does not have the same level of offload capabilities found in newer processors. Usually, these are higher-end hardened IP blocks in DPUs so we are going to say there is an acceleration story, but it is not met with this solution

- PCIe Gen4 lanes run as either root or endpoints – Since the PCIe Gen4 lanes are handled by the Stratix 10, we know that it and be run in endpoint mode. We have heard Stratix 10 can be made to run in a root mode. To us, the fact that this is not a use case specifically designed in the platform means that we would not consider this as met

- Security and management features – This is probably an area where the Inventec FPGA SmartNIC C5020X borders on meeting our criteria

- Runs its own OS separate from a host system – With the Xeon D, we have a familiar platform for this

On balance, this is a platform that is very close to a DPU, but we would still classify this as a SmartNIC going forward. It certainly is a large step up from a foundational NIC such as the Intel Ethernet 800 series but it does not have many of the DPU market features implemented.

The reason we are discussing this in such detail is that I expressed that I want the industry to call that class of device a DPU in the future. This is a campaign I am launching in the industry to get NICs classified along some basic guardrails so we can start to group the myriad of solutions out there. Without these classifications, it is hard for our readers to track the stratification of solutions.

Final Words

Overall, we think that the Inventec FPGA SmartNIC C5020X is an interesting solution for a set of customers, but it is unlikely the solution that we are going to find having mass-market appeal as we will see with Columbiaville. What the product does showcase is Intel’s ability to bring together elements of its portfolio onto a single device. As part of Intel’s networking and interconnect strategy going forward, mixing technologies from different parts of Intel will become an increasingly important practice. For Inventec, the FPGA SmartNIC C5020X provides an alternative to the Broadcom-based offering which helps its cloud customers diversify their options.

Patrick,

I agree with your assessment of the lack of support for PCIe root and/or dual-mode functionality is disappointing. We can only hope that the necessary software IP Core becomes available.

Referring to the compute side of the C5020X solution, it seems disappointing that only 16GB of CPU memory is provided. I would have liked to have seen 32 or 64GB be available or add support for SO-DIMM for expansion.

Unfortunately that 16GB is in one channel, so not using all the capabilities of the Xeon D. Perhaps that will help maximise the boost within the 22W TDP, though? 1.5-2.5Ghz is quite a variable speed for an essentially embedded device.

Then again, my D-1521 boosts to the full 2.7Ghz all-core for 5W less than its 45W TDP, so since the D-1612 is newer and doesn’t have to handle 2x10GbE, perhaps it will be close to the upper end as well.

Alas, the 32GB SSD is eMMC, so seems like more of a boot drive for in-memory operation.