It feels like forever since we covered the Welcome to the Intel Ice Lake D Era with the Xeon D-2700 and D-1700 series. Now it is time to talk about its refresh. Instead of adopting the cores from the 4th/5th Gen Xeon Sapphire Rapids/ Emerald Rapids, the Intel Xeon D series is getting the Xeon 6 treatment with the Granite Rapids-D part in 2025.

For those who want to catch up, we have an entire archive of Broadwell-DE and Skylake-D series Xeon D content on STH. We also did the Ice Lake-D launch video:

Please note that we are doing these live at Hot Chips 2024 this week, so please excuse typos.

Intel Xeon 6 SoC for the Edge Hello Granite Rapids-D

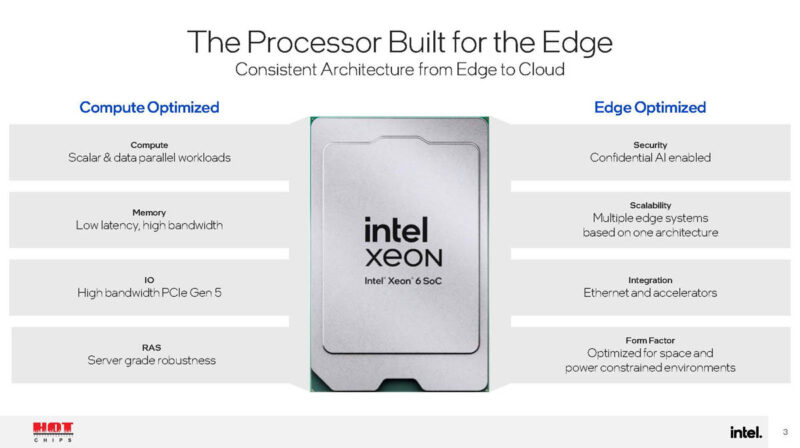

The Intel Xeon D line is designed for the edge, specifically bringing performance cores and integrated network and acceleration to the edge. It sits between the Atom line with E-cores and the mainstream Xeon lines. The edge is also different because it requires different operating temperatures and environmental profiles.

The new chips have PCIe Gen5, which is up from PCIe Gen4 in Ice Lake-D, and new features.

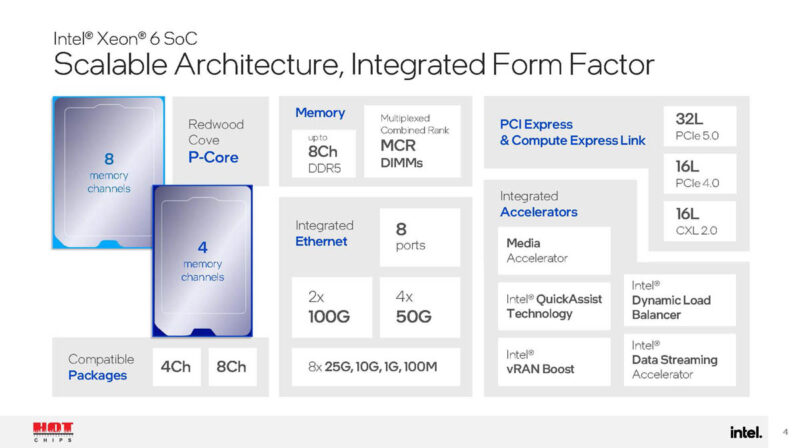

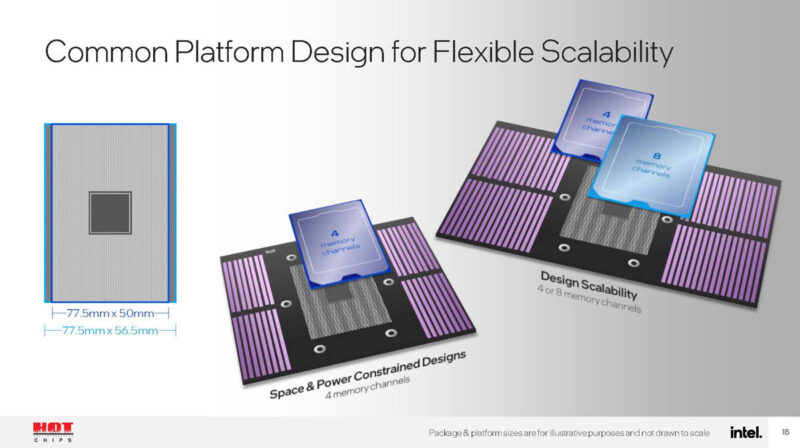

Here are the highlights, and WOW. There are both 4-channel and 8-channel designs, and they can use high-speed MCRDIMMs. There is 100GbE connectivity, Intel QuickAssist, DLB, DSA, and vRAN Boost. The I/O looks really interesting as well with up to 32 lanes of PCIe Gen5 and CXL 2.0 support.

Intel says it gets more cores, more bandwidth, and more I/O.

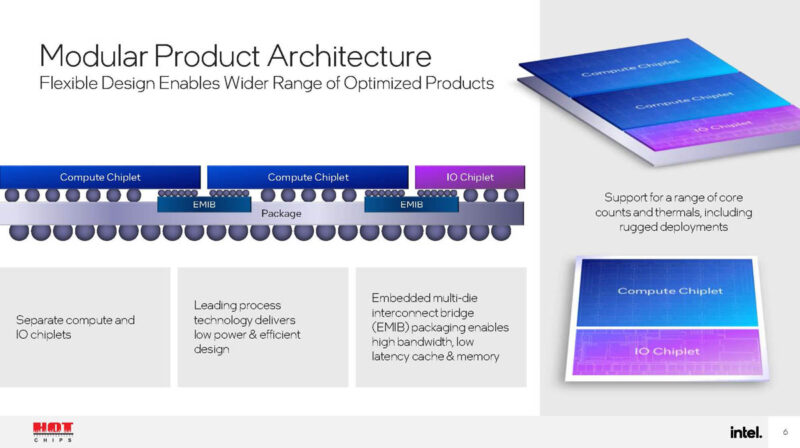

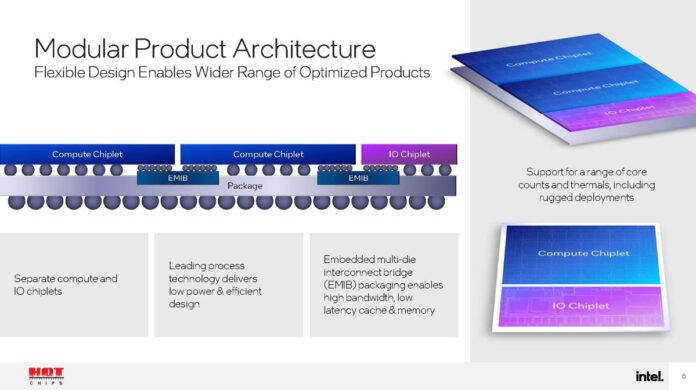

This is also interesting since Intel is showing its compute and I/O chiplets. We covered this a bit last year with Intel Shows off Granite Rapids and Sierra Forest Packages. The big change here is that Intel is entirely moving to next-gen packaging for Xeon-D.

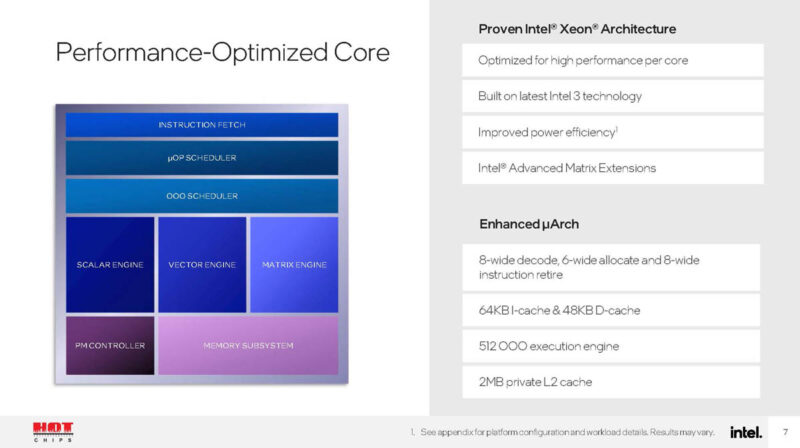

The performance core is the Granite Rapids / Redwood Cove P-core. Notably not the Intel Lunar Lake P-core.

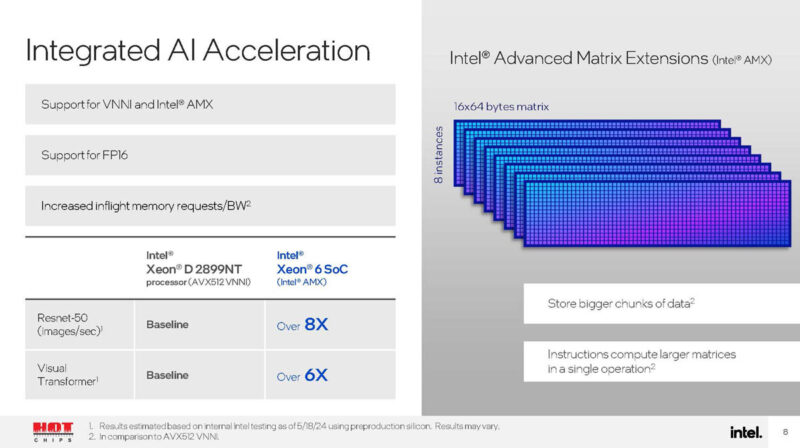

The new chips support AMX for AI acceleration. This may not seem like a big deal if you are accustomed to the higher-end Xeon’s, but if you are coming from an Ice Lake-D with VNNI only, this is a big jump in AI performance.

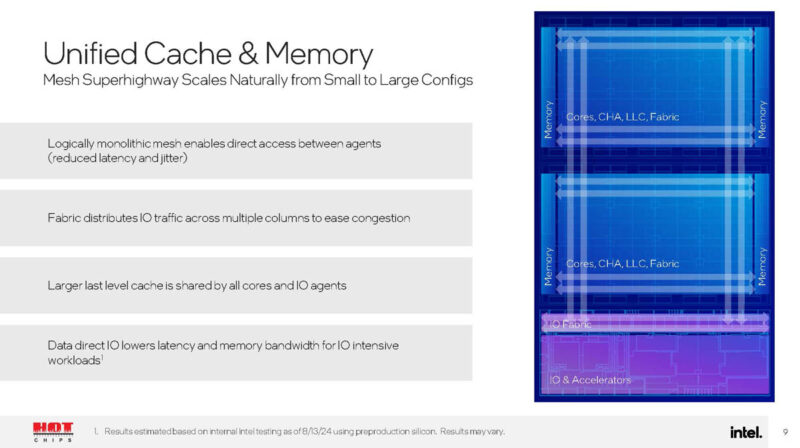

Here is the unified cache and memory that is being stitched together using EMIB.

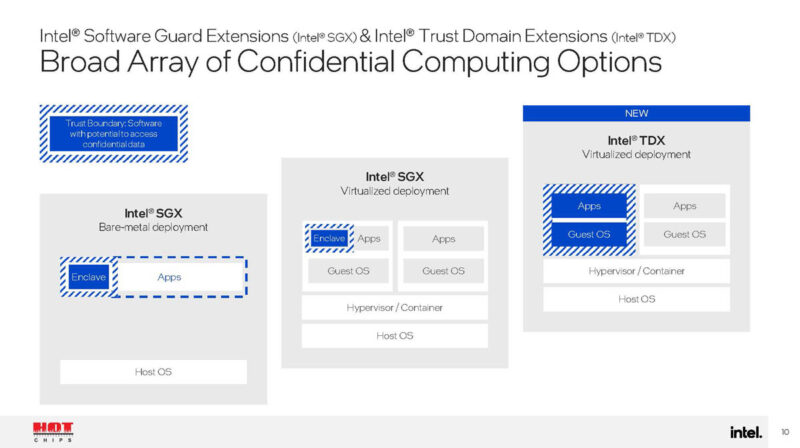

We also get Intel SGX and TDX for confidential computing.

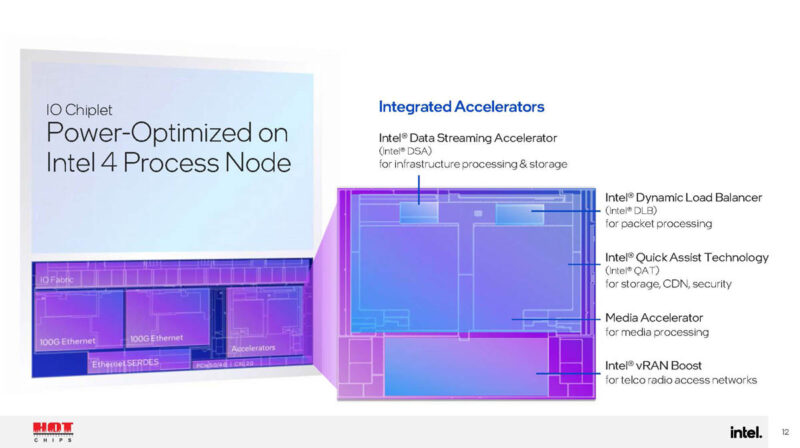

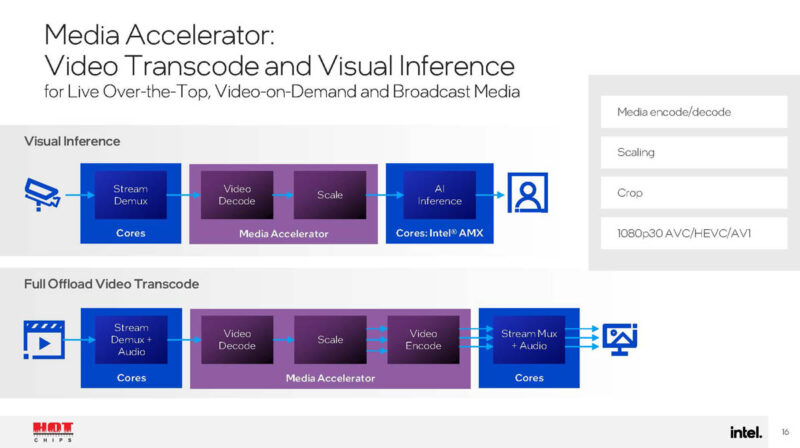

The new I/O chiplet is built on Intel 4. Here, we can see the various accelerators, including DSA, DLB, and QAT. It will be interesting to learn more about the media accelerator. Intel says it is for AI inference and transcoding.

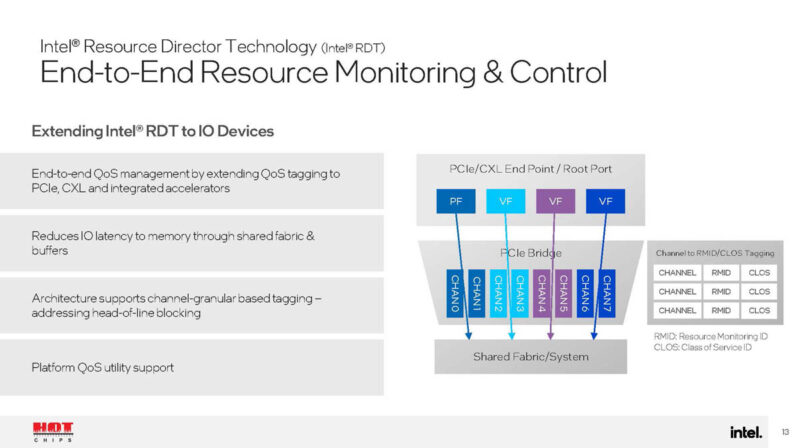

The new chips have Intel Resource Director Technology that helps with things like QoS on the platform.

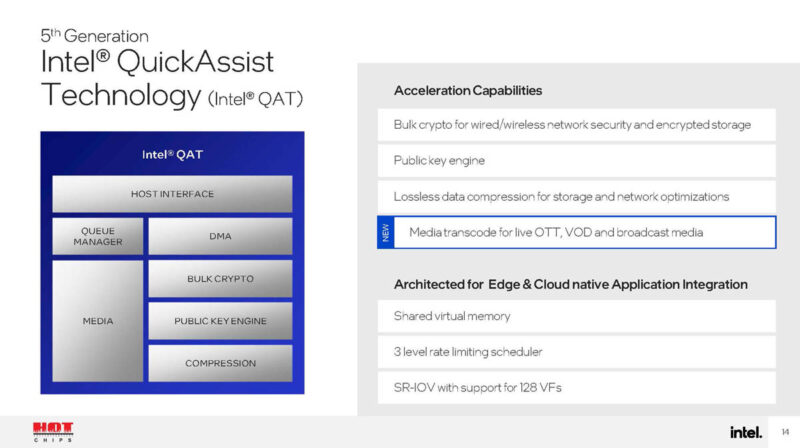

Here is a bit more on QAT, there is media transcoding! This is really neat as it will expand the use cases for QAT beyond compression and crypto.

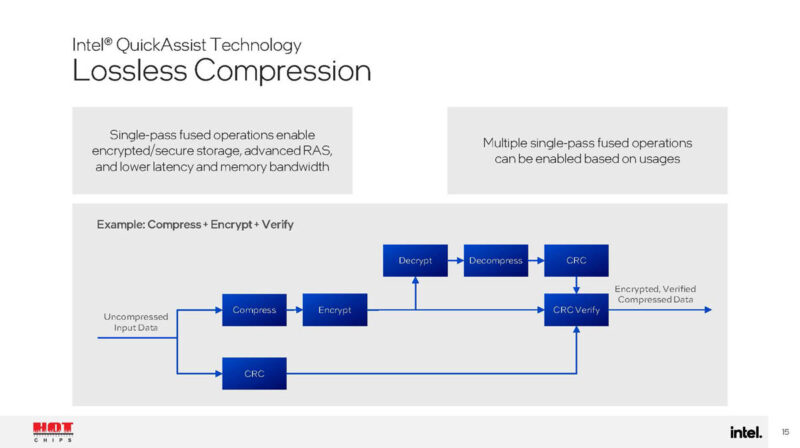

Intel QAT helps with compression. This is a single pass, verified compression, to ensure the compression is not losing fidelity in the process. This is a new feature for this generation.

Here we go. It looks like there is at least 1080p30 AVC, HEVC, and AV1 encoding, decoding, scaling, and cropping. Video can be decoded using the hardware offload and then used in AI inference. This is a very important capability.

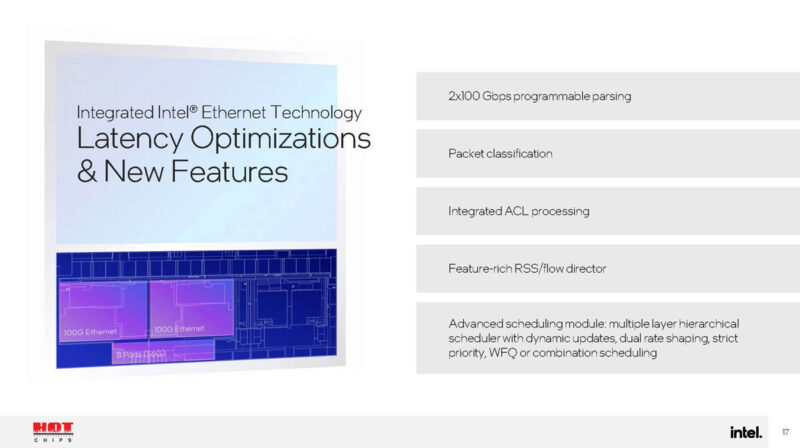

Intel is adding features to its 100GbE networking. The company says that removing PCIe lowers the power needs, but it will also let this run custom parsing so customers can program the networking. That is a new capability.

Here is something cool: we can see a 4-channel memory 2 DIMM per socket design as well as an 8-channel memory design for the SoC.

This looks like a big update to the Xeon D-line.

Final Words

Remember the original Intel Xeon D-1500 era with 45W TDP CPUs like the Intel Xeon D-1540? Those days appear to be gone. Still, next year will mark the 10-year anniversary of Xeon D, and it is cool to see how it has evolved over that time.

It is cool to see how performance-oriented this platform is compared to previous generations. At the same time, it feels a bit like there will be a big gap between the Atom lines and the Xeon 6 SoC. It feels like the Atom P5000/C5000 line needs an update with more modern E-cores. Even with that, the baseline networking feels like it is becoming 100GbE, leaving a void for 10GbE/ 25GbE solutions. It also feels like Intel saw AMD Siena and is moving up-market.

The oddity is that Intel seemingly added QuickSync without putting in a full fledge GPU. Given that they’ve moved to a modular chiplet style packaging, adding a GPU die from say the consumer based products would be an ideal re-use of technology. For users who don’t want/need it, Intel saves money on silicon. However, this doesn’t seem to be the case.

Piggy backing on the chiplet idea, the edge market that this is targeted at would also benefit from on package FPGA options that wouldn’t leverage the normal PCIe lanes. Seems like a missed opportunity here.

Dual on chip 100 Gbit Ethernet is fast but many Xeon D appliances today still come with some sort of additional networking provide more ports. Here in this generation it’d have been nice to support quad 100 Gbit Ethernet with options to break that out into two 100 Gbit + eight 25/10 Gbit ports.

Lastly, what is the total number of PCIe lanes? Else where they indicated 32 PCIe 5.0 lanes total with 16 lanes being CXL 2.0 capable but here it reads as 64 total with 32 PCI 5.0 + 16 PCIe 4.0 + 16 CLX 2.0.

Thanks. Best coverage I’ve seen.

This chip also updates AMX with Complex operations, according to the October Architecture manual.

https://cdrdv2-public.intel.com/836496/architecture-instruction-set-extensions-programming-reference.pdf