The Intel Stratix line is the company’s high-end FPGA line. Intel is now fully invested in the FPGA business after its blockbuster Altera acquisition that happened before this product cycle. One of the key areas that FPGA have traditionally played in is communications infrastructure and the Intel Stratix 10 TX variant is specifically geared toward this market.

Intel Stratix 10 TX

The Intel Stratix 10 family utilizes EMIB to allow fusing heterogeneous “chiplets” into a single package. In the Stratix 10 TX case, this means fusing the traditional FPGA components such as logic elements and adaptive logic modules with high-speed 58G transceivers.

The 58G transceivers can operate at previous generation standards (28G and lower) speeds allowing the company to deliver backward compatibility at a lower power footprint than previous generations.

With the newer generation chips and the optical transceivers that will be released this quarter, Intel expects the Stratix 10 TX to play in a space for next-generation 5G infrastructure roll-outs where the entire infrastructure will need to focus on providing higher bandwidth and lower latencies.

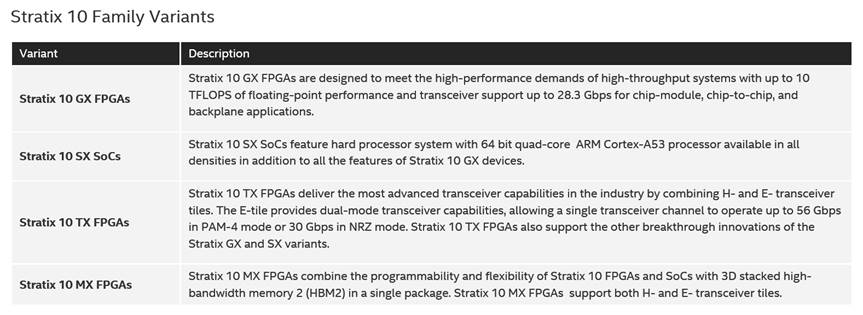

Intel Stratix 10 TX in the Overall Stratix 10 Family

As one of four variants in the Intel Stratix 10 family, the TX line has is positioned specifically as having the higher-end transceivers options with its 58G transceivers.

We asked Intel, and the focus on the TX variant is telecoms. These are not intended for hyper-scale AI applications like other Stratix 10 variants as found in Microsoft Shows off Project BrainWave Persistent Inferencing from FPGA Cache.

Intel Stratix 10 TX Key Specs

Here is a spec table for the Intel Stratix 10 TX family. You can see the full spec sheet here.

| TX 1650 | TX 2100 | TX 2500 | TX 2800 | |||||||||||||

| Resources | Logic elements (LEs)1 | 1,679,000 | 2,073,000 | 2,422,000 | 2,753,000 | |||||||||||

| Adaptive logic modules (ALMs) | 569,200 | 702,720 | 821,150 | 933,120 | ||||||||||||

| ALM registers | 2,276,800 | 2,810,880 | 3,284,600 | 3,732,480 | ||||||||||||

| Hyper-Registers from Intel® HyperFlexTM FPGA architecture | Millions of Hyper-Registers distributed throughout the monolithic FPGA fabric | |||||||||||||||

| Programmable clock trees synthesizable | Hundreds of synthesizable clock trees | |||||||||||||||

| eSRAM memory blocks | 2 | 2 | – | – | ||||||||||||

| eSRAM memory size (Mb) | 90 | 90 | – | – | ||||||||||||

| M20K memory blocks | 6,162 | 6,847 | 9,963 | 11,721 | ||||||||||||

| M20K memory size (Mb) | 120 | 134 | 195 | 229 | ||||||||||||

| MLAB memory size (Mb) | 9 | 11 | 13 | 15 | ||||||||||||

| Variable-precision digital signal processing (DSP) blocks | 3,326 | 3,960 | 5,011 | 5,760 | ||||||||||||

| 18 x 19 multipliers | 6,652 | 7,920 | 10,022 | 11,520 | ||||||||||||

| Peak fixed-point performance (TMACS)2 | 13.3 | 15.8 | 20.0 | 23.0 | ||||||||||||

| Peak floating-point performance (TFLOPS)3 | 5.3 | 6.3 | 8.0 | 9.2 | ||||||||||||

| I/O and Architectural Features | Secure device manager | AES-256/SHA-256 bitsream encryption/authentication, physically unclonable function (PUF), ECDSA 256/384 boot code authentication, side channel attack protection | ||||||||||||||

| Hard processor system | Quad-core 64-bit ARM* Cortex*-A53 up to 1.5 GHz with 32KB I/D cache, NEON* coprocessor, 1 MB L2 Cache, direct memory access (DMA), system memory management unit, cache coherency unit, hard memory controllers, USB 2.0 x2, 1G EMAC x3, UART x2, SPI x4, I2C x5, general purpose timers x7, watchdog timer x4 – – Yes Yes |

|||||||||||||||

| Maximum user I/O pins | 544 | 440 | 544 | 440 | 544 | 440 | 296 | 544 | 440 | 296 | ||||||

| Maximum LVDS pairs 1.6 Gbps (RX or TX) | 264 | 216 | 264 | 216 | 264 | 216 | 144 | 264 | 216 | 144 | ||||||

| Total full duplex transceiver count | 72 | 96 | 72 | 96 | 72 | 96 | 144 | 72 | 96 | 144 | ||||||

| GXE transceiver count – PAM-4 (up to 56 Gbps) or NRZ (up to 30 Gbps) |

12 PAM-4 24 NRZ |

36 PAM-4 72 NRZ |

12 PAM-4 24 NRZ |

36 PAM-4 72 NRZ |

12 PAM-4 24 NRZ |

36 PAM-4 72 NRZ |

60 PAM-4 120 NRZ |

12 PAM-4 24 NRZ |

36 PAM-4 72 NRZ |

60 PAM-4 120 NRZ |

||||||

| GXT transceiver count – NRZ (up to 28.3 Gbps) | 32 | 16 | 32 | 16 | 32 | 16 | 16 | 32 | 16 | 16 | ||||||

| GX transceiver count – NRZ (up to 17.4 Gbps) | 16 | 8 | 16 | 8 | 16 | 8 | 8 | 16 | 8 | 8 | ||||||

| PCI Express* (PCIe*) hard intellectual property (IP) blocks (Gen3 x16) | 2 | 1 | 2 | 1 | 2 | 1 | 1 | 2 | 1 | 1 | ||||||

| 100G Ethernet MAC (no FEC) hard IP blocks | 2 | 1 | 2 | 1 | 2 | 1 | 1 | 2 | 1 | 1 | ||||||

| 100G Ethernet MAC + FEC hard IP blocks | 4 | 12 | 4 | 12 | 4 | 12 | 20 | 4 | 12 | 20 | ||||||

| Memory devices supported | DDR4, DDR3, DDR2, DDR, QDR II, QDR II+, RLDRAM II, RLDRAM 3, HMC, MoSys | |||||||||||||||