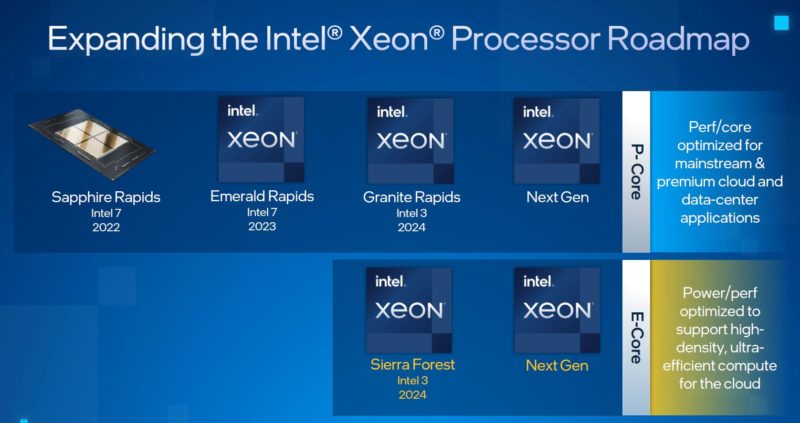

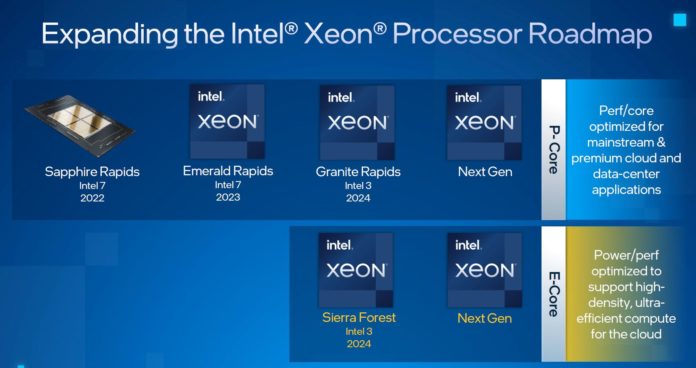

Intel Sierra Forest uses Intel’s efficient cores to create a higher-core count platform for cloud service providers. While we have heard Granite Rapids before, specifically for the P-core-based offering, Intel at Investor Meeting 2022 is talking about the other chip destined for that platform, Sierra Forest. Effectively Intel is saying that in its next-generation platform it plans to offer two types of cores with a common high-level platform feature set. This is in many ways very similar to what AMD is doing with Genoa and Bergamo. It is also is exactly what Intel needs.

Note: This is being done live at Investor Meeting 2022 so please excuse typos.

Intel Sierra Forest the E-Core Xeon Intel Needs

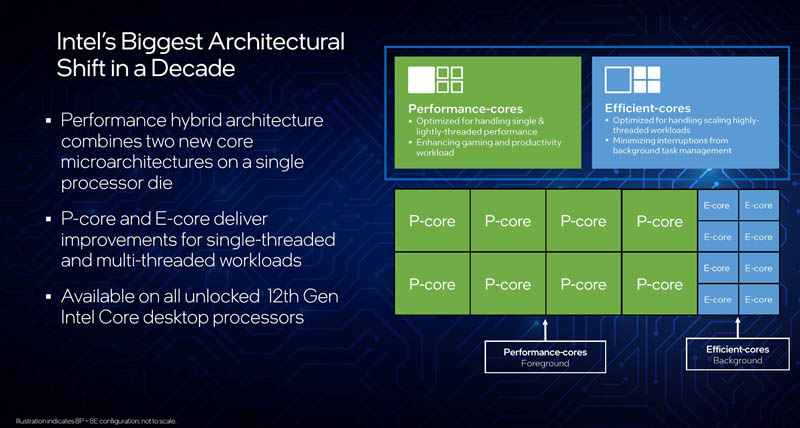

Intel currently has a challenge. It has very high-performance cores it calls its “P-cores” that are designed for maximum per-core or per-thread performance. These cores are loaded with features like AVX-512 that are excellent at accelerating some workloads, as we have shown with AWS EC2 M6i Instances. At the same time, P-cores have to dedicate the die area to all of that functionality, and that is problematic. Many cloud workloads simply do not use all of that extra acceleration and performance.

On the customer side, Intel has many large cloud service providers that simply do not care as much about having HPC acceleration. They instead want a certain ECU/vCPU integer and floating-point performance. Anything above that is almost unnecessary if it comes at the expense of core density.

On the customer side, Intel has many large cloud service providers that simply do not care as much about having HPC acceleration. They instead want a certain ECU/vCPU integer and floating-point performance. Anything above that is almost unnecessary if it comes at the expense of core density.

What Intel is basically doing with Sierra Forest is using its efficient cores, which currently fit roughly 4:1 in the space of its performance cores, and using those to make a CPU designed for these workloads. That allows Intel to fit more cores on the same package.

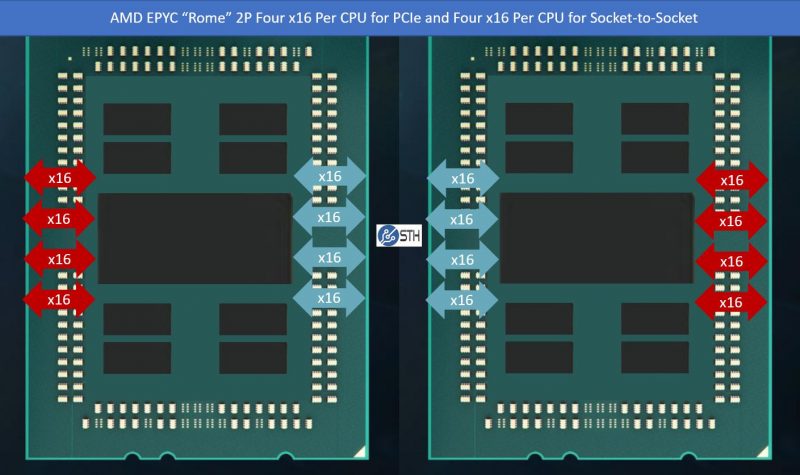

Intel is taking a page from the AMD playbook and is moving to a new chip design with Granite Rapids. It is disaggregating its uncore with its I/O and that is a huge portion of this announcement. Intel is effectively moving to the I/O die approach that AMD switched to in 2019 with the AMD EPYC Rome.

This approach has a profound impact. Intel is able to then use a common socket, firmware, and platform and switch in the type of compute die it needs for a given chip. In the future, this also paves the way for heterogeneous compute tiles to be used. That is similar to AMD’s approach for late 2022/2023 with Genoa and Bergamo.

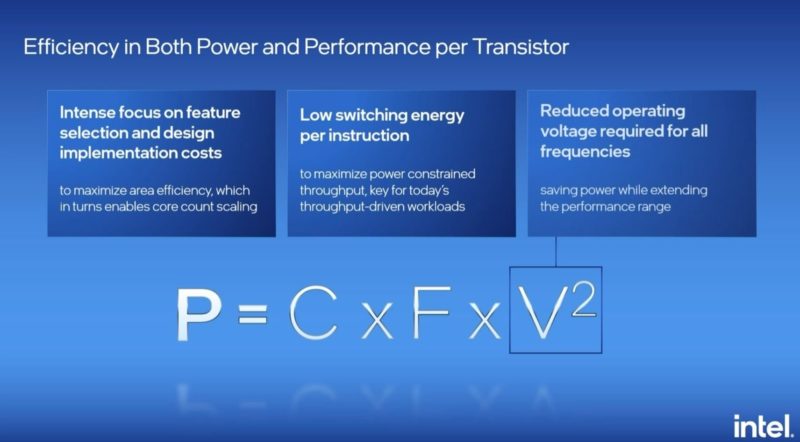

There is an important nuance to this as well. Intel has been hammered recently on PPA versus Arm. Arm chips like the Ampere Altra and Graviton2 are more like collections of E-cores. That, combined with being on TSMC and a process ahead of Intel has flipped the script. Intel could be less efficient than Arm, but when Intel had superior process technology and higher volumes, Arm could not compete. The Atom line, the lineage of the E-core, and specifically the Atom C2000 series Avoton/ Rangeley products effectively kept Arm at bay in the lower-end of the market for almost a decade (with the C3000 series coming later.)

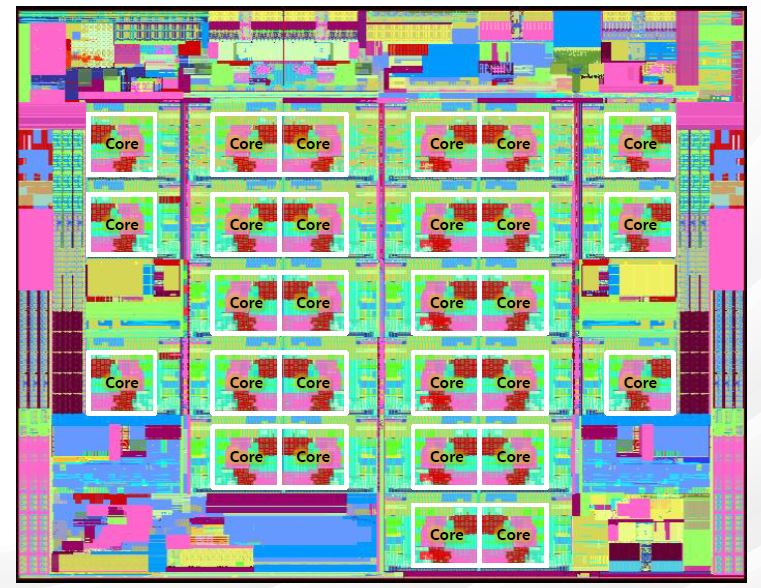

Assuming Intel can get even in terms of the process by the time these chips are launched, then the PPA discussion becomes very interesting. If Arm is 50% more efficient than x86, then that does not mean it can necessarily fit 50% more cores. Many make this incorrect assumption. The amount of die area dedicated to caches, PCIe/CXL I/O, memory interfaces, and so forth is very large. The above image shows how much is core versus everything else in a chip.

As a result, the E-core Xeon has a real chance of getting Intel a direct competitor to the Arm solutions on the market, especially since it is now slated for Intel 3 a new process node.

Intel Updates P-Core Roadmap with Emerald Rapids and Granite Rapids

Next up on the P-core side, we get an update on the Intel 7 Sapphire Rapids. Most of this we have already seen. Intel has some really cool technologies, beyond HBM, that are going in SPR, we just cannot discuss them yet. Intel said that initial shipments will be this quarter (Q1 2022) and specifically initial SKUs to initial customers in March 2022.

Next is Emerald Rapids. This is what we covered in the Intel AXG on Falcon Shores Arctic Sound-M and Future Products at Investor Meeting 2022 piece. Here it was called “Xeon Next” and “Xeon Next HBM” but this is the 2023 platform for Intel. Intel said it will be socket compatible with the Sapphire Rapids platform. Again, we cannot discuss which bridge is next after Ponte Vecchio.

Today Intel announced that Granite Rapids and Sierra Forest will be on Intel 3.

Final Words

Overall, we are very excited about Sierra Forest. This is the type of chip that would be ideal for a lot of what we do, even down to web hosting. Now we just need those chips to get into the market.

Any details on whether full ECC DDR5 is supported (I am not talking about just the on-die ECC which is standard for DDR5, but the full thing as found on ECC DDR3 etc).

@B – Perhaps you could articulate it as cross-dice level ECC vs on-die ECC.

Those are Xeons and every Xeon line have supported ECC RAM of whatever form so far.

Any news on refreshed Intel D CPUs ?

Stay tuned to STH we will cover when we can.

E-cores for servers makes the most sense where the workload is fairly easy to parallelize out run concurrent tasks (like http requests) and you are not licensed per core. It’s also important to consider the CPU and it’s cores are only a small part of the cost for a whole system.

Pure E-core CPUs have a place where you don’t pay core licenses but maybe socket or server. I wonder if hybrid E and P core setups will also be limited to that, if Intel even makes that. It could make a lot of sense for virtualization, or containers. If most threads are light weight, move the heavy ones to P cores, or VMs/containers running expensive per core license software.

Sierra Forest is very interesting and seems to leverage perhaps the most interesting Intel core of 2022 – the E cores.

The problem is timing/delays. In 2022 this would be a transformative product. Very interesting against Bergamo.

As a 2024 product won’t it be going up against Turin and its various iterations up and down the stack? Turin should pack a huge number of cores and probably some serious power efficiency in certain SKUs….?