At ISC 2022, Intel discussed its near, and a bit further in the future plans for the HPC space. The company started talking more about the generations beyond the 2022 generation in terms of Rialto Bridge and Falcon Shores. These are products that we heard about, conceptually, at SC21, but we now have more information about them.

This is being done live during the keynote in Hamburg so please excuse typos.

Intel ISC 2022 Keynote Rialto Bridge and Falcon Shores

Only 23% of data center power is being used for compute in data centers currently. Power efficiency is a big deal, especially in Europe where ISC is being held. 3-5x increased energy cost in EU in the last year. So part of moving toward Zettascale is not just getting faster chips, but also figuring out new ways of getting more performance in a similar power envelope. Today’s modern systems like Frontier are already in the 30MW range.

We covered Intel’s new chips for its Argonne Aurora supercomputer recently as part of our Intel Vision 2022 recap video.

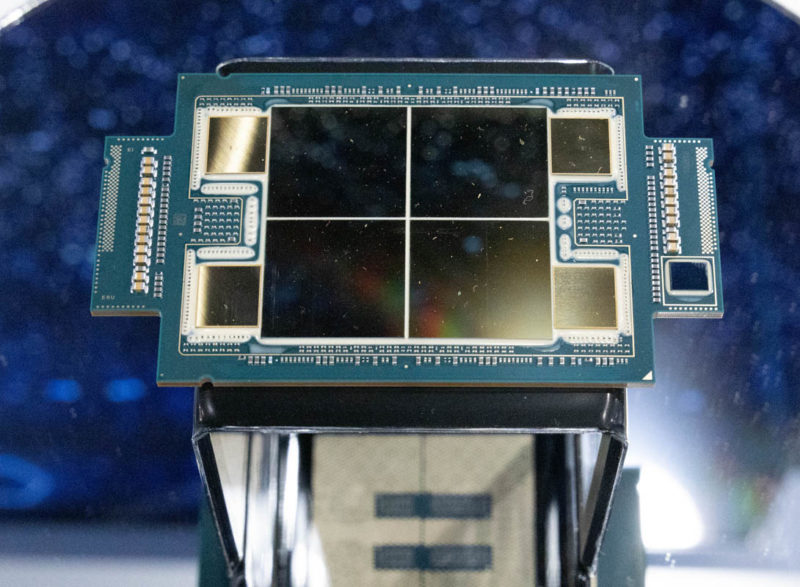

As part of that, we recently saw the 4th Generation Intel Xeon Scalable Processors with High Bandwidth Memory (HBM) at Intel Vision 2022.

The next generation of chips is the Emerald Rapids 5th Generation Xeon Scalable product that will follow Sapphire Rapids. Looking beyond 2023, next will be Falcon Shores:

This will combine x86 and Xe cores and be a chiplet-based solution that can be more configurable. Perhaps the way to think about this is more of like scaling up something akin to a M1 Ultra where the CPU and GPU are integrated with high-speed memory. Then, the idea is scaling out many of these XPUs. As some reference, others like AMD and NVIDIA are also working on similar solutions, but we should have a host of other really interesting technologies with this generation.

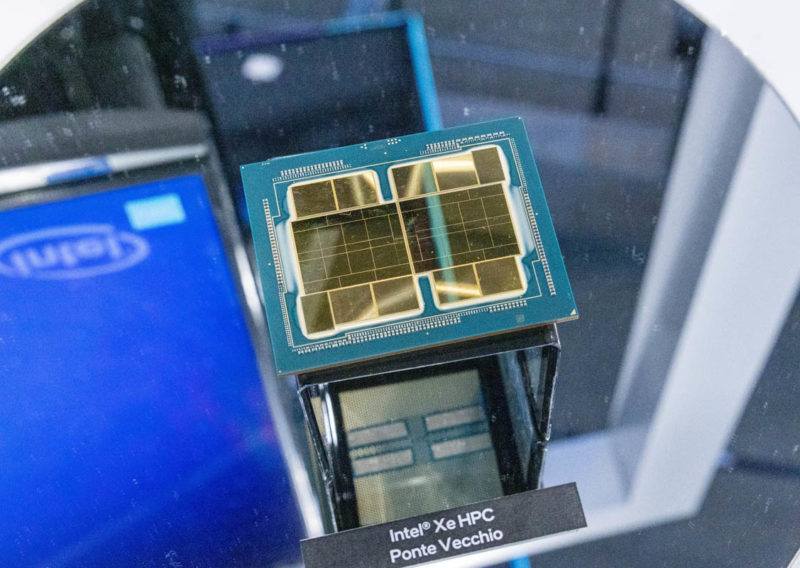

On the GPU side, we also recently saw the Ponte Vecchio chip:

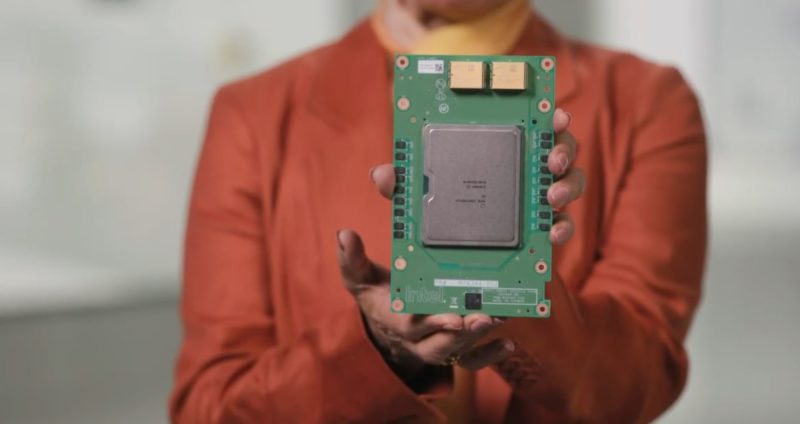

And card:

The next Xe HPC GPU is the Rialto Bridge. This is the next Italian bridge line of processors. The way to think about this is as a performance upgrade that is a generational improvement.

Falcon Shores is an extension beyond the Italian bridges so that is when the solution really changes. Also, from what I understand, the future bridges are not just from Italy and not necessarily physical historical bridges.

If you want to learn more about the next generations and concepts beyond 2022, check out the path to Zettascale video from SC21:

Thus far, Intel is continuing along with the roadmap we first heard about six months ago on the path to Zettascale.

Final Words

Overall, we are still waiting for Ponte Vecchio and Sapphire Rapids with HBM to go into Aurora, hopefully for the SC22 Top500 list. After this generation is out, then we will get to the incremental 2023 generation before eventually moving onto the more radical changes.

Falcon Shores: “Perhaps the way to think about this is more of like scaling up something akin to a M1 Ultra where the CPU and GPU are integrated with high-speed memory.” This does remind me of the recent order we made at home for an M1 Studio Ultra for my wife’s video chores…But I think back to all those DIMM slots in the thousands of servers I have wrangled over the past few decades. Ordering them often half populated with DIMMs so that I could add RAM over the years if a given server got more use. Can’t do that in this case (or in the case of ordering said Studio with 64-GB versus the 128-GB RAM max)…Hmmm.

Falcon Shores chiplet flexibility: At 1st blush, this would portend for many SKUs.

I ran across an article on phoronix that said the user mode interrupt feature coming in SPR leads to a 9x performance increase in IPC.

That feature combines with their user mode pause/wait capability, which can go to a low power state that doesn’t involve any spinning.

I haven’t seen it discussed much, but seems like this could also be used to improve their current thread scheduling in oneAPI/dpc++ … so maybe something to look forward to in oneAPI 2.0.