What do you get when you combine what has traditionally been a high-end desktop line of cores with what has been a traditionally lower-end of cores? One answer is you get something like the Arm big.LITTLE architecture. Previously Intel primarily focused on downclocking big cores, but with Alder Lake, it is bringing about a hybrid core approach with larger and smaller cores on the same CPU.

Intel Alder Lake Hybrid Processor at Hot Chips 33

Intel Alder Lake incorporates new cores and new technologies to build a more efficient client computing chip.

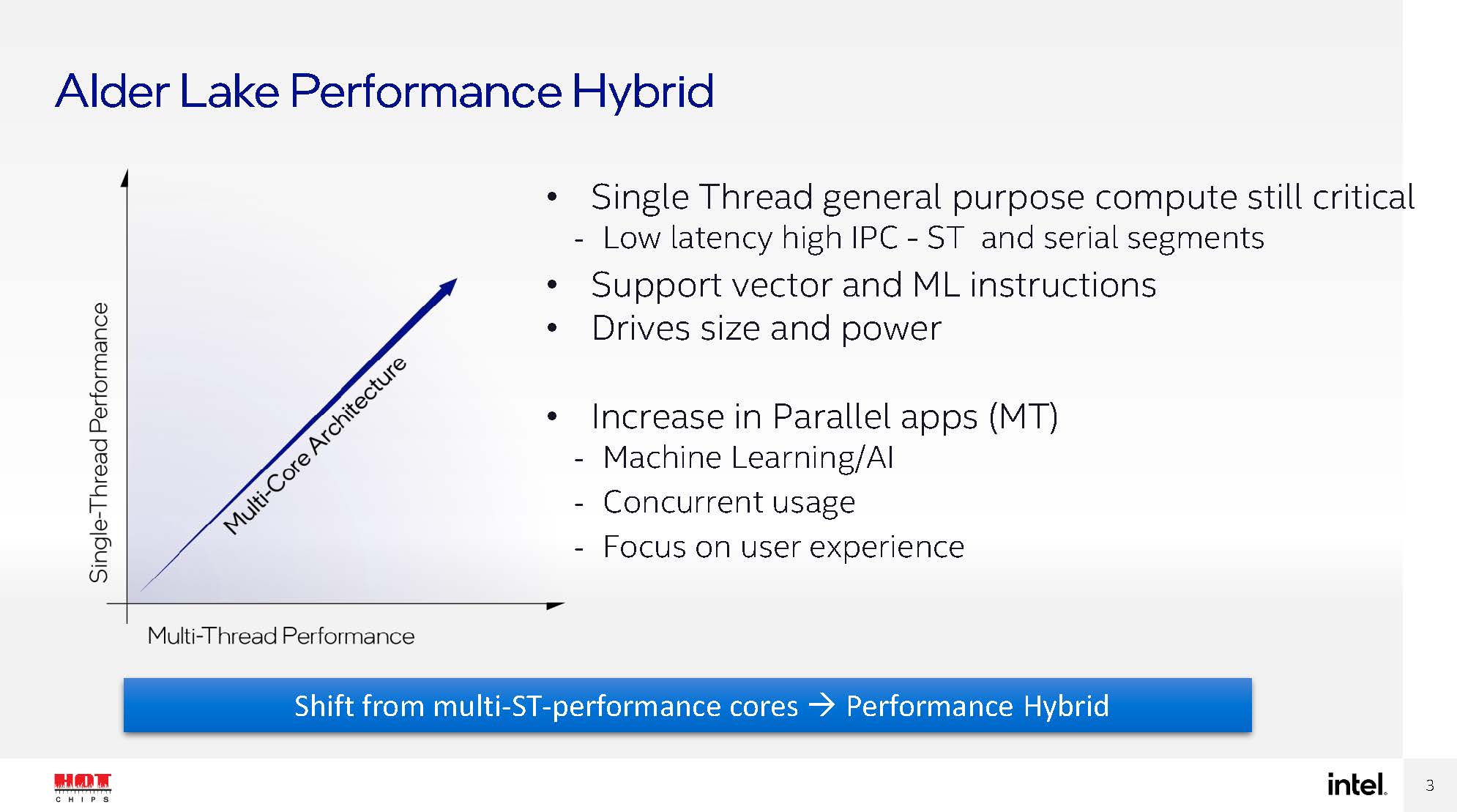

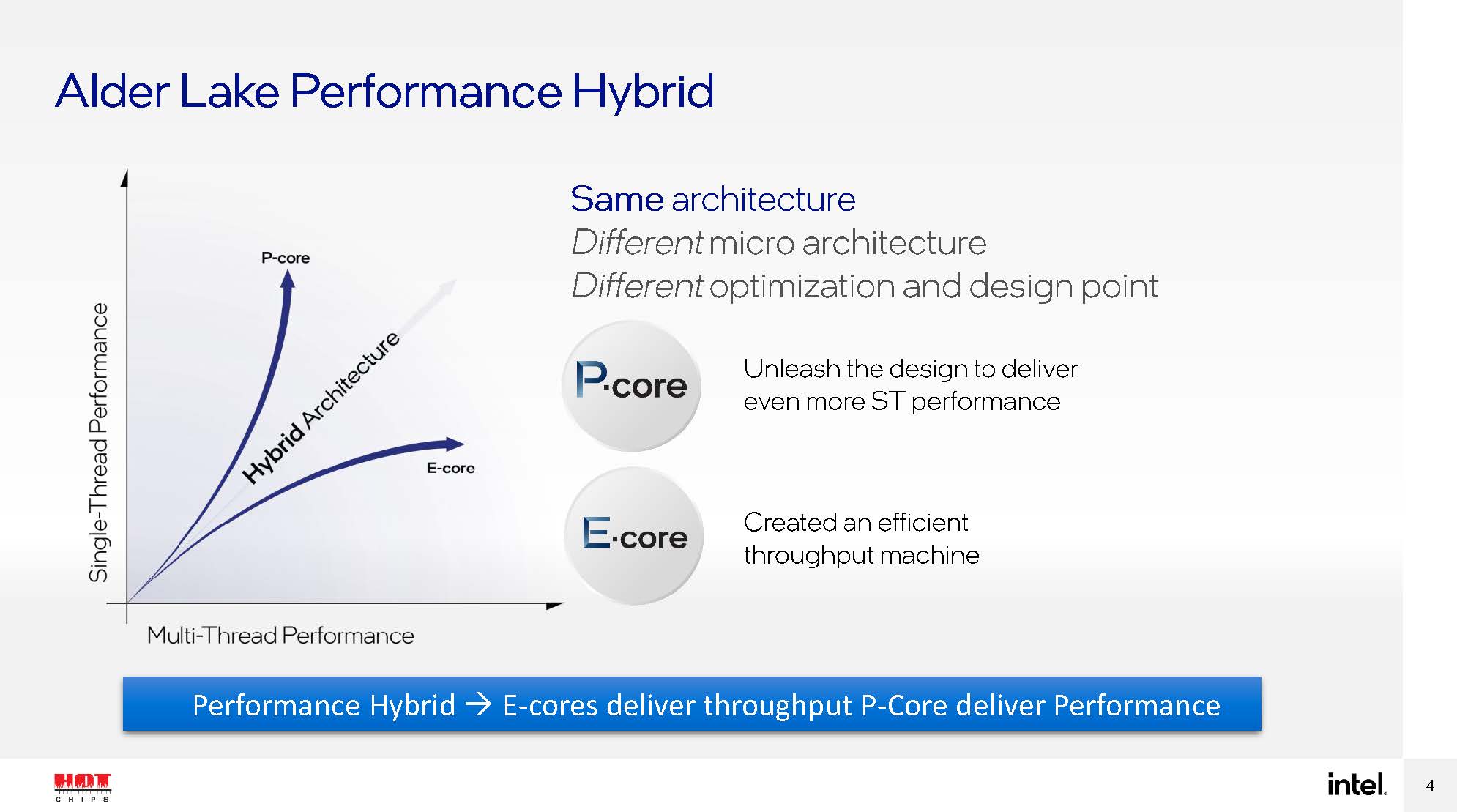

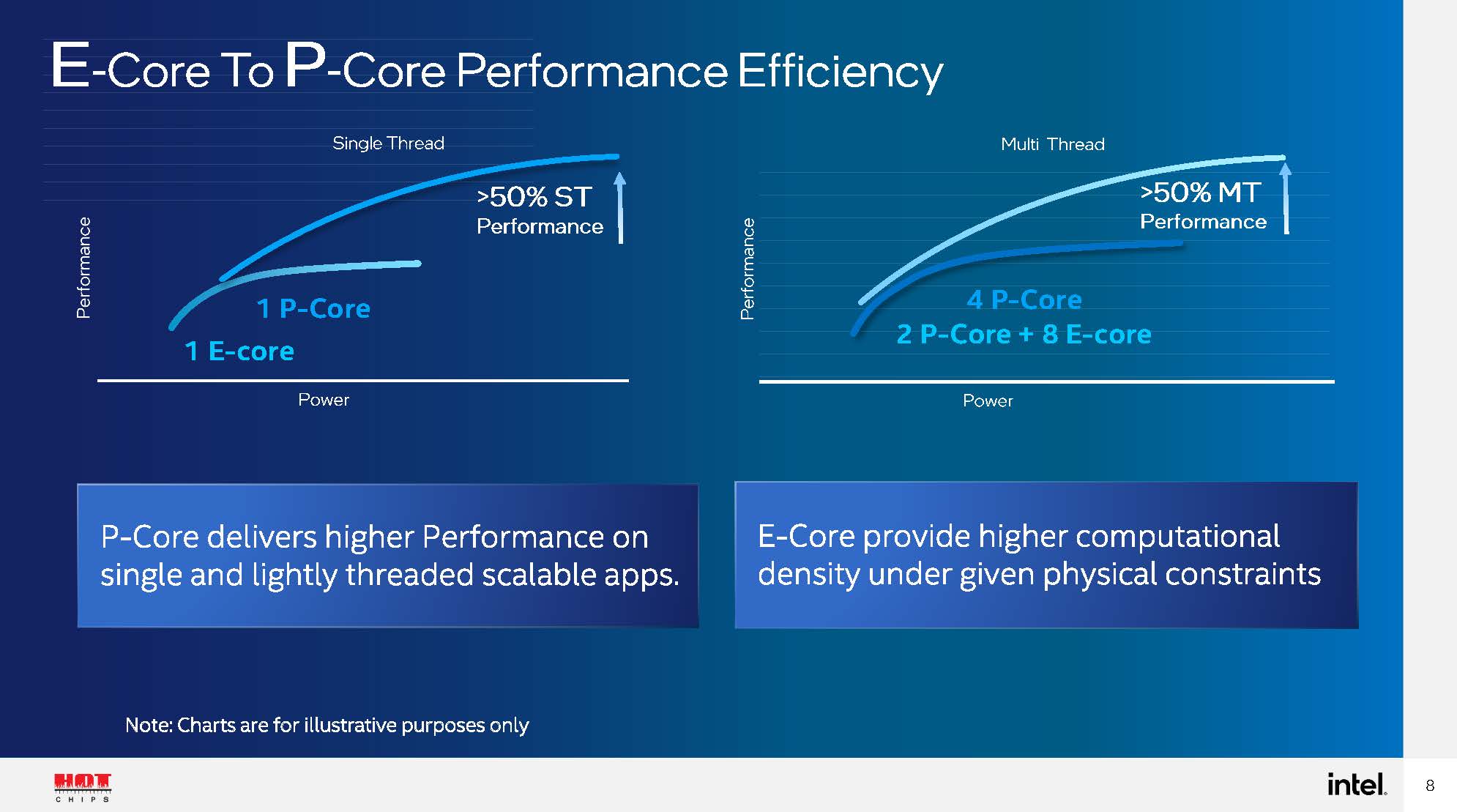

Perhaps the biggest innovation is the inclusion of two different types of cores. The goal is to take advantage of the performance one can get with the high-performance cores for single-threaded applications and then scale out to higher efficiency cores for threads that need less performance.

At STH, we are going to have a deep dive on the P and E cores later this week. For now, assume the P core is the performance core designed for maximum per-thread performance. Versions of the P core will be used by Alder Lake for client devices but also Sapphire Rapids on the Xeon side for servers. The E cores one can think of as highly upgraded versions of the older Atom line.

In this generation, the “E” or efficient cores are designed for adding more cores to a design at a smaller power and area footprint. As a result, combining these cores means one can distribute work among the different core types and get power and performance gains.

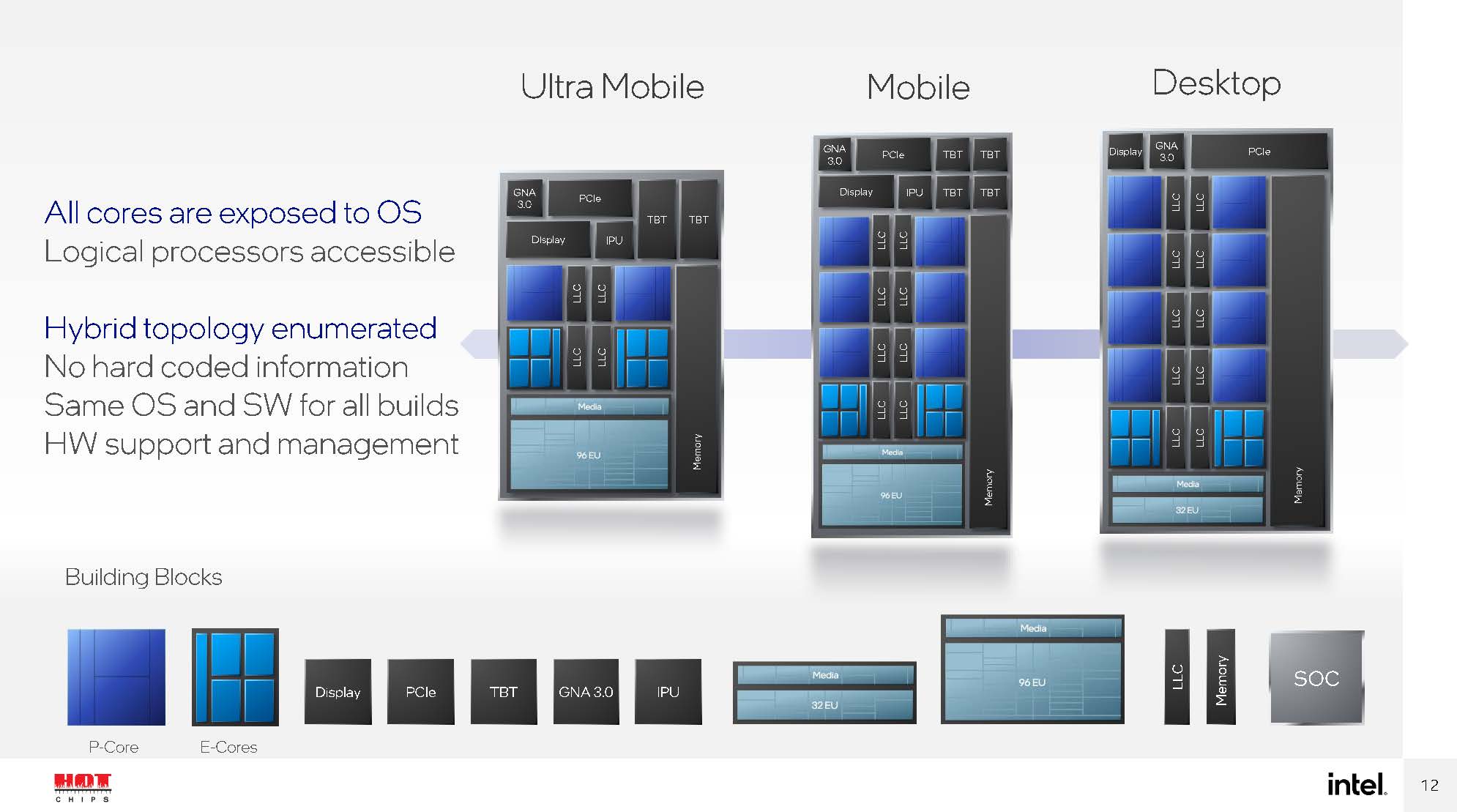

Alder Lake is designed from a number of building blocks. These include the P and E cores but also GPU EU’s (although Intel at Architecture day said it wanted to get away from using EUs.) There are also various controllers, caches and so forth that can be added and combined to make BGA to LGA 1700 socketed desktop parts.

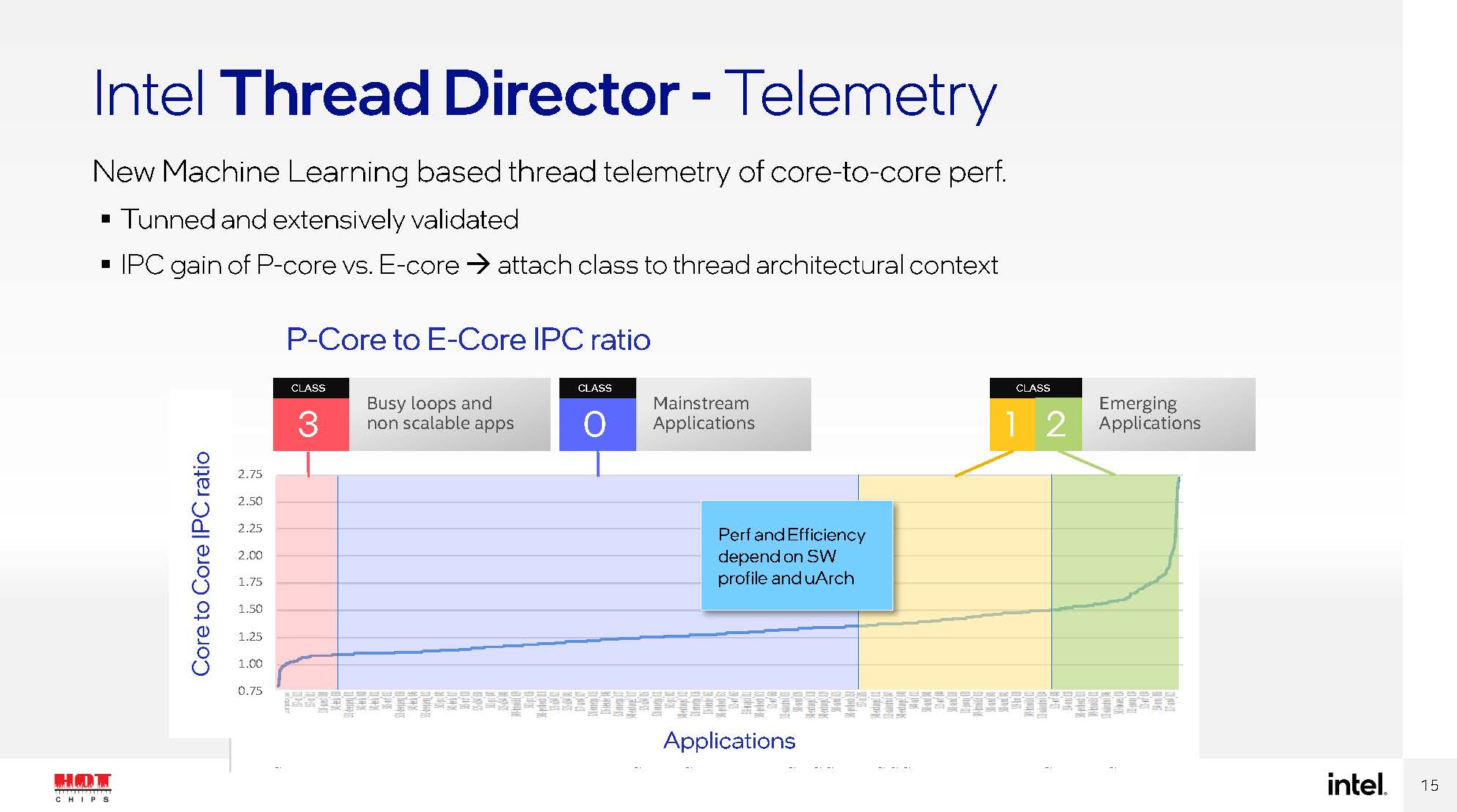

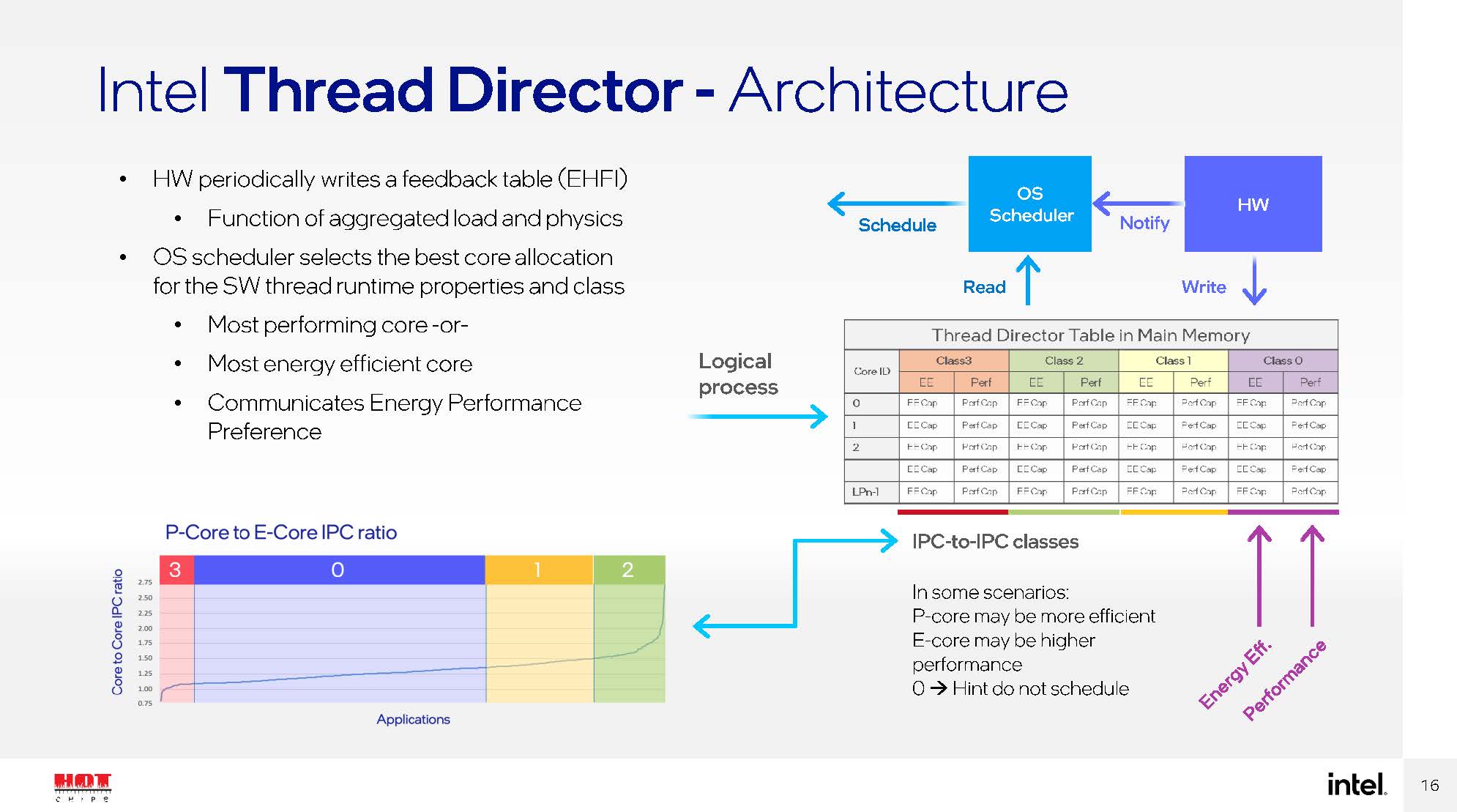

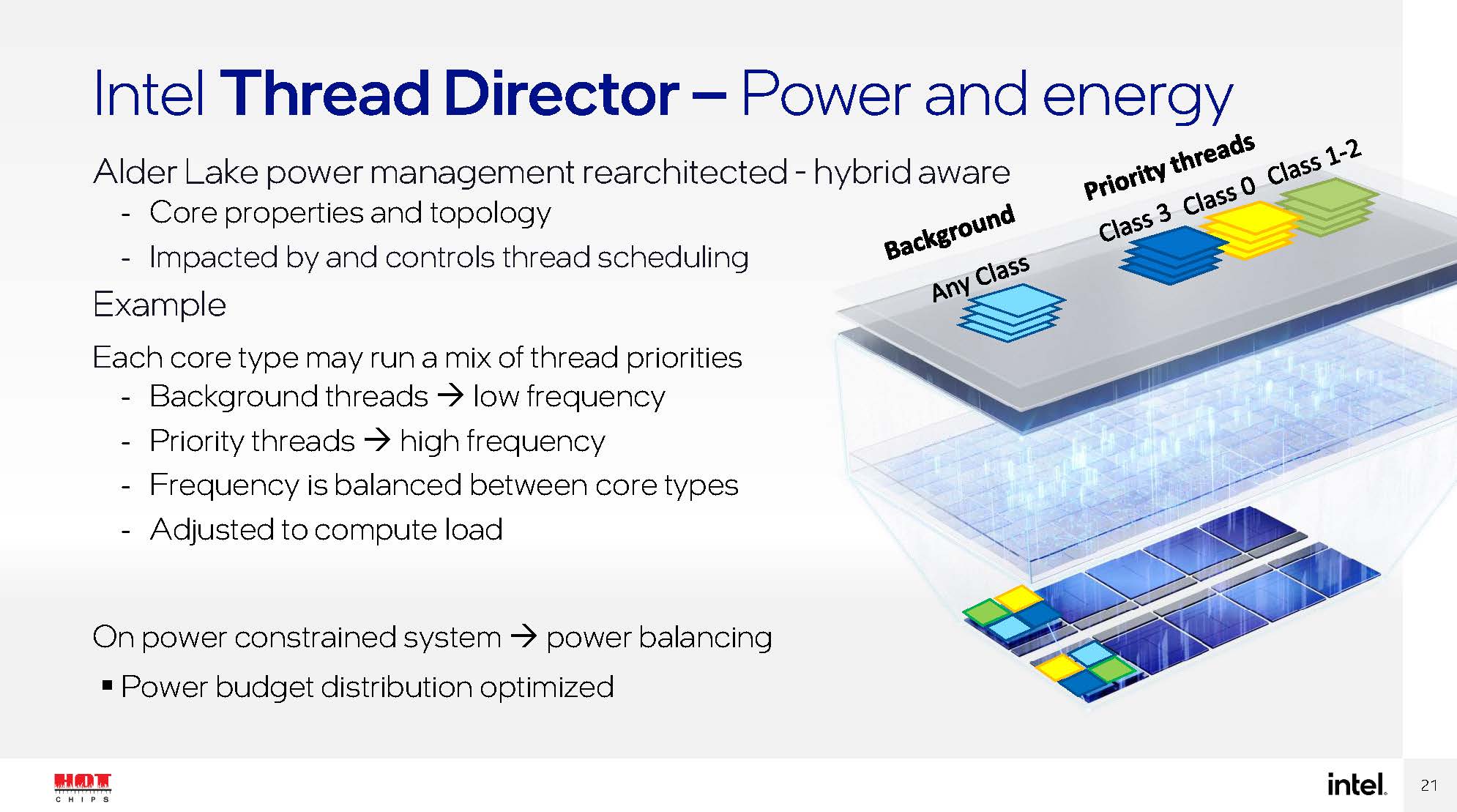

Putting the solution together creates an important challenge. How will threads find their ways onto cores? Intel Thread Director is the technology that helps decide how threads are scheduled on the diverse set of cores.

Part of this is that Intel needs to decide whether a thread needs the single-thread performance of the P core or the efficient nature of the E core.

Intel is not using a solution that simply hides the lower power cores from the OS and then offloads work to those E cores transparently. Instead, all cores are exposed to the OS, and Intel Thread Director helps provide information and inputs to the process.

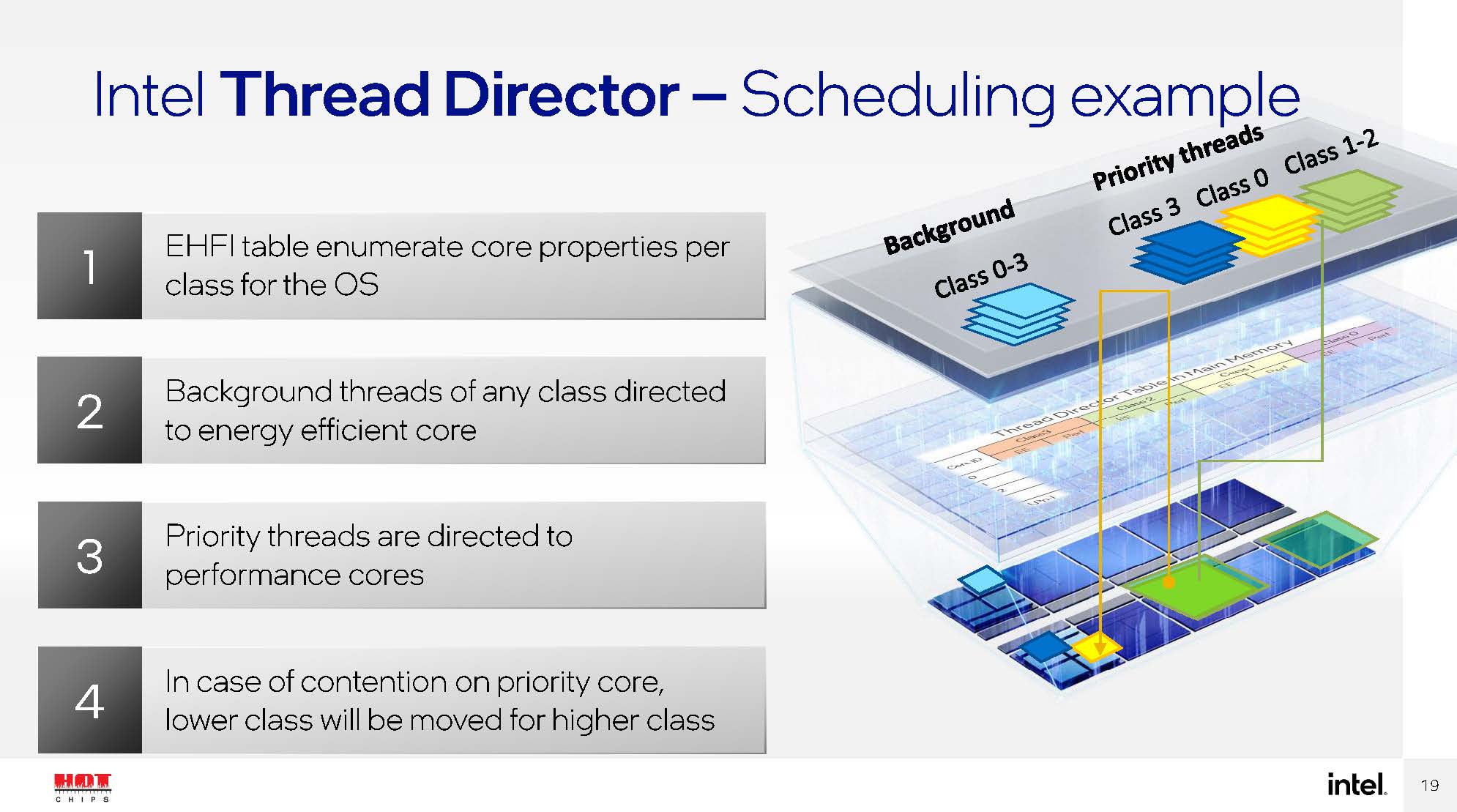

Here is an example Intel gave during its talk around how Thread Director works.

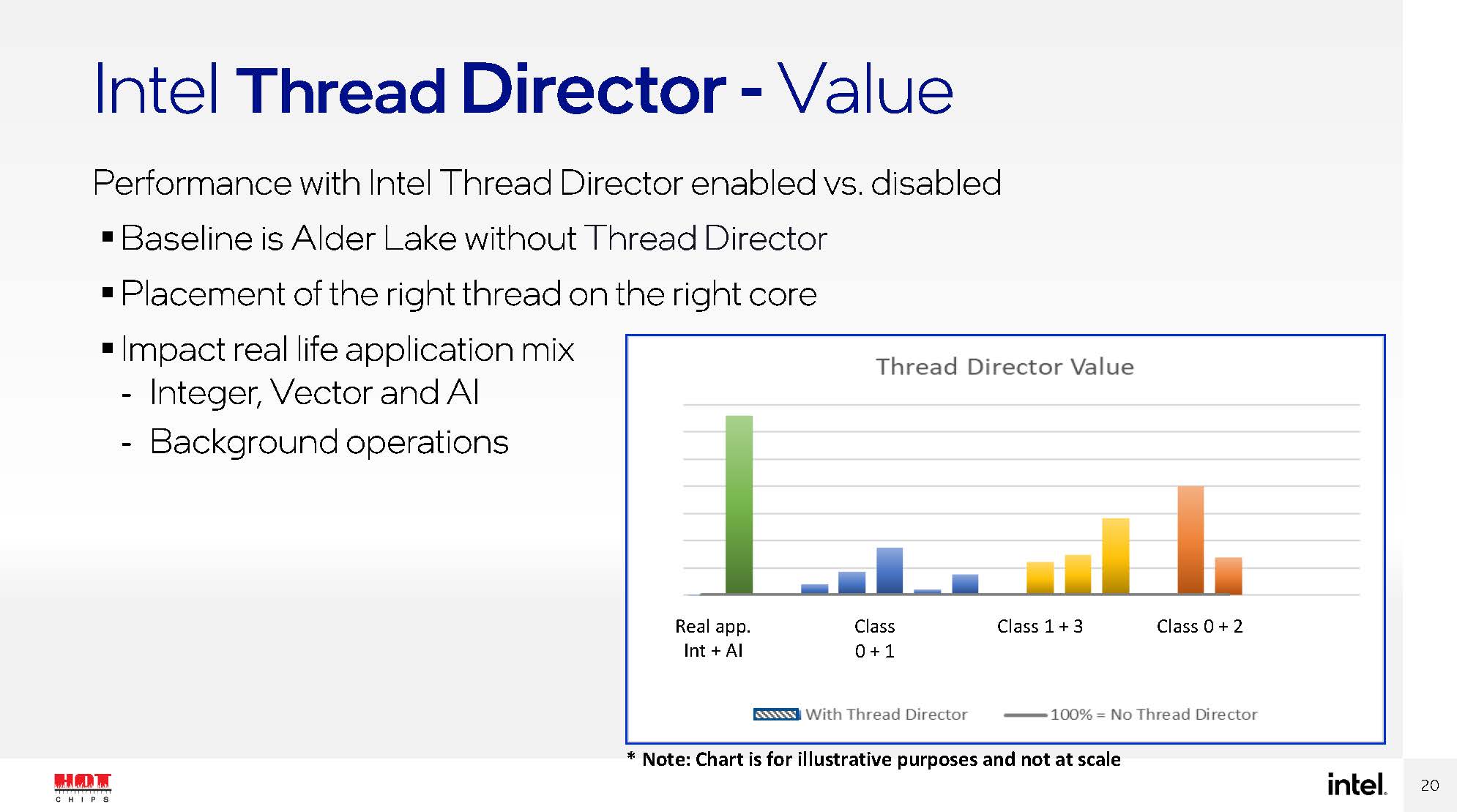

Intel says that Thread Director increases performance versus Alder Lake without it. In the talk, Intel said these are not official and not to scale. There is no scale so for this we can just say that Intel says it is better with Thread Director than without.

By scheduling threads that can run on lower-power E cores, Intel says it lowers overall power consumption while also increasing performance.

Final Words

We are going to have more on the P and E cores. I know that is something that Patrick is working on but I do not think he is done yet.

The optimal simplest easiest to program CPU design is all same cores. We did not need bloody ML trained schedulers before this Intel fab debacle, ever. How long before the AI geys put of datr anyway, as software titles change? Context switching is not slow and is not an energy suck. Intel’s little cores will still context switch.

Remove all the handwaving and snow job and what you are left with is two things:

1. Intel can not manufacture it’s headline core design anymore and have it work inside a reasonable power envelope.

2. Atom is still slow.

This is not Intel moving the state of the art forward. This is Intel in full damage control mode and to heck with the fallout.

“…before the AI gets out of date…”

Who cares Intel’s future is hugely secure they landed a huge government contract to supply processors Inthe future for the defense department as part of the program to keep those made in America and not overseas and then intel buys up the biggest block of tscm 3 nm .. I don’t think Intel.is worried one bit