At Hot Chips 32 (2020) Intel was very focused on its 10nm product updates. We already covered the Intel Ice Lake-SP Next-Gen Xeon Architecture at HC32, and there were some Intel Xe disclosures similar to what we saw last week at Architecture Day 2020. One of the other big products getting some time is the Intel Agilex family of 10nm FPGAs. We are going to focus on some of the higher-level family details in our coverage here. Please note, we are doing this live at Hot Chips 32, so this piece will be updated.

Intel Agilex Family Hot Chips 32 Update

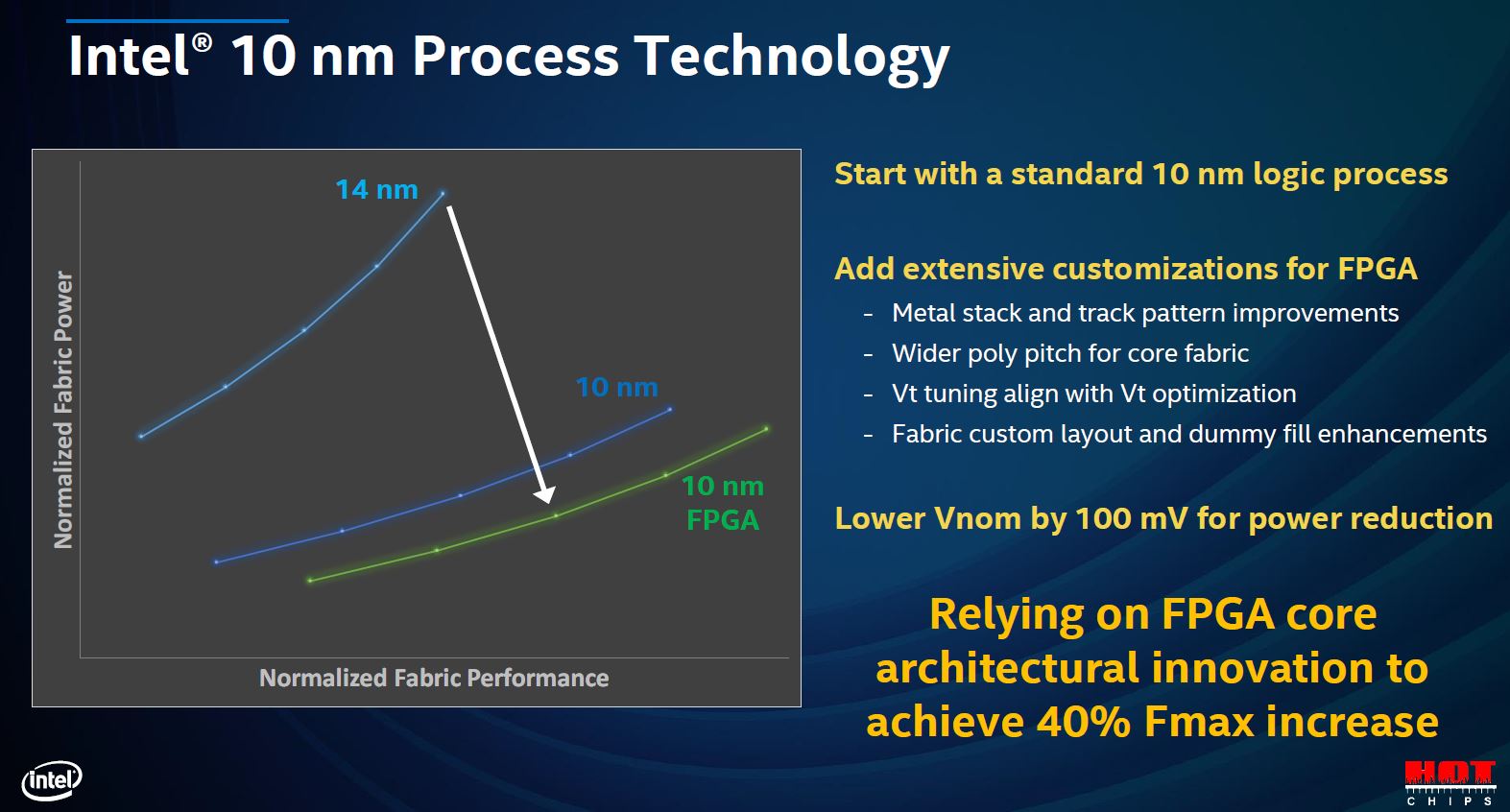

Intel just coined 10nm SuperFin and Enhanced SuperFin but Agilex was one of the earliest 10nm products. We have asked at HC32 which process it is on. Update: Intel answered my question at HC32. Intel is using 10nm SuperFin with FPGA specific enhancements.

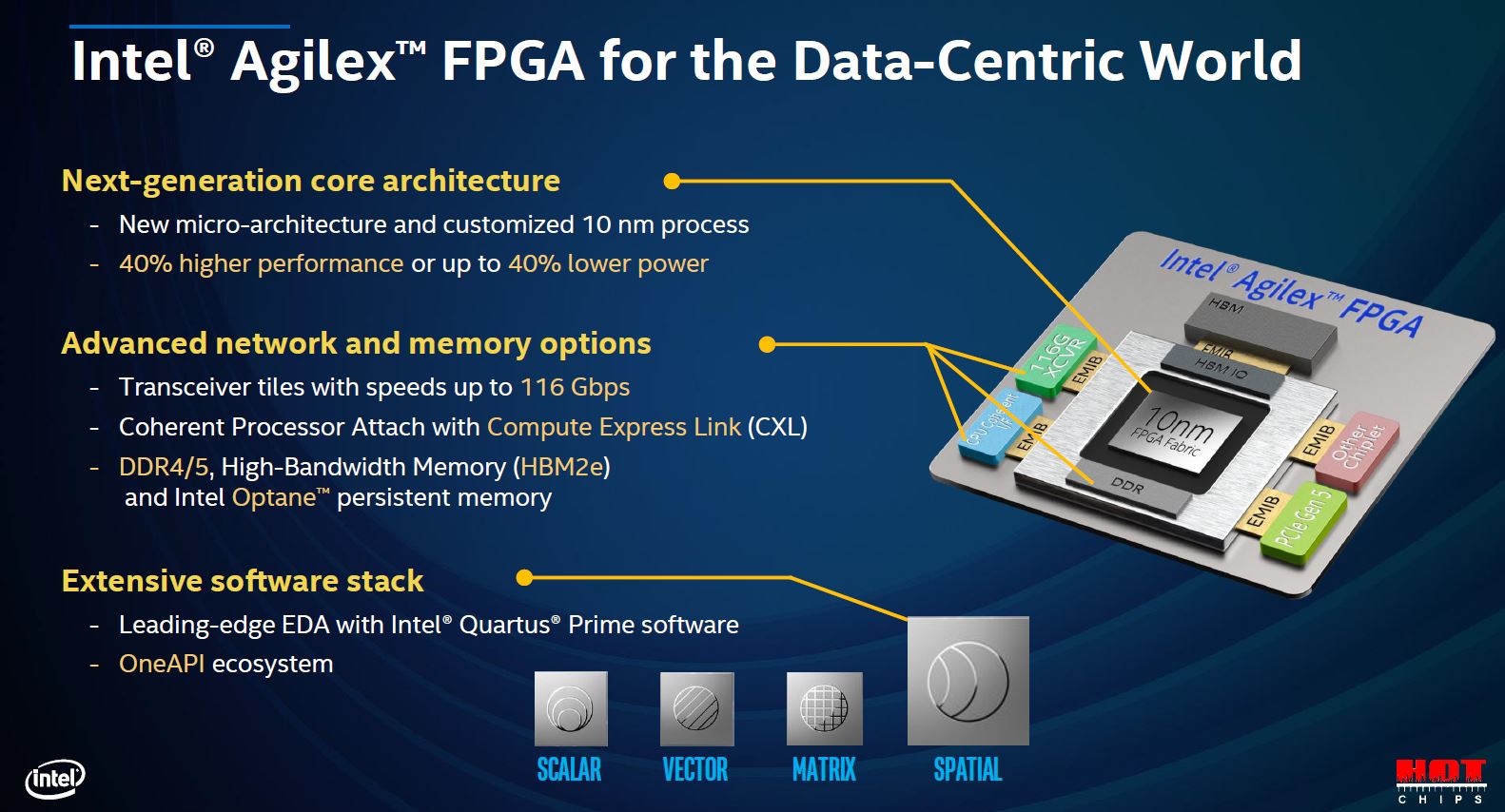

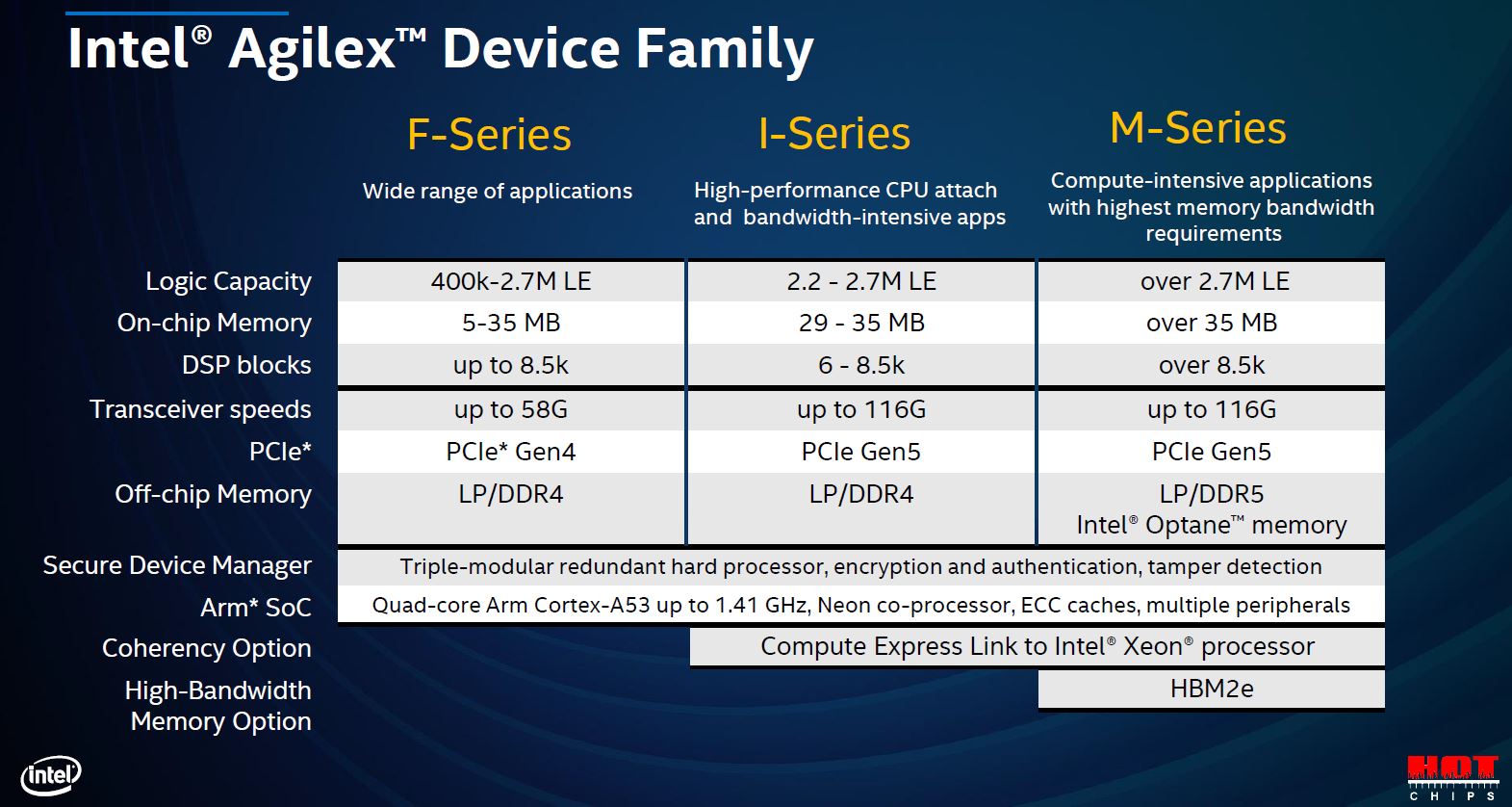

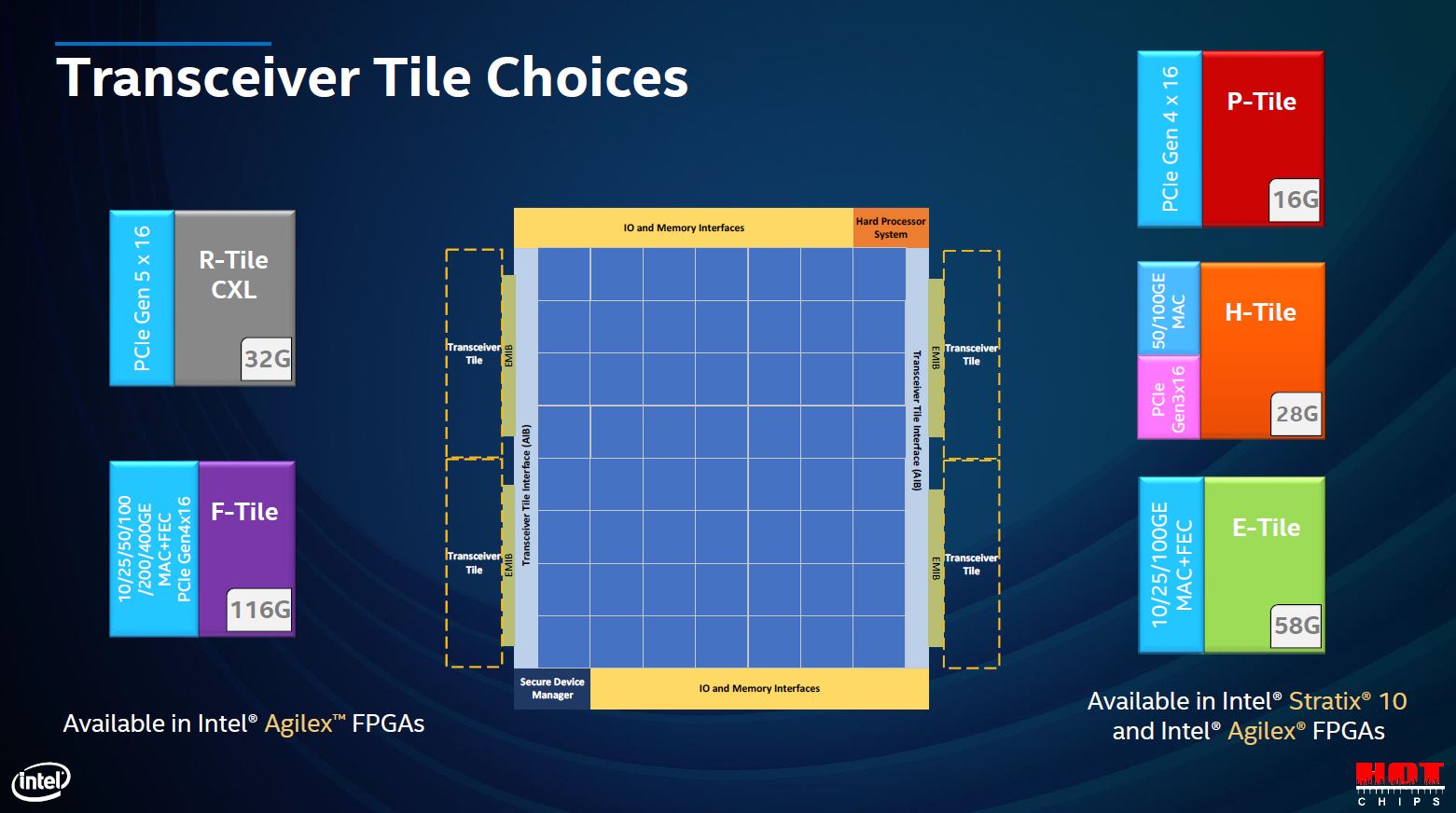

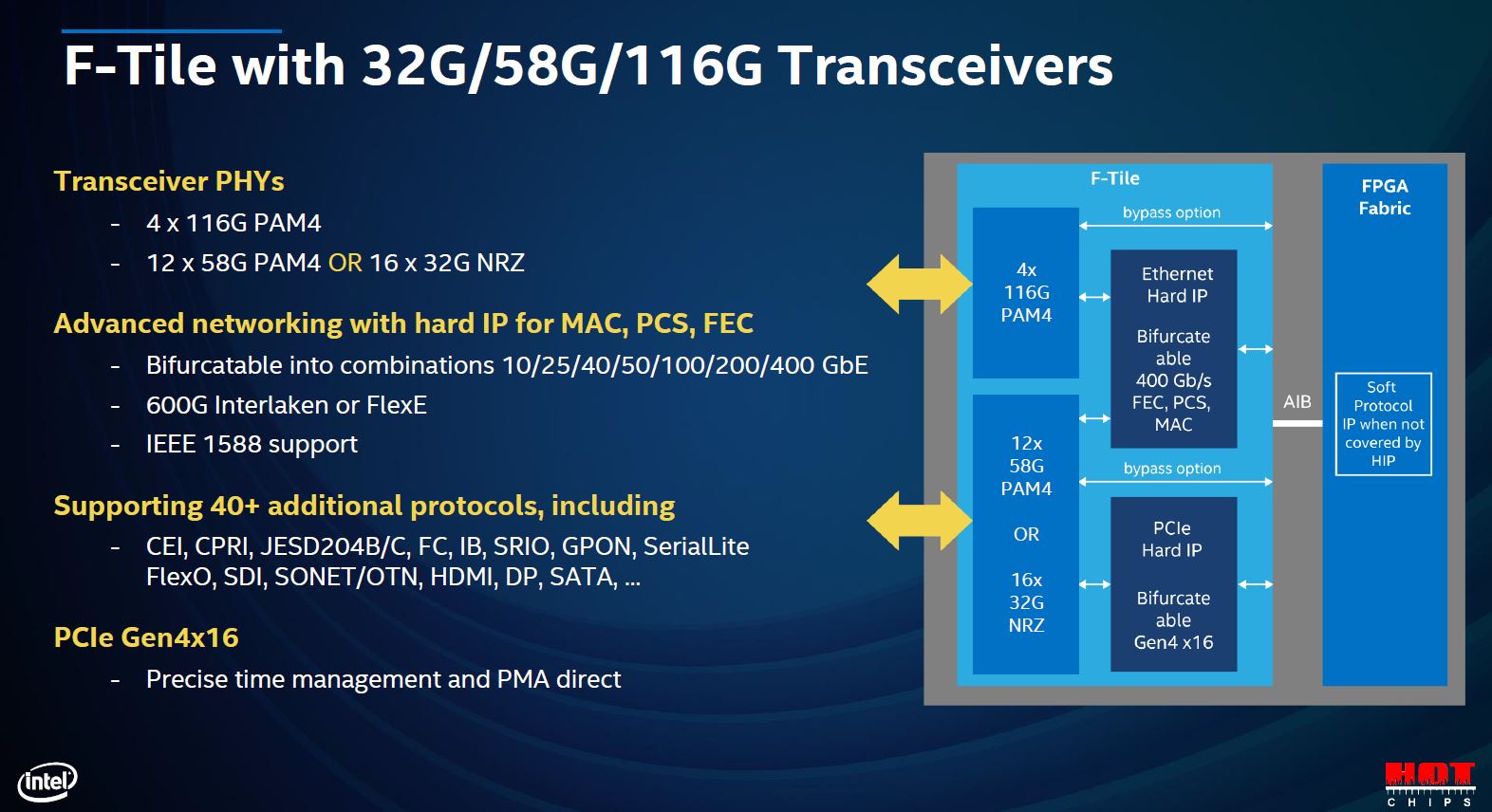

Agilex has a number of different families that scale with I/O. Intel had told us that we would see generations of connectivity beyond 58G transceivers and PCIe Gen4. It is now going into more detail.

We saw some of the Optane enabled FPGAs at Intel’s Seoul storage event last year where they covered the Intel Optane DC Persistent Memory Module Roadmap. Here is that test vehicle with the older generation Stratix 10.

Part of Intel’s strategy is to proliferate the technology across its silicon portfolio. Next, let us get into how these are built.

Intel Agilex Building a Better FPGA

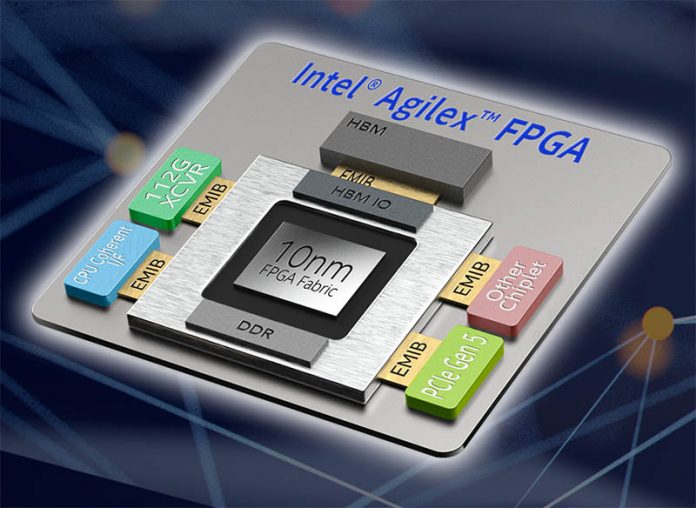

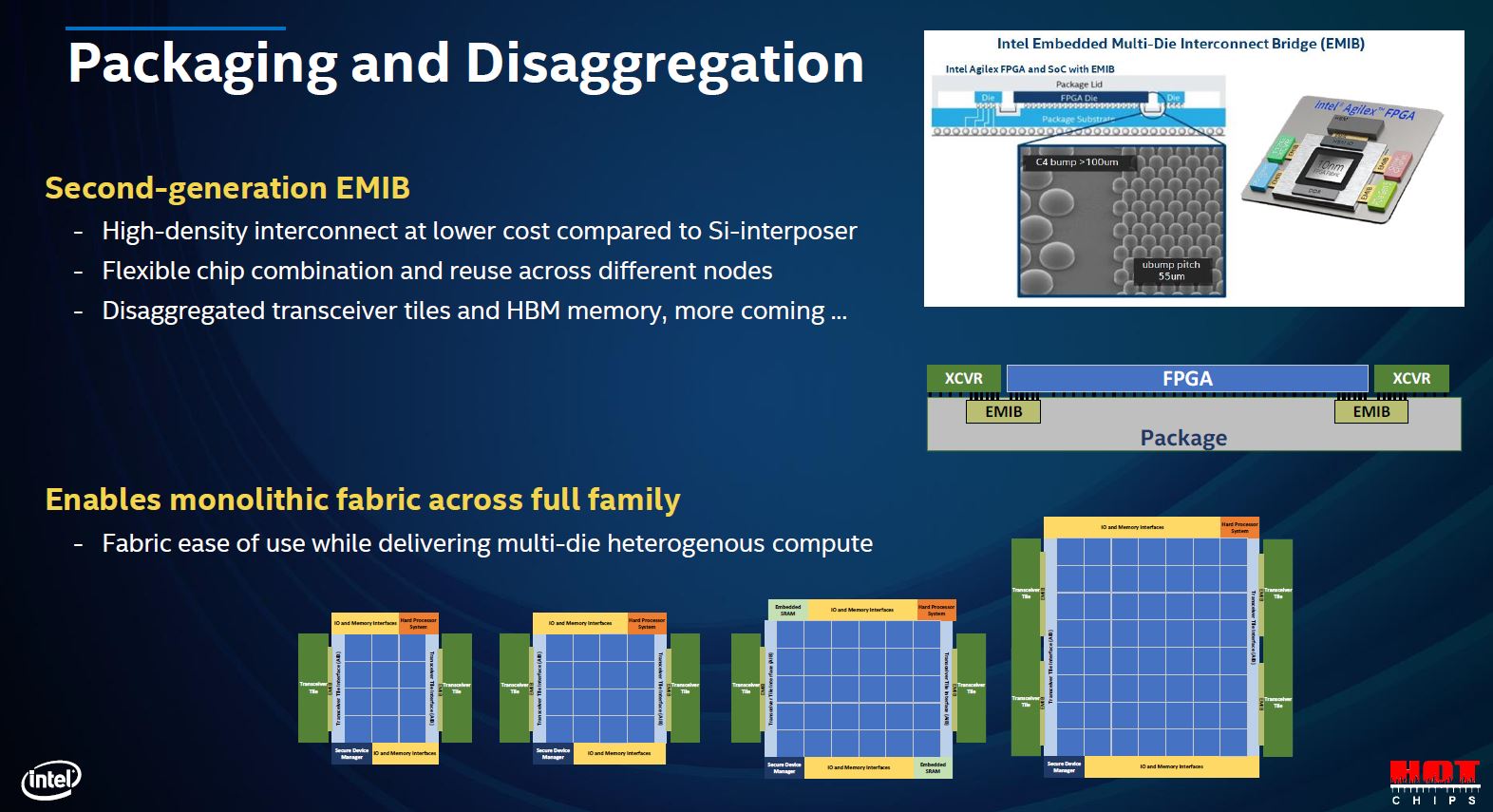

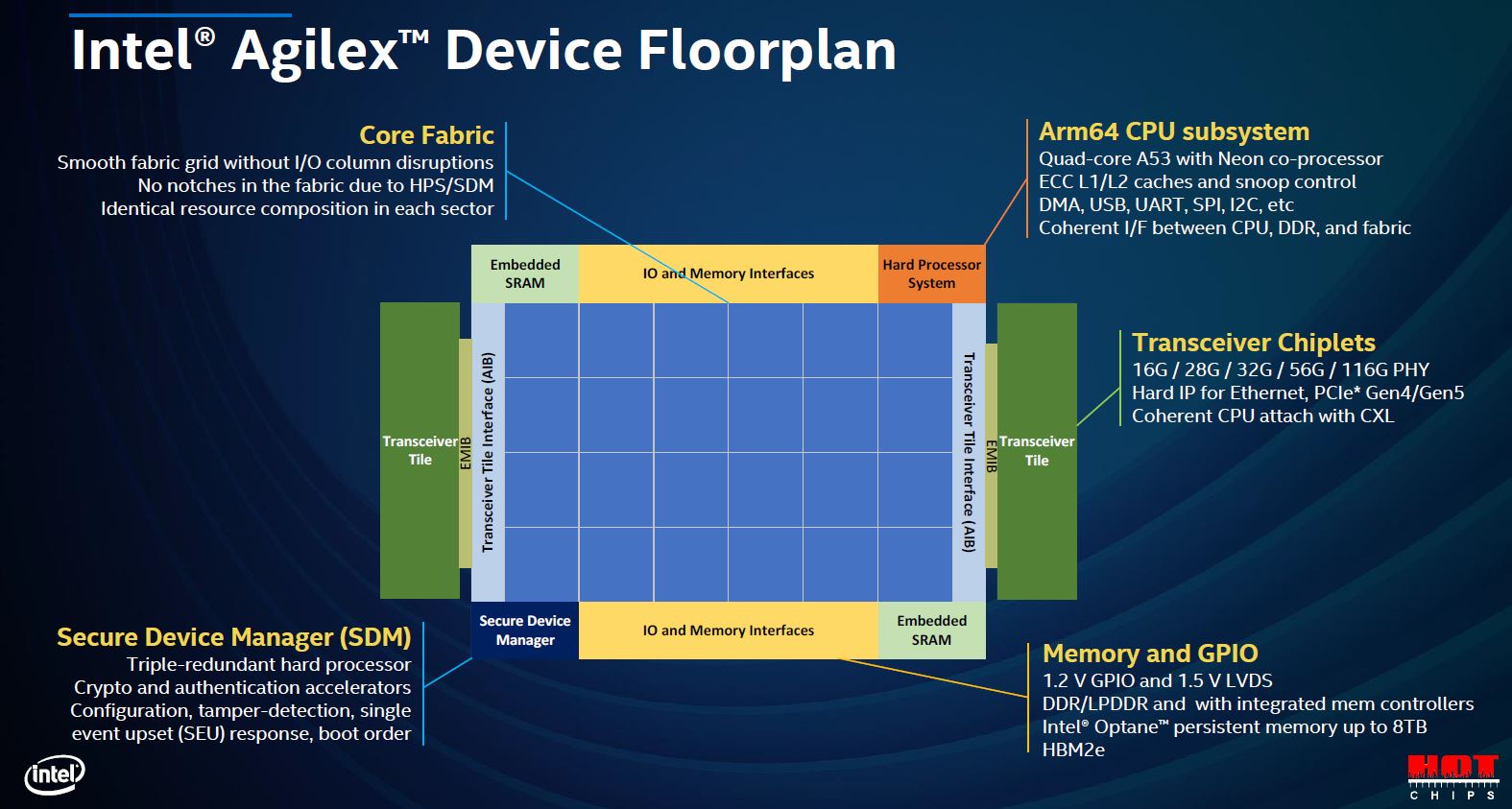

A big part of the Agilex value proposition is being able to integrate tiles to customize functionality. Traditionally, FPGAs have been part of highly customized engineered systems. Part of the vision is to be able to use a large programmable logic chip but then put transceivers, accelerators, and memory on the outer regions of the package to add hardened logic and functionality where needed.

When we look at the Intel Agilex solution, one can see the large programmable gate array. One can also see an interesting feature. Altera used Arm CPU cores in their FPGAs so this is a high-end Intel package that utilizes 64-bit Arm cores. As we discussed in An Arm Opportunity with Cloud Service Providers, Arm is already inside many accelerators even if it is not in as many primary sockets. This is a great example.

Intel is calling Agilex a 10nm process. Intel is saying that it is getting better than 10nm SuperFin process benefits from the scaling on FPGAs using a customized 10nm process. Larger Agilex chips are large and complex which makes them scale well with process node transitions. The harder part is often the I/O transition.

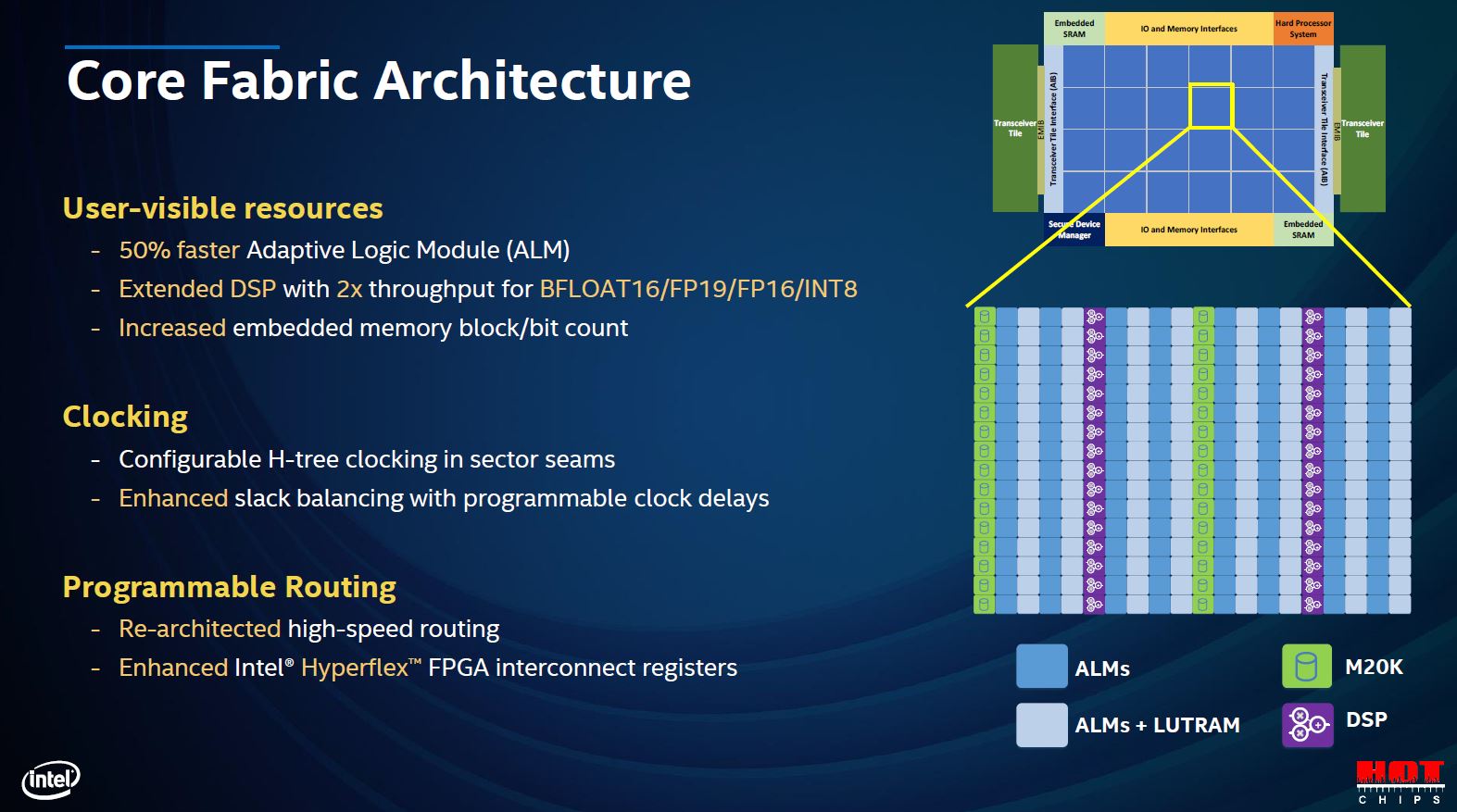

Intel as part of its core fabric has its Adaptive Logic Modules (ALMs), as well as embedded memory, and DSP segments designed to accelerate bfloat16, and INT8 for AI workloads among other uses.

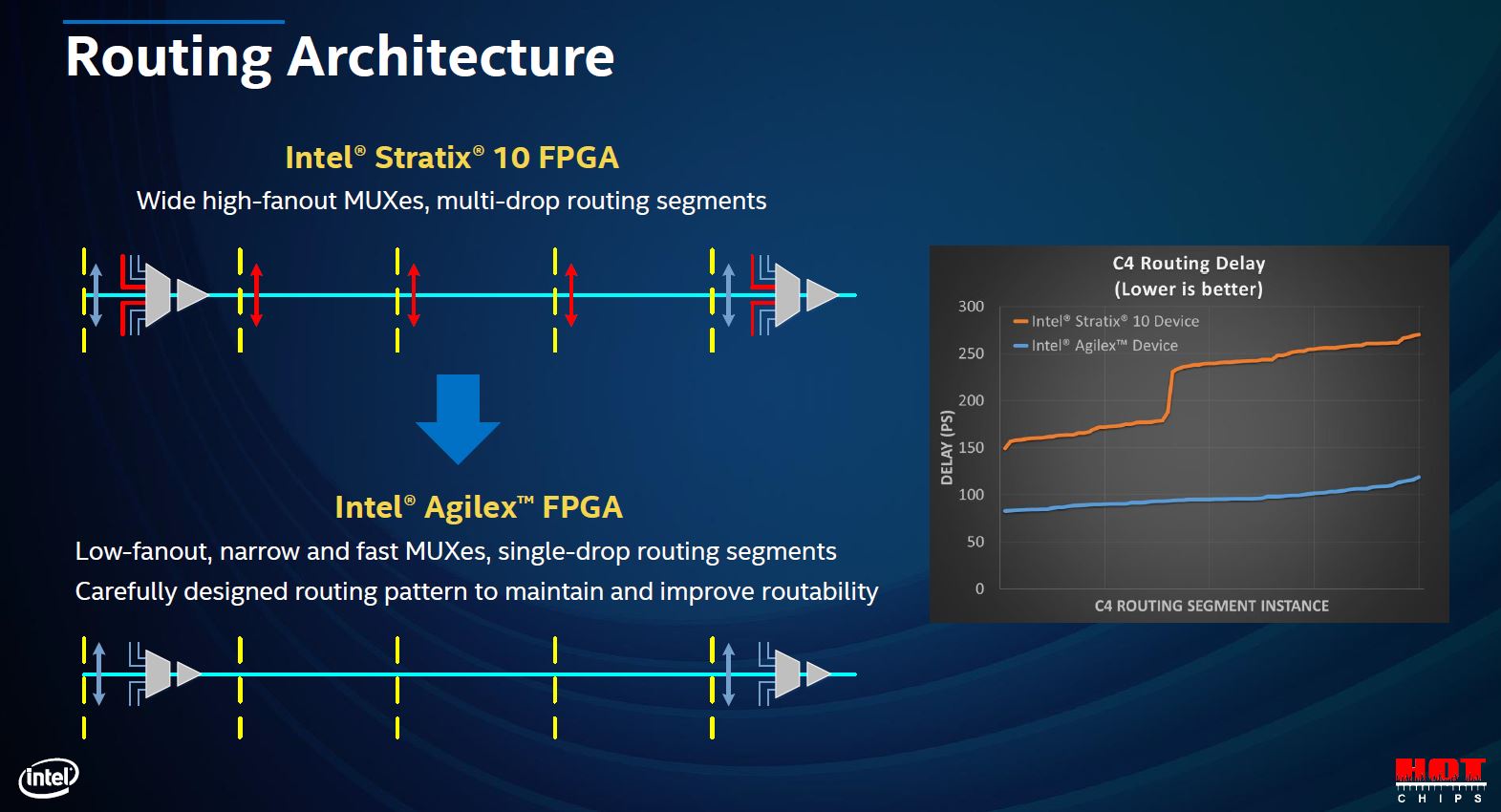

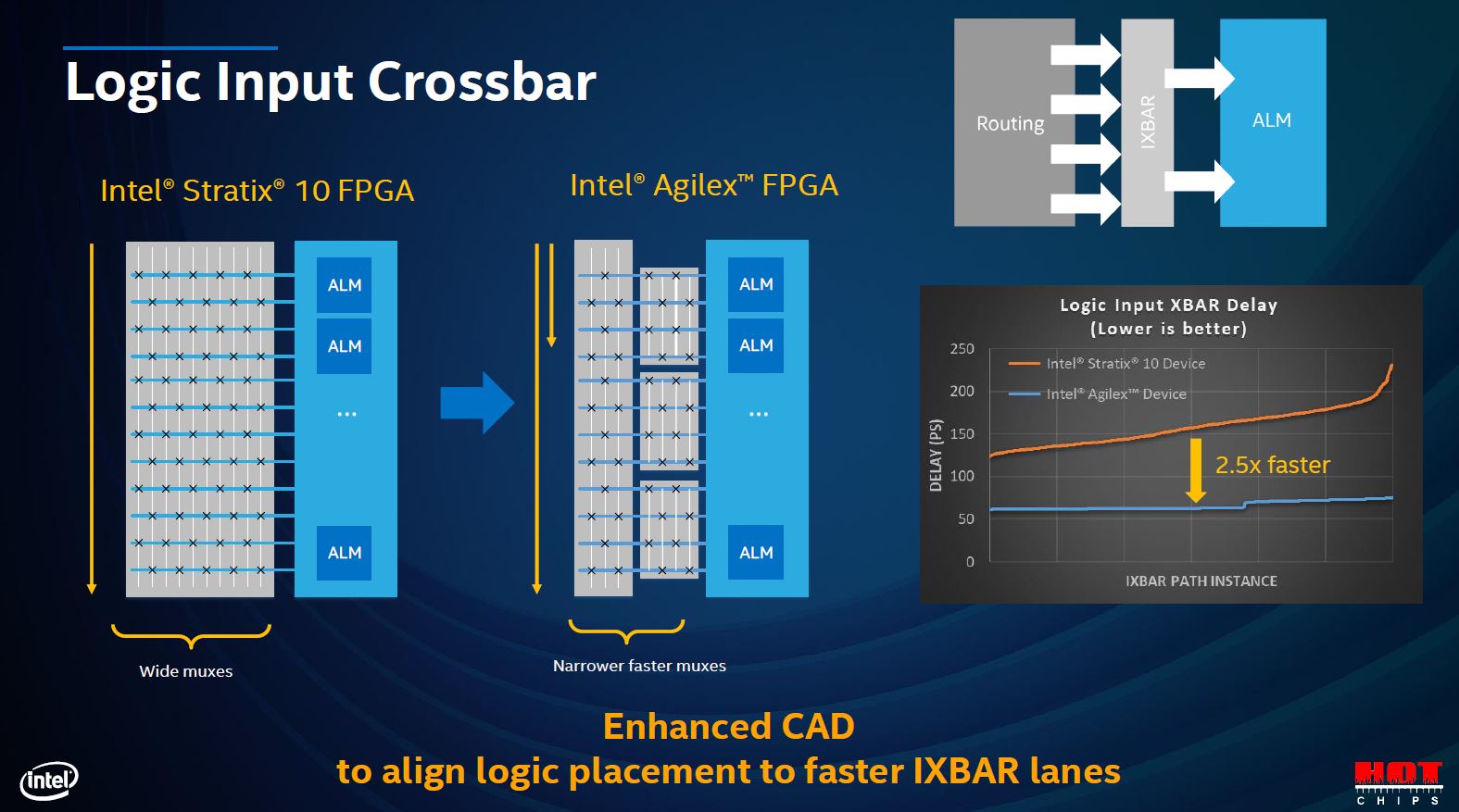

With each generation of FPGAs (Xilinx does this too), we see improved routing functionality. Having the large rectangular area for core fabric and other logic on the periphery help remove routing hot spots.

Unlike traditional CPUs, the flexibility of a FPGA also means that the reprogramming, placement, and routing are all concerns for those defining what a FPGA should do. As such, this is a big area of innovation.

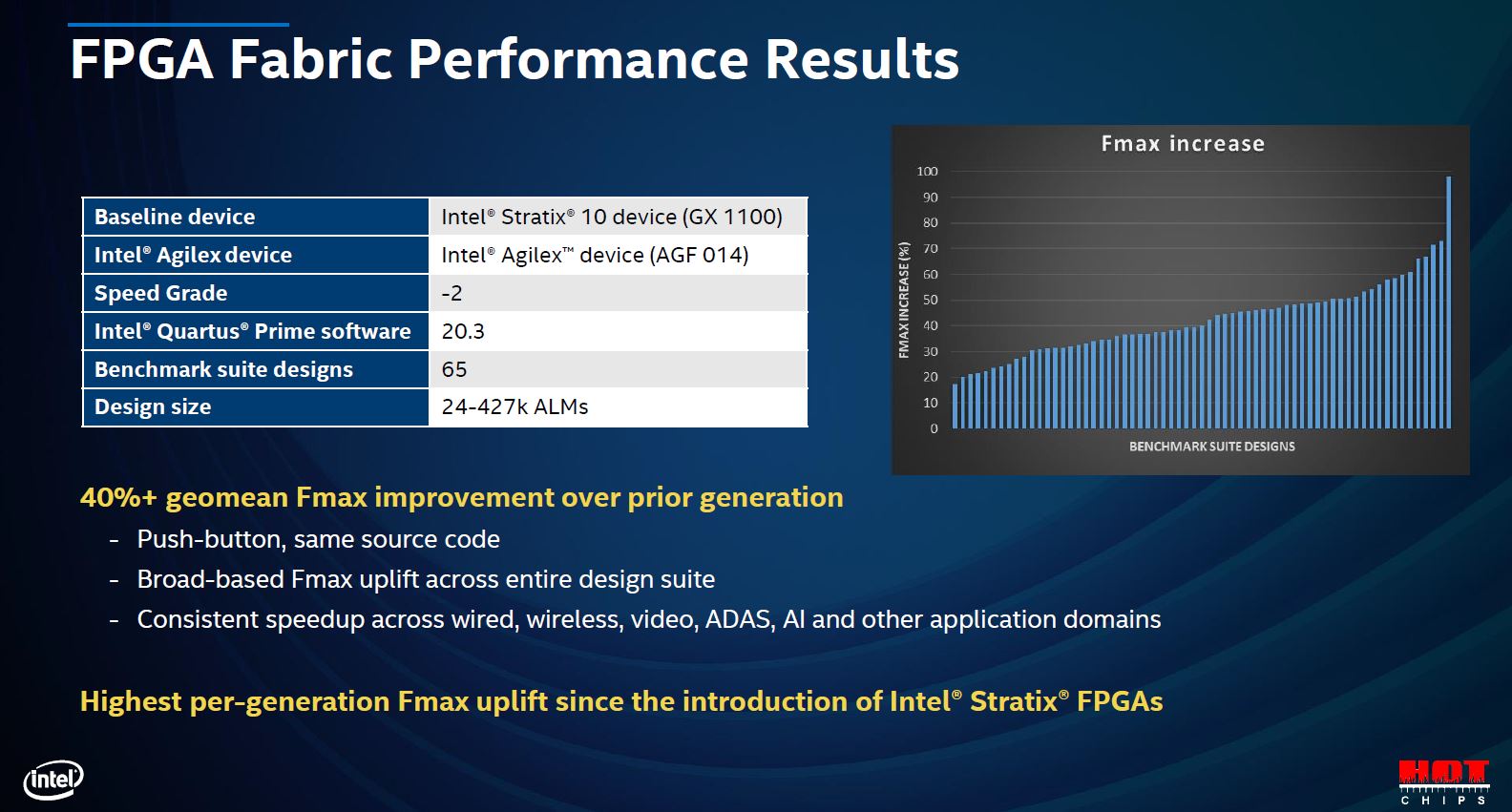

Intel is claiming large fabric performance results between Agilex and Stratix 10.

Let us move to the modularity, connectivity, and tiles.

Agilex Transceivers and Tile Modularity

Using EMIB packaging, one can add additional tiles to the Agilex FPGA. Intel has a number of their own tiles, but can also add 3rd party tiles.

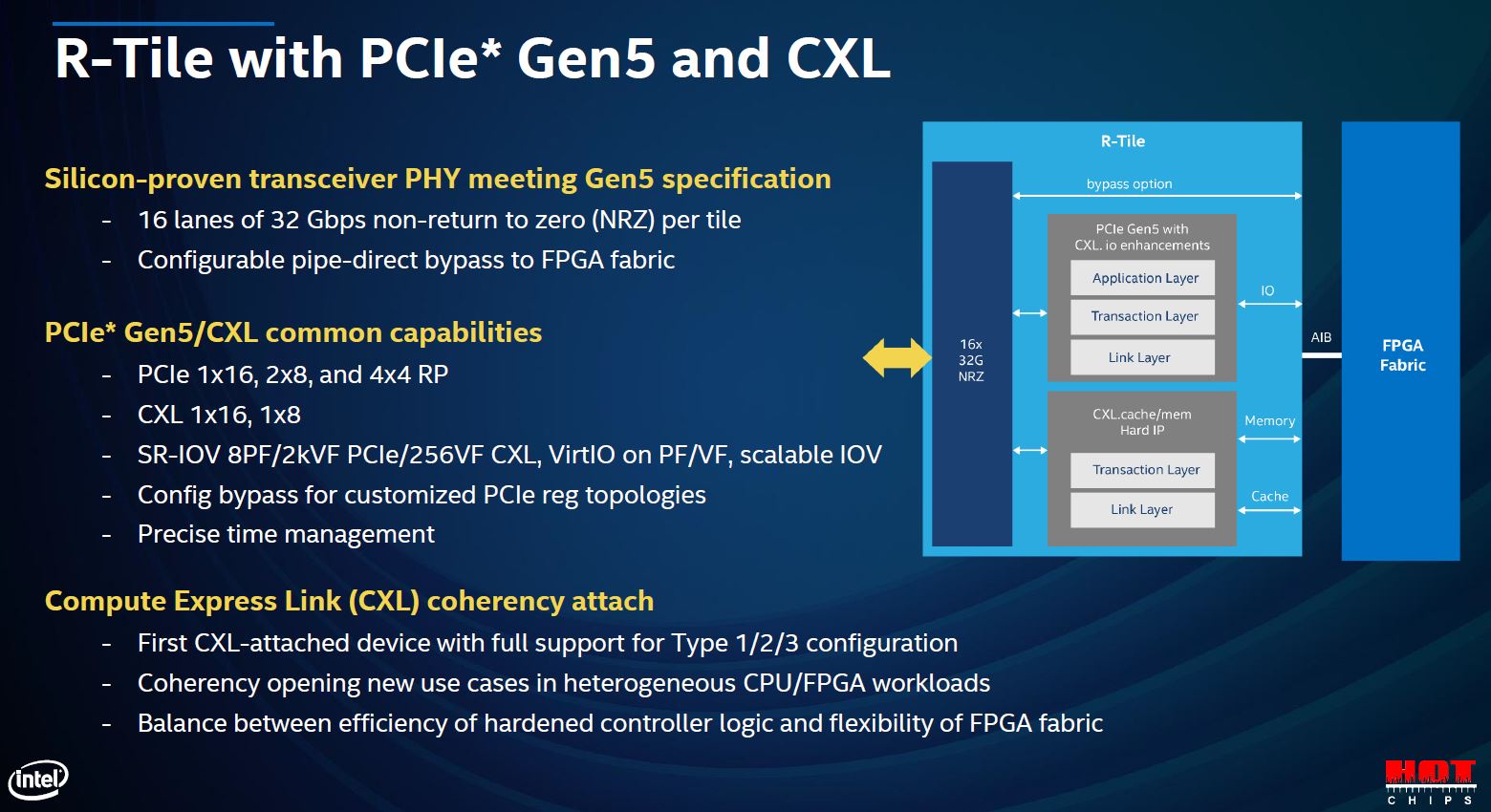

We thought this is one of the exciting tiles. Intel is now talking about PCIe Gen5 and CXL capabilities with Agilex which can be added via a R-Tile. This is Intel’s first CXL device. You can read more about CXL Details at Intel Interconnect Day 2019. This will allow Sapphire Rapids CPUs, as an example, to have a coherent interconnect to Agilex.

The F-tiles have high-speed transceivers. These tiles can be customized for different customers.

Intel has the ability to integrate both its own tiles, as well as tiles from 3rd parties. For example, if a customer had a custom DSP for 5G functionality, they could integrate those as well via EMIB.

Final Words

This solution has come a long way. We have already covered the Agilex Launch and Takeaways from a Discussion with Dan McNamara (who now, coincidentally runs the AMD EPYC business.) We also covered how it is shipping to Microsoft. Hopefully, we will see more Agilex in servers we review in the near future as we are starting to work with other vendors on this.