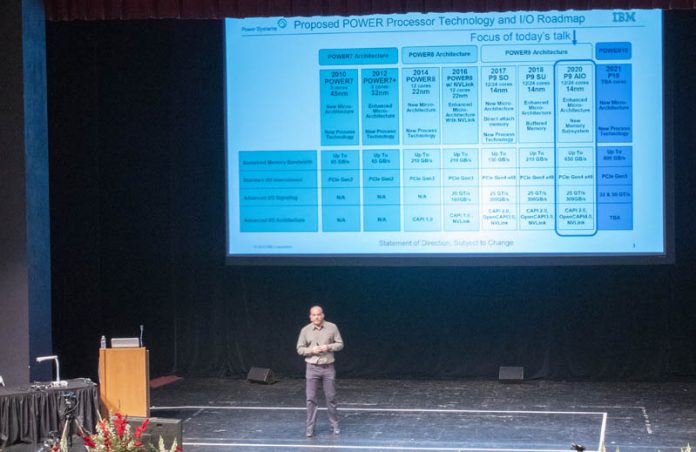

At Hot Chips 31, IBM showed off its newest Power9 chips. This is a big deal. The new IBM Power9 Advanced I/O (AIO) is designed to minimize the number of PHYs that the company needs, and provide what it calls the best acceleration platform. The company is not talking Power10 today, but it is talking about one of the key technologies, the Open Memory Interface. OMI is what is giving the new IBM Power9 platform a bump from 210GB/s to 600GB/s.

IBM Power9 Advanced I/O Overview

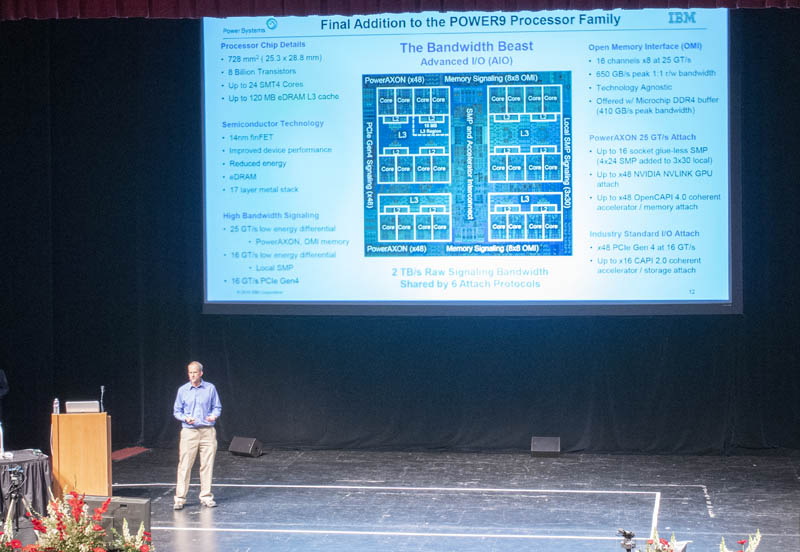

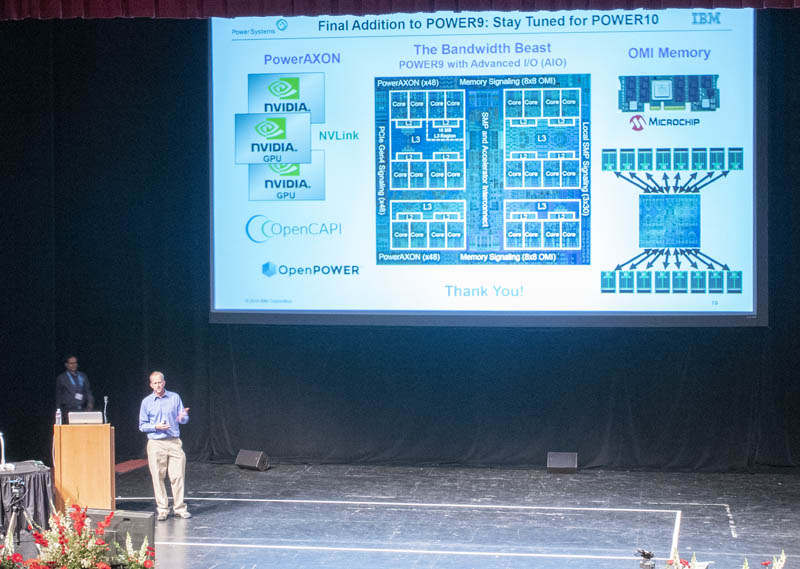

The IBM Power9 Advanced I/O family added three primary benefits. The first, IBM Power9 AIO adds the “next-generation NVIDIA NVLink.” You can read about NVLink and NVSwitch from our deep-dive look last year. Second, it introduces OpenCAPI 4.0 up from 3.0 in earlier versions of Power 9. Third, it adds support for the Open Memory Interface (OMI.) Here is the overview of the chip:

As one can see, by using OMI, IBM is able to dramatically increase the memory capacity and bandwidth over previous generation parts. IBM says that the design target is 5-10ns of additional latency while greatly increasing bandwidth. IBM also took a jab at AMD saying how with OMI, one does not need to re-spin an I/O Die to support DDR5. This is actually a telling comment. With the AMD EPYC 7002 series, AMD now has more PCIe bandwidth than IBM. Last year, IBM was taking jabs at Intel as the big x86 competitor.

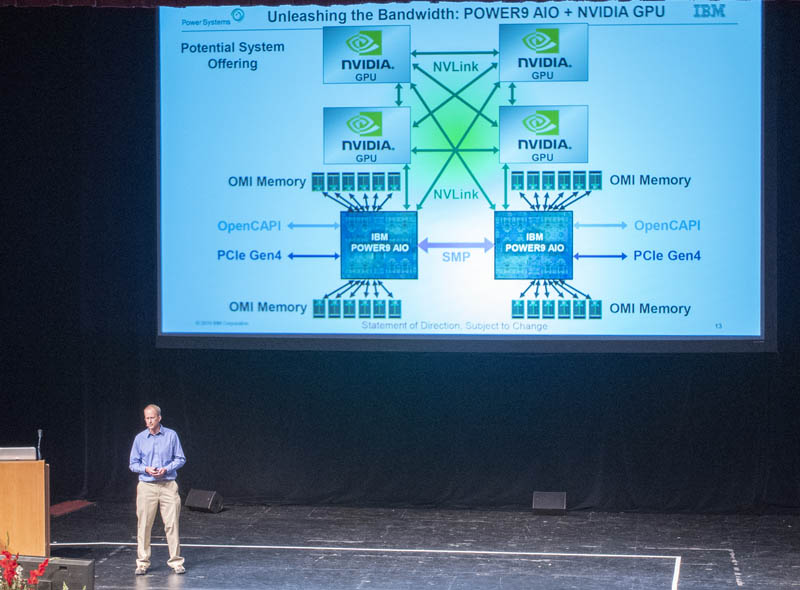

This is 2-socket, but it can scale up to 16 sockets. We had more on how these can scale to more accelerators in last year’s Hot Chips IBM coverage. Overall, the company is looking to simplify PHYs onboard which in turn allows it to increase bandwidth and I/O devices.

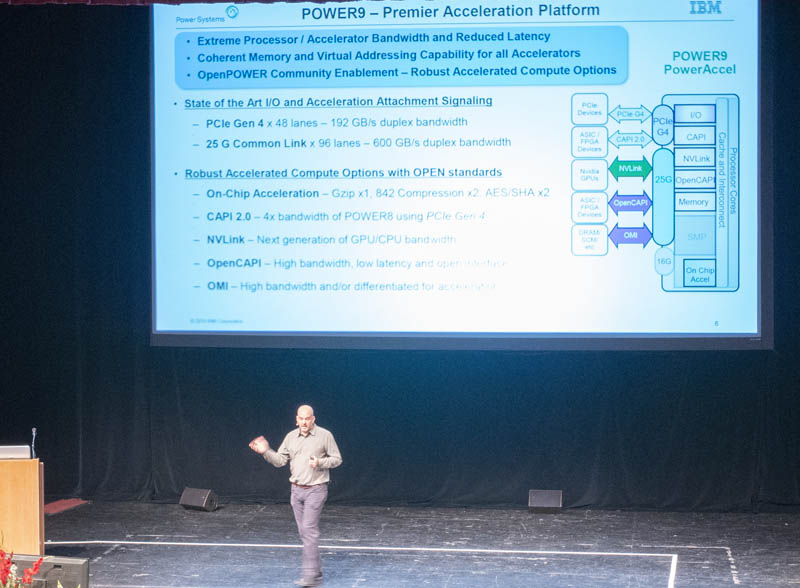

OpenCAPI and NVLink Design Goals

With OpenCAPI, the company wants to bring coherent caching accelerators. As computing gets more heterogeneous, many companies are targeting accelerators. IBM said it believes OpenCAPI is better than CXL because it can handle accelerators and memory, and is shipping today.

IBM did not out a new NVIDIA Tesla design, but it did say that there is a new NVLink coming for a new generation of GPUs, which we would expect.

IBM sees the Power9 AIO as a key technology to enable a diverse accelerator ecosystem today with more memory capacity and bandwidth.

Open Memory Interface

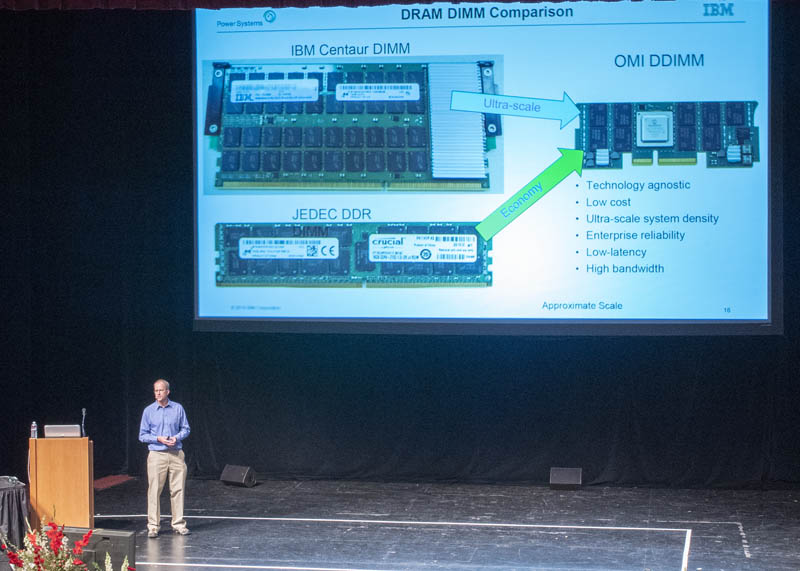

We covered this in our recent Microchip OMI piece. The basic idea is that serial attached memory is a lightweight, high-bandwidth interface. The OMI spec allows not just DDR4 DIMMs, but also future DDR5, persistent memory, tiered memory, and even GDDR6 memory onto the serial interface. It also allows one to use higher capacities of memory. Here is an example of the IBM Power memory evolution.

As one can see, IBM is getting its serial attached memory in a smaller form factor.

Looking Ahead to Power10

Looking ahead, IBM is introducing OMI in this generation so that the next-generation can support the feature.

We expect Power10 to have not just OMI, but also PCIe Gen5 and faster cores along with a few other new features.

So they took a jab at AMD for having to rearchitect for a newer memory standard while OMI DIMMs are practically proprietary and in use by them alone?

600GB/s per socket? I know a lot of HPC centers already queuing up at IBM doors to get these machines ;)