Nantero NRAM v. NVDIMM

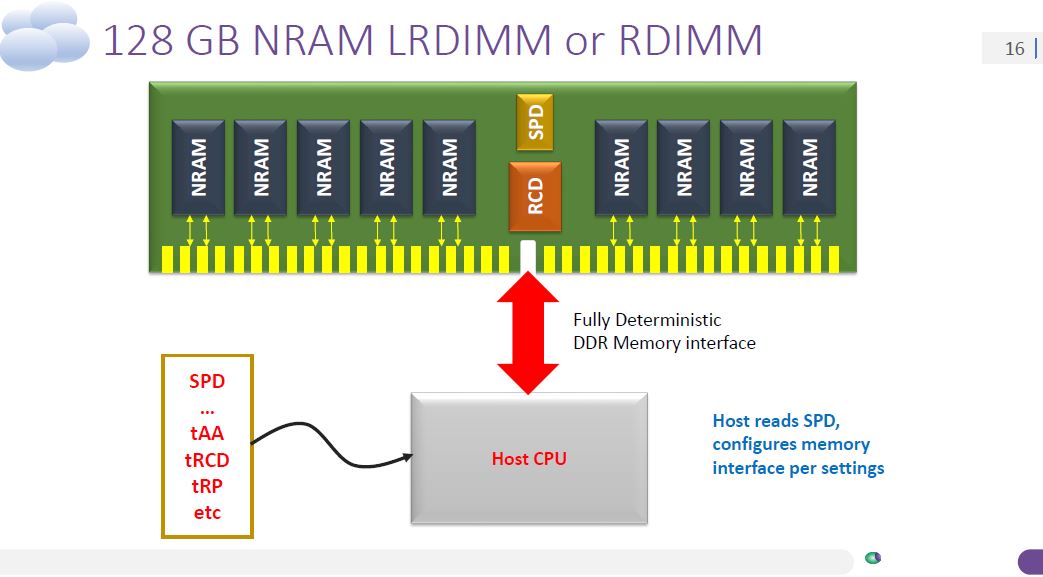

These days, NVDIMMs are becoming popular alternatives for persistent storage on the memory bus. NRAM DIMMs will look more like traditional LRDIMMs or RDIMMs as they will not require flash plus DRAM storage with a controller and a power source.

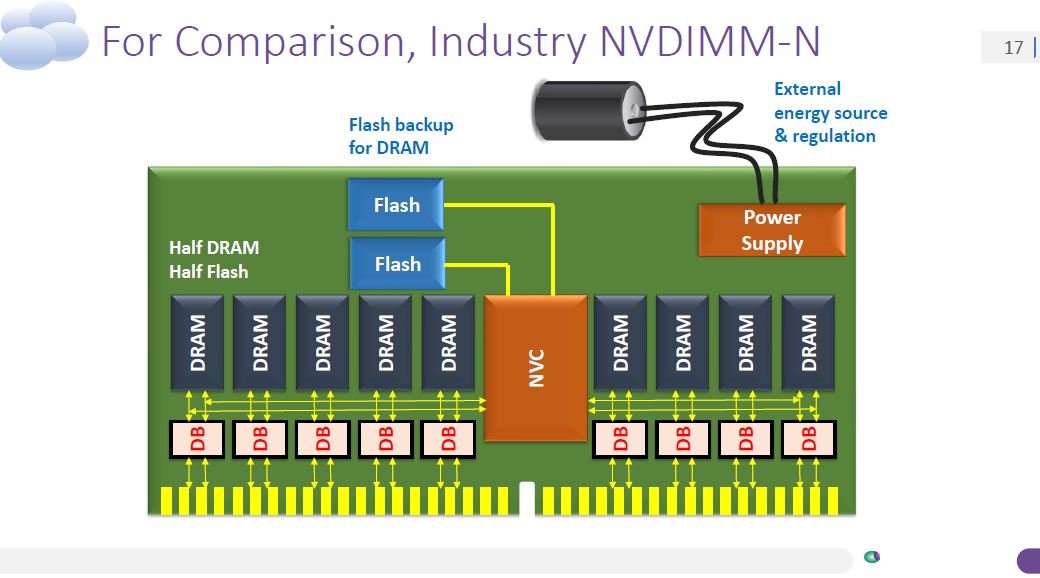

Here is an example of NVDIMM-N solution where DRAM is used. Upon power failure, the controller writes data to flash.

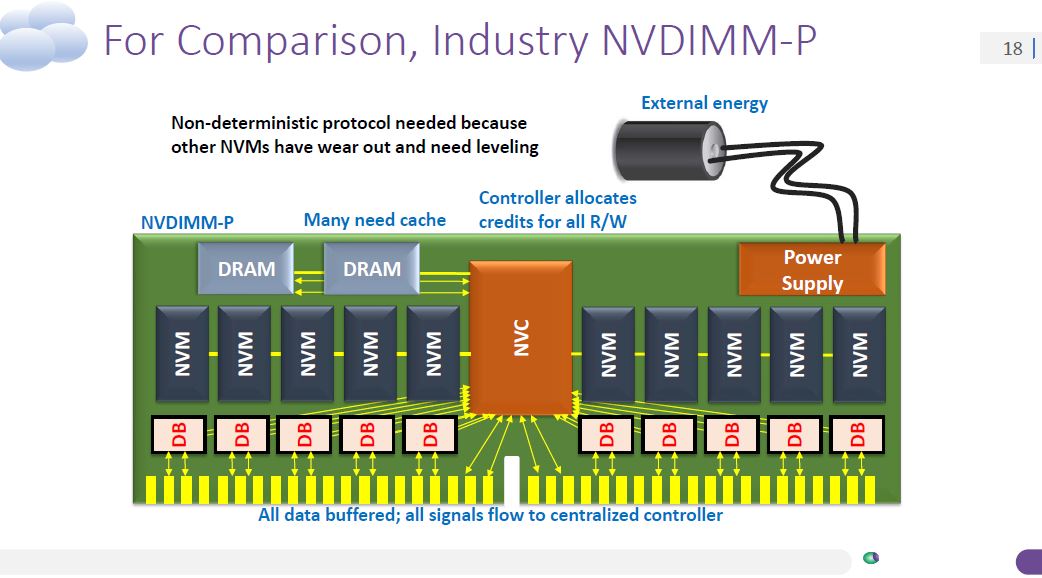

The NVDIMM-P model using nonvolatile memory but may have DRAM for a cache.

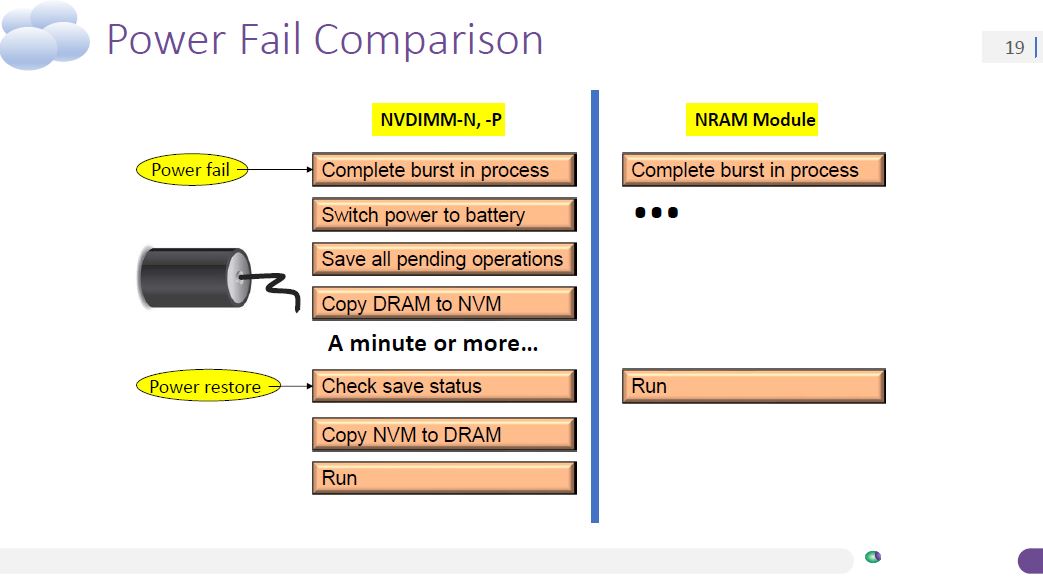

Since the NRAM is a persistent memory itself and running at DRAM speeds, it does not need any additional steps to function as a persistent memory.

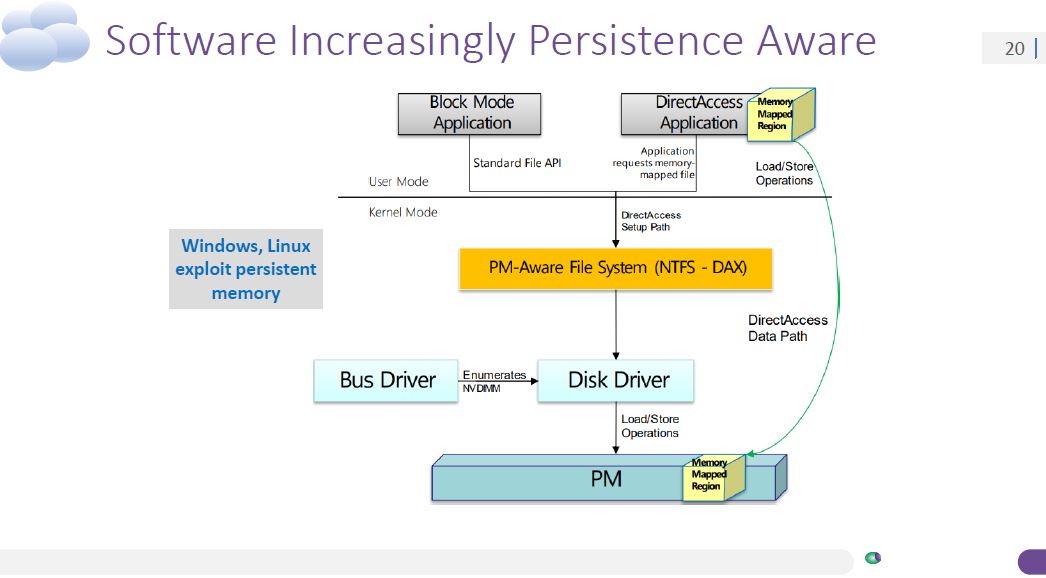

Nantero has a slide that basically says that the need for persistent memory is here as software is becoming persistence-aware.

At this point you may be thinking, this almost sounds too good to be true.

Final Words

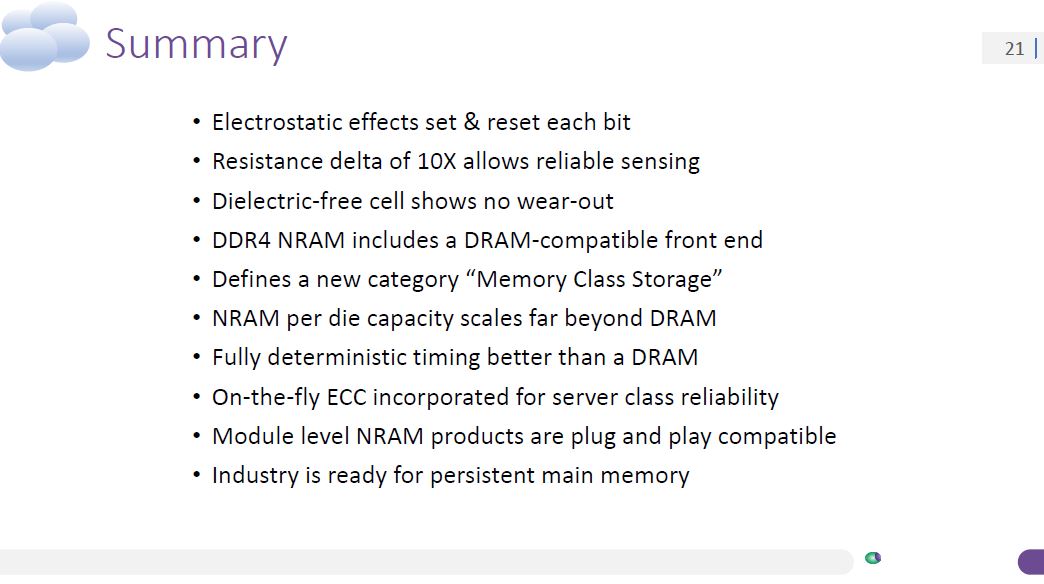

Here is the summary slide. Just about everyone in the audience thought it was borderline too good to be true.

A lot of the capacity scaling is dependent on process technology. Fujitsu’s NRAM as we covered some time ago, will pick up at 55nm while Nantero’s initial low capacity figures assume 28nm process. We believe that the initial batch of devices will be relatively small. We also think that the company did a great job drumming up industry interest at Hot Chips. One of those connections may lead to NRAM getting a shot at a smaller process node and higher capacity. We still think we are several years from seeing NRAM in servers. It is an interesting technology nonetheless.

While this might seem like everything is too good to be true, this was something that has been a long time coming. A few years ago UW Madison created carbon nanotube transistors that out performed silicon. https://news.wisc.edu/for-first-time-carbon-nanotube-transistors-outperform-silicon/ With a couple more years of R&D and process refinements it isn’t out of the question that nanotubes are getting to the point of being ready for RAM and eventually will probably replace silicon inside GPUs and CPUs.

A couple interesting questions pop to mind then:

– How well does a cell hold up under varying environmental conditions: Temperature, humidity, shock (Both physical and thermal shock), vibration?

– Do to the mechanical deformation involved, does the cell wear out?

– Due to a vibration or shock (physical or thermal again), can the gap necessary be created or destroyed creating a false bit flip?

Hi, guys, thanks for following up on this. We’re pretty excited for obvious reasons. To Don’s questions, we haven’t yet seen any tendencies for wear-out. The carbon nanotubes move in a void but once the contact is made between tubes via injection of electrostatic force, the bonding is atomic inside the van der Waals region. To separate the tube connections, a phononic disruption is needed to jump back over the vdW barrier. Macro effects like shock and vibe don’t impact the cells which are molecular level effects. Also, we use hundreds of switching tubes per cell so anything that would have that kind of impact would have other more catastrophic effects. One of the things carbon nanotubes are known for is lack of sensitivity to thermals, so temperature extremes don’t seem to have any effect on the cells; the limit would be the underlying CMOS.