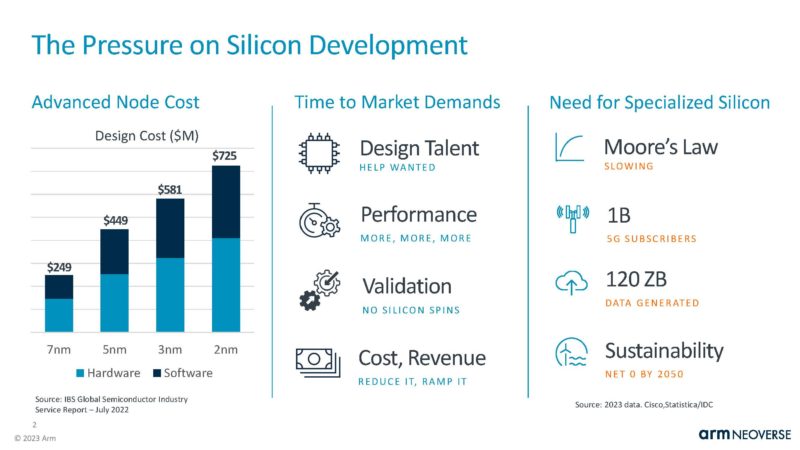

At Hot Chips 2023, Arm showed off a new way to implement Neoverse N2 cores. Instead of just licensing N2 core IP, Arm Neoverse Compute Subsystem or Neoverse CSS allows customers to buy larger IP blocks to drop into designs.

Since these are being done live from the auditorium, please excuse typos. Hot Chips is a crazy pace.

Arm Neoverse CSS Makes Neoverse N2 Cores Drop-in at Hot Chips 2023

Arm is targeting Neoverse CSS at making it easier for the chiplet community to integrate Noeverse N2 cores.

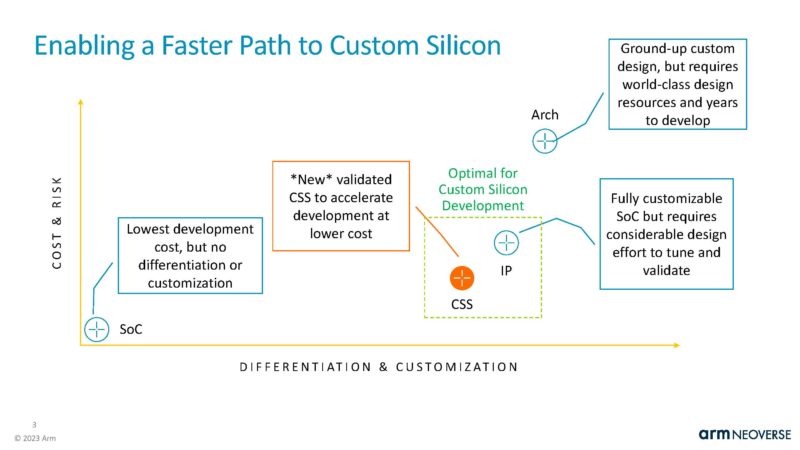

With new validated CSS solutions, less work is needed to implement Arm cores, hastening development, but Arm has other options.

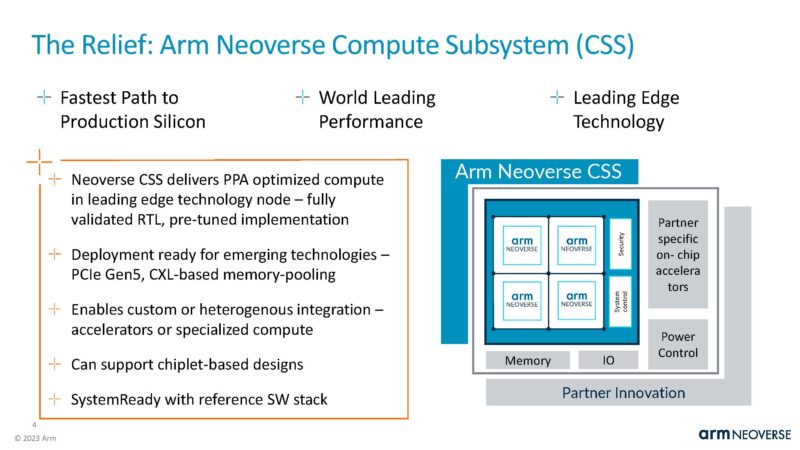

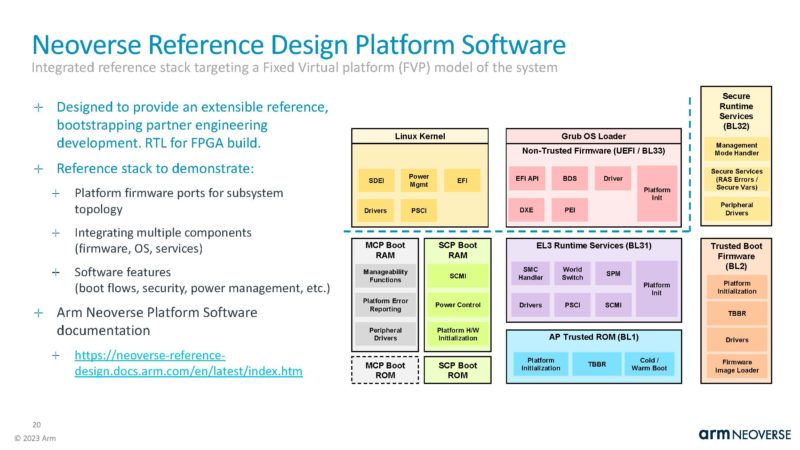

Neoverse CSS has fully validated RTL tuned and ready to implement into designs.

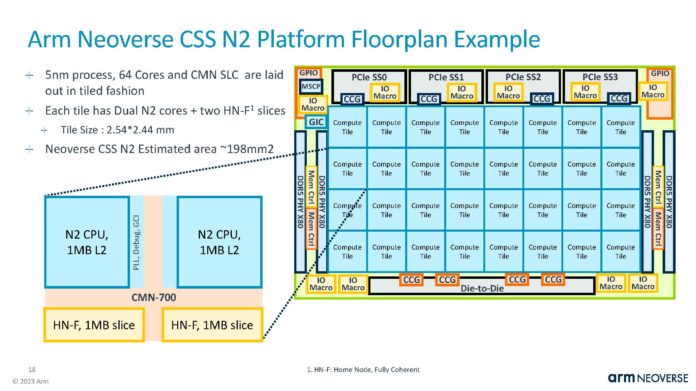

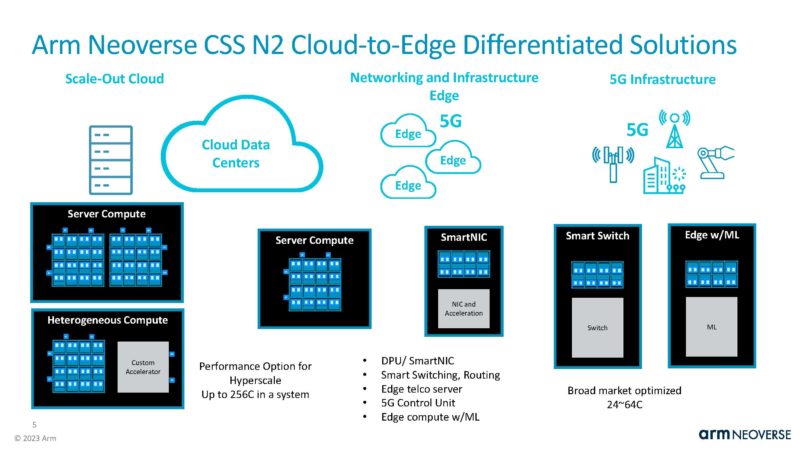

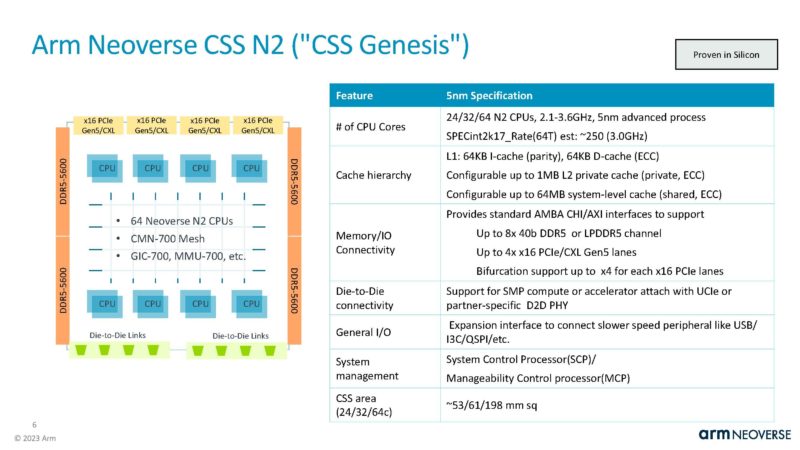

The first Neoverse CSS product is the Neoverse CSS N2. This uses Arm’s scale-out Neoverse N2 cores and allows companies to pick clusters of cores and implement them in designs.

N2 scales from 24, 32, and 64 core designs per chip. It has interfaces to connect to DDR5, LPDDR5, PCIe/ CXL, and other types of IP.

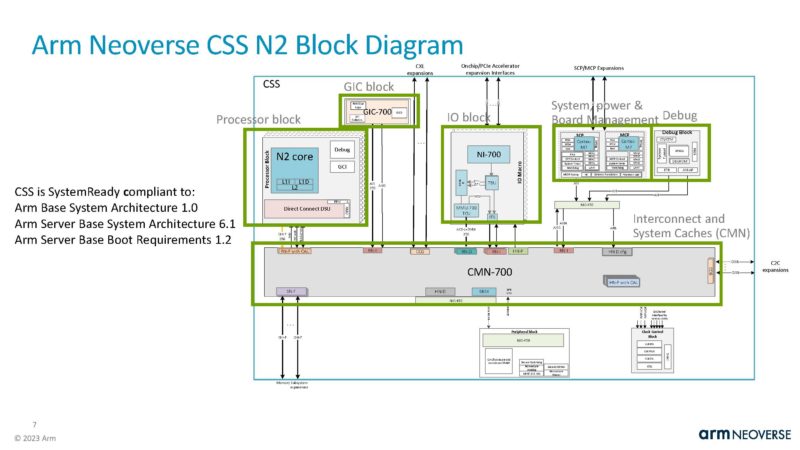

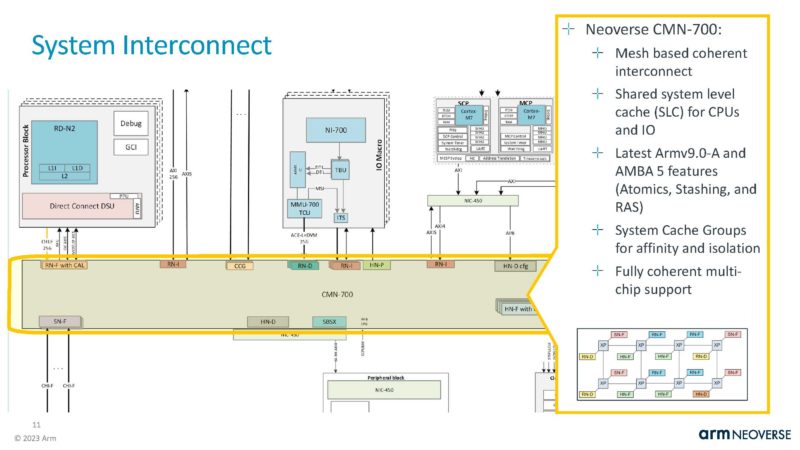

Here is the block diagram. Arm is using CMN-700 here to tie different components together. CSS is compliant to Arm standards out of the box which makes sense.

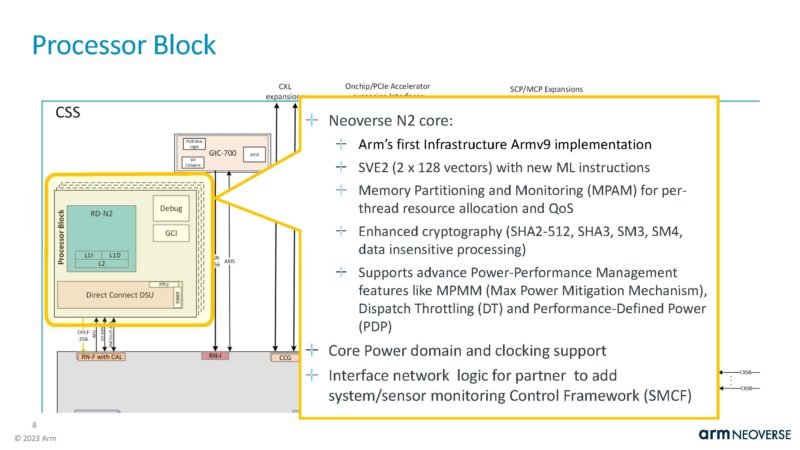

The processor IP block is based on the Neoverse N2 cores.

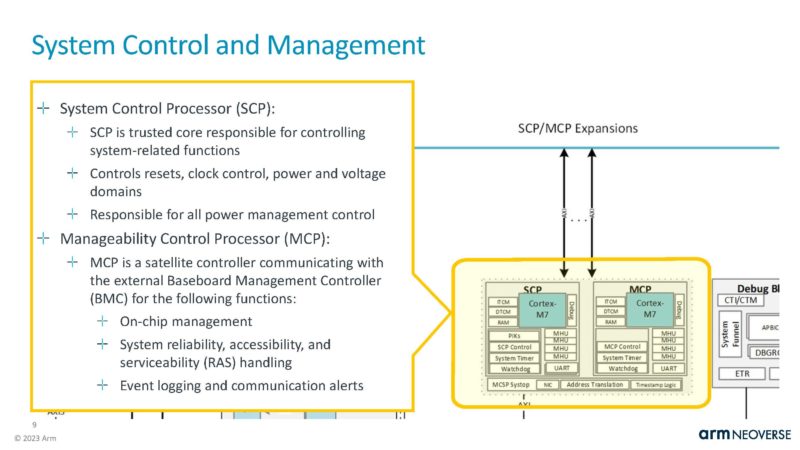

There is also an IP block for system control and management.

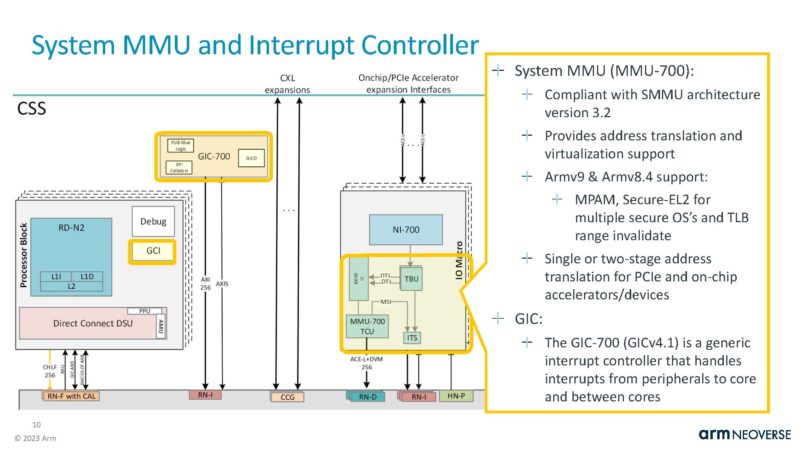

There is also a system MMU and interrupt controller.

Again, the Neoverse CMN-700 is included with the system level cache and the mesh-based coherent interconnect.

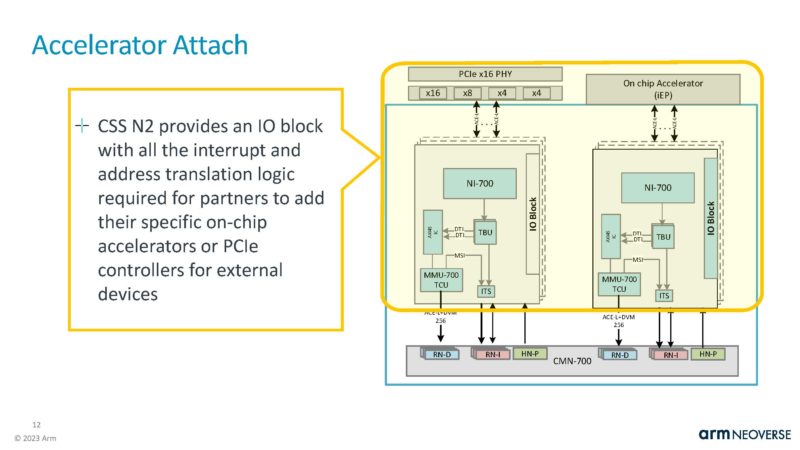

Arm is targeting this for vendors that want to attach accelerators, so it has IP for connecting those.

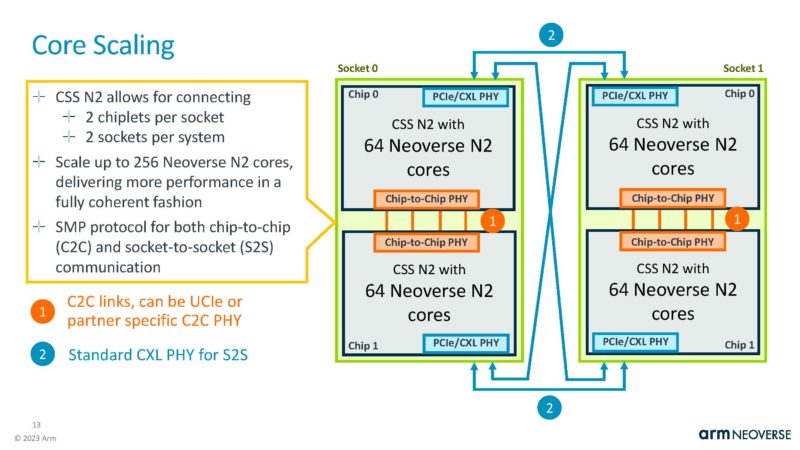

Arm can get to 128 cores per socket by connecting two 64-core Neoverse N2 chiplets together. What this tells us is that Arm is not aiming this to be a competitive high-density server CPU base in this generation. 128 Arm Neoverse N2 cores will not match AMD’s shipping Bergamo performance based on what we have seen thus far wich parts like the Marvell Octeon 10 and Neoverse N1 128 core parts like the Ampere Altra Max M128-30. This is really for those that need CPU cores for accelerators.

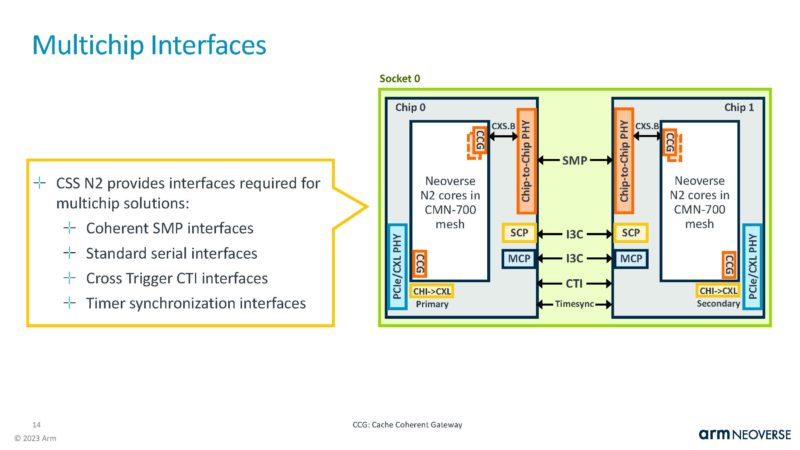

There are different interface options for chips and chiplets.

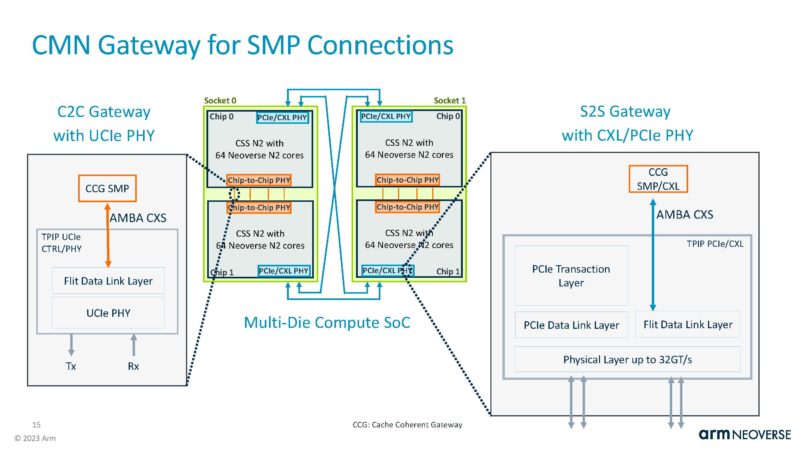

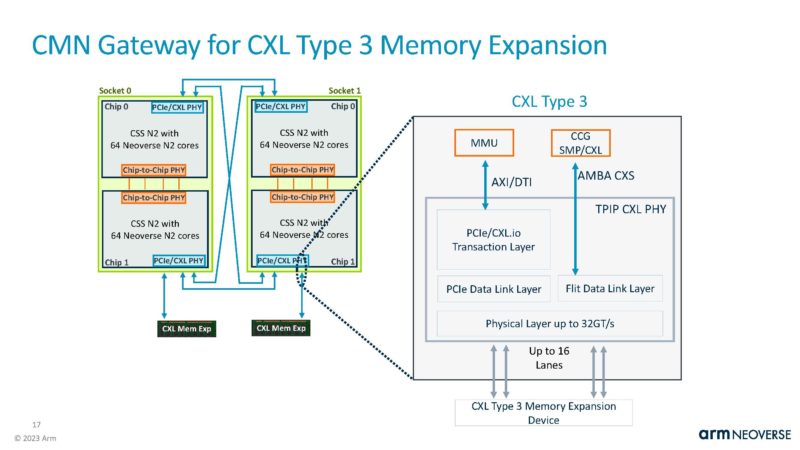

Here is the CMN gateway, but again, it does not seem like this is designed for high-end multi-socket CPU only systems.

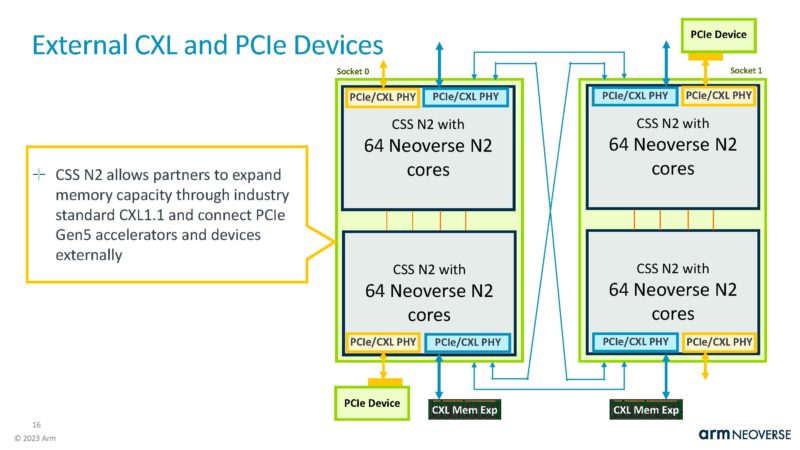

Here is the slide on CXL and PCIe IP added.

Arm says with the correct added IP it can support CXL Type-3 memory expansion devices.

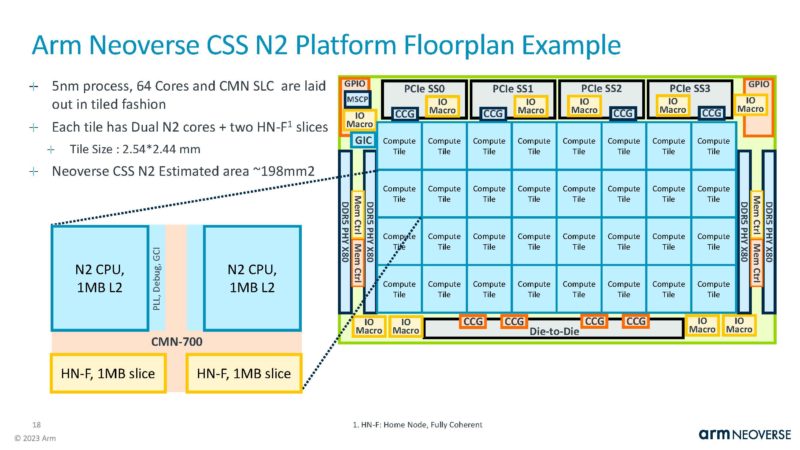

Here is the Arm Neoverse CSS N2 floorplan for a 32 core design as an example.

Here we can have two of these N2 blocks with a CMN-700 connecting everything.

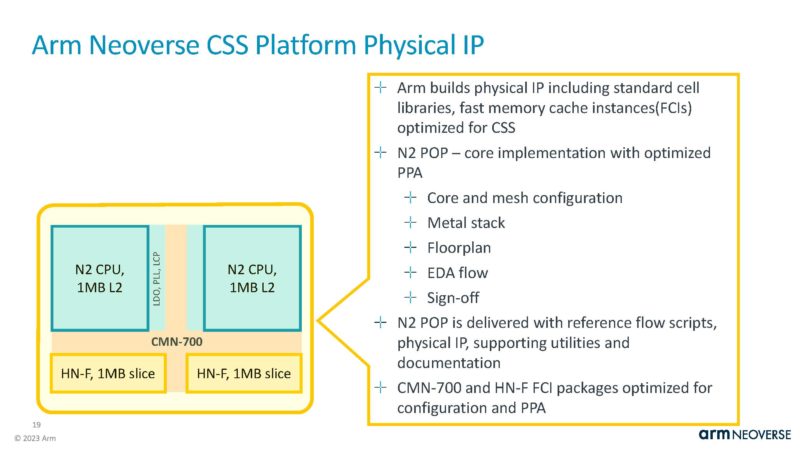

Along with the floorplan, Neoverse CSS has RTL and other software and design platform tools to help make development faster.

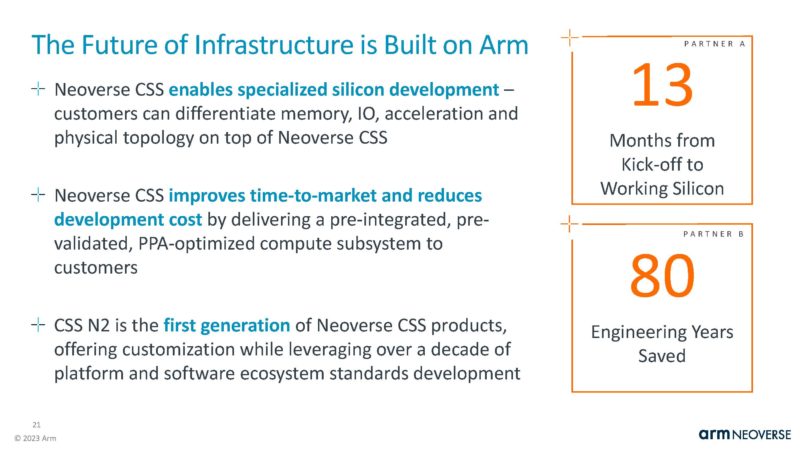

Arm says that it might be able to accelerate design by several quarters using this.

Overall, this is a very exciting announcement.

Final Words

Intel and AMD need to figure this out. Arm’s drop-in Neoverse CSS will likely expand to other core types over time. In the future, the next question is how relevant this is for chiplet CPUs. If Intel, for example, allows foundry customers to buy and integrate E-core chiplets then that is the next step in making it easier for companies looking to build packages. Still, Arm is out with CSS today, and in theory, it allows for a company to easily integrate N2 cores with an accelerator in a non-chiplet-based SoC.

This is a cool solution that we hope expands. On the other hand, one could also argue that Arm could sell pre-fabbed ready-to-integrate Neoverse chiplets with UCIe in the future for the ecosystem.