Ampere came out of relative stealth mode today and announced its 64-bit ARMv8 32 core CPU. The company is headed by Renee James, formerly of Intel and a new leadership team. One of the more interesting aspects to Ampere is also its owners. The company is backed by the Carlyle Group. The Carlyle Group purchased the AppliedMicro X-Gene 3 assets from MACOM in 2017 and now we know why.

The Ampere 32 core 64-bit ARM Server CPU

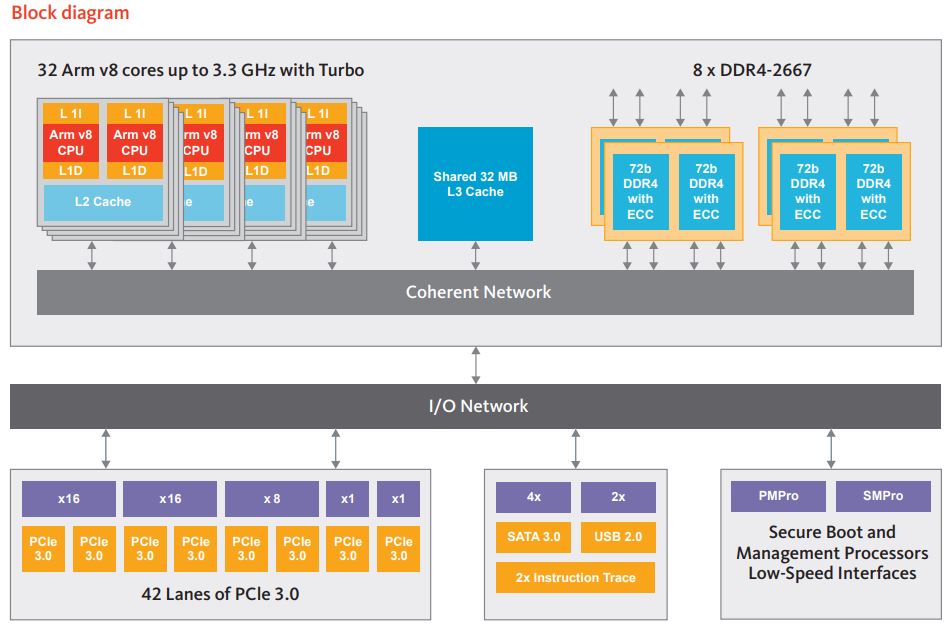

Here is the key feature list of the solution. You will notice this looks a lot like the X-Gene 3 solution we saw at OCP Summit 2017:

- 32 Arm v8 64-bit CPU cores up to 3.3 GHz with Turbo

- 32 KB L1 I-cache, 32 KB L1 D-cache per core

- Shared 256 KB L2 cache per 2 cores

- 32 MB globally shared L3 cache

- 8x 72-bit DDR4-2667 channels with up to 16 DIMMs, 1 TB/socket

- Full interrupt virtualization

- I/O virtualization

- Enterprise server-class RAS

– End-to-end data poisoning

– Error containment and isolation

– Background L3 and DRAM scrubbing - 42 lanes of PCIe Gen 3, with 8 controllers

– x16 or two x8/x4

– x16 or two x8/x4

– x8 or two x4

– Two x1 - 4 x SATA Gen 3 ports

- 2 x USB 2.0 ports

- TSMC 16 nm FinFET+

- 125W TDP

This is certainly a competitive part for the lower-end of the market. It is also yet another solution targeting 8-DIMMs per socket showing how Intel missed the mark with its six-channel DDR4 memory controller on the Intel Xeon Scalable line. Even this lower-end ARM CPU will address more memory than the current generation Xeon Scalable CPUs in a similar price / power segment.

For a quick reminder, the X-Gene 3 had 32 ARMv8-A 64-bit cores, 8x DDR4-2667 ECC memory channels supporting 2DPC (16 DIMMs) for a maximum of 1 TB RAM and 42x PCIe 3.0 lanes. Those types of specs, and ownership plays tell us that this is essentially a rebranded X-Gene 3 with the Ampere name.

Final Words

The X-Gene 3 had very little foot traffic at OCP Summit 2017 with similar specs, especially compared to the Cavium ThunderX2 (Broadcom Vulcan based) and Qualcomm Centriq 2400. For ARM entrants in the market, they essentially need to aggressively court either the embedded segments or large hyper-scale customers to maintain a viable product. The Cavium ThunderX2 (Vulcan based variant) is slightly different as its dual socket capability and first mover advantage have found its way into a number of applications.

We expect approximately a $1k price for these chips. Although X-Gene 3 was at OCP Summit 2017, Ampere expects mid-2018 shipments. That is going to put them in contention with shipping ARM server products and a next-generation of x86 solutions.

if the core is capable at least as X-Gene v1, then it’s very capable chip thanks to GHz increase. Anyway, I also hope they made their homework and do something on single-threaded performance. If so, then this would be great even for its $1k price…

Looking at the Block Diagram this doesn’t appear to be a NUMA architecture as in AMD EPYC, can you confirm?