At AMD Financial Analyst Day 2022, the company gave an update on its data center business and specifically the AMD EPYC roadmaps. We are getting ready for Genoa this year and Bergamo in the first half of 2023. We already covered the Zen roadmap in AMD Technology Roadmap from AMD Financial Analyst Day 2022.

This is being done very fast live, so please excuse typos.

AMD EPYC Update at AMD Financial Analyst Day 2022

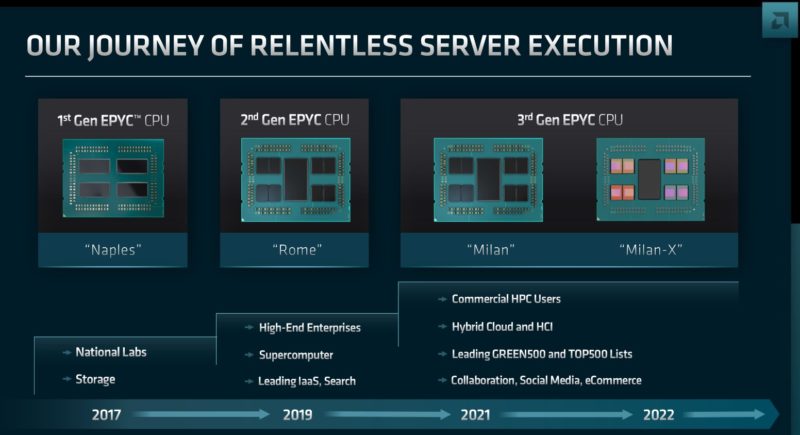

AMD’s data center and embedded business are growing rapidly. Here is the journey from Naples in 2017 to Milan-X in 2022.

Going after a bigger market TAM means AMD needs new chips.

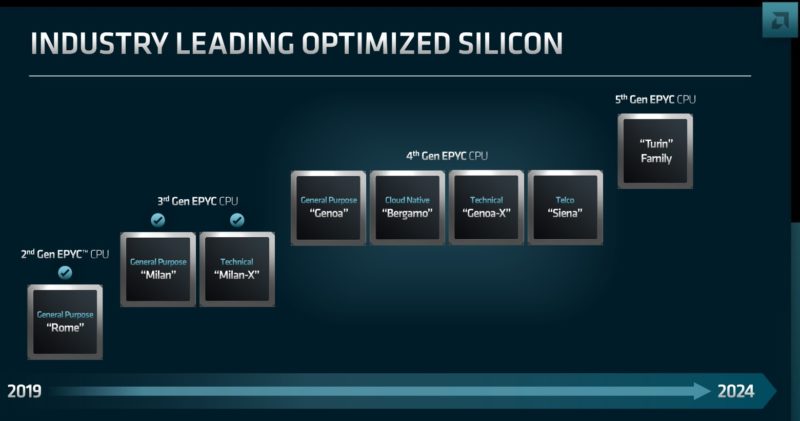

AMD says is building out its solution portfolio.

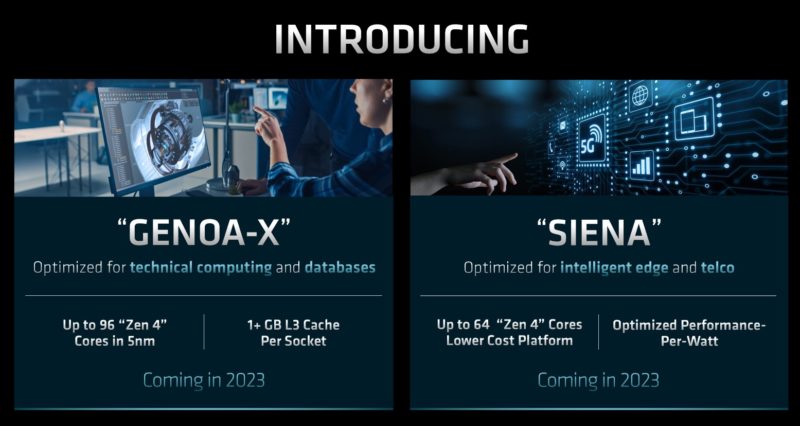

This is the AMD EPYC Zen 4 roadmap. We already know Genoa and Bergamo.

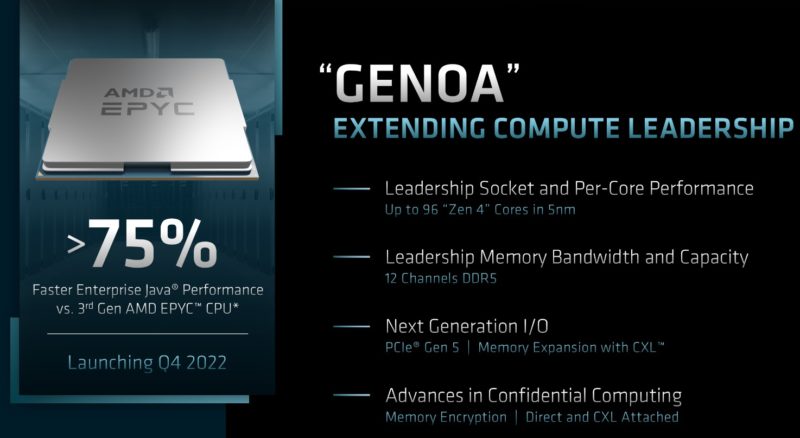

For Genoa, coming in Q4 2022, there are huge upgrades. PCIe Gen5 and CXL here. DDR5 and 12 channel memory for much higher memory bandwidth. AMD says it will enable CXL attached memory (Type 3) which is a cool capability. There will also be 96 cores on 5nm.

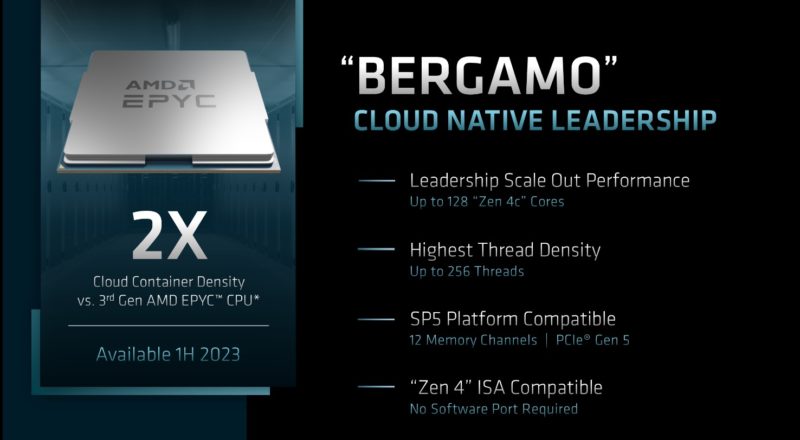

Bergamo is a higher density core chip in the same socket as Genoa. That means the same platform, but up to 128 cores and 256 threads per chip.

There will be a 3D V-Cache solution called Genoa-X with more than 1GB of L3 cache per socket. See Server CPUs Transitioning to the GB Onboard Era. Siena is a lower-cost Zen 4 platform.

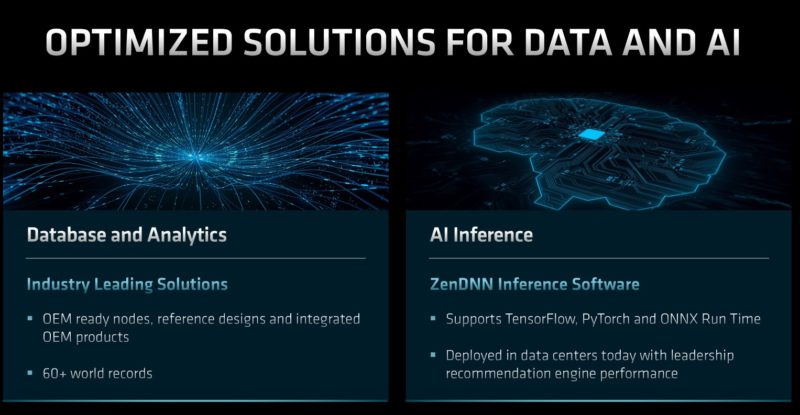

Intel is pretty far ahead in onboard accelerators for AI. We have even shown them in Stop Leaving Performance on the Table with AWS EC2 M6i Instances. Intel will have more accelerators in the next generation. AMD is also working on areas like an AI story.

We will hear more on AMD’s AI story in a bit.

Final Words

Great updates. Genoa and Bergamo sound exciting and this generally follows the trend of domain-specific features for server processors that we have been tracking on STH. Siena is important because AMD needs a lower cost and power solution as EPYC scales. Now, it is time to get on to the next presentation.

I really liked the smaller, single/dual Die Epycs, (3001 series iirc) but the market is really niche with Epyc for Enterprise and Ryzen for small business/homelab uses.

Socket for Siena would be interesting too, as the new, bigger one would bring quite a challenge for system designers

“PCIe Gen5 and CXL here. DDR5 and 12 channel memory for much higher memory bandwidth.” – I guess there is a mistake, isn’t Genoa supposed to sport DDR5? Seems so, from AMD’s slides; otherwise please remove the “huge upgrades” wording in the preceding statement, as we are sick off DDR4 already :)