AMD EPYC 7003 Updating the EPYC 7002

Next, we wanted to talk about what is being updated, specifically the architecture. This is a much less dramatic shift than we saw from the EPYC 7001 to EPYC 7002, but it still can have a big impact on performance.

AMD EPYC 7003 Zen 3 Update

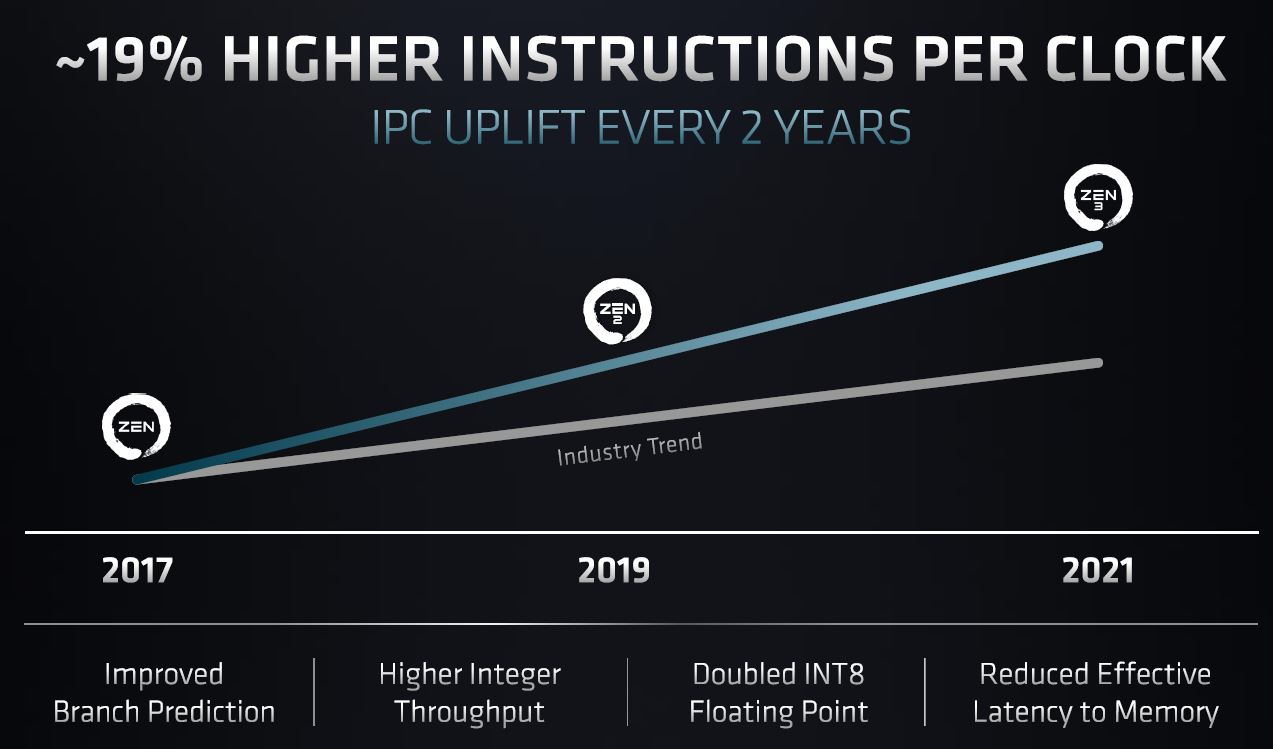

AMD calls its microarchitecture Zen followed by a generation. This is Zen 3 and AMD says it is worth around a 19% higher IPC.

Many of these slides are going to look familiar. AMD Zen 3 and AMD Ryzen 5000 series have been out for some time and AMD leverages the microarchitecture across product lines.

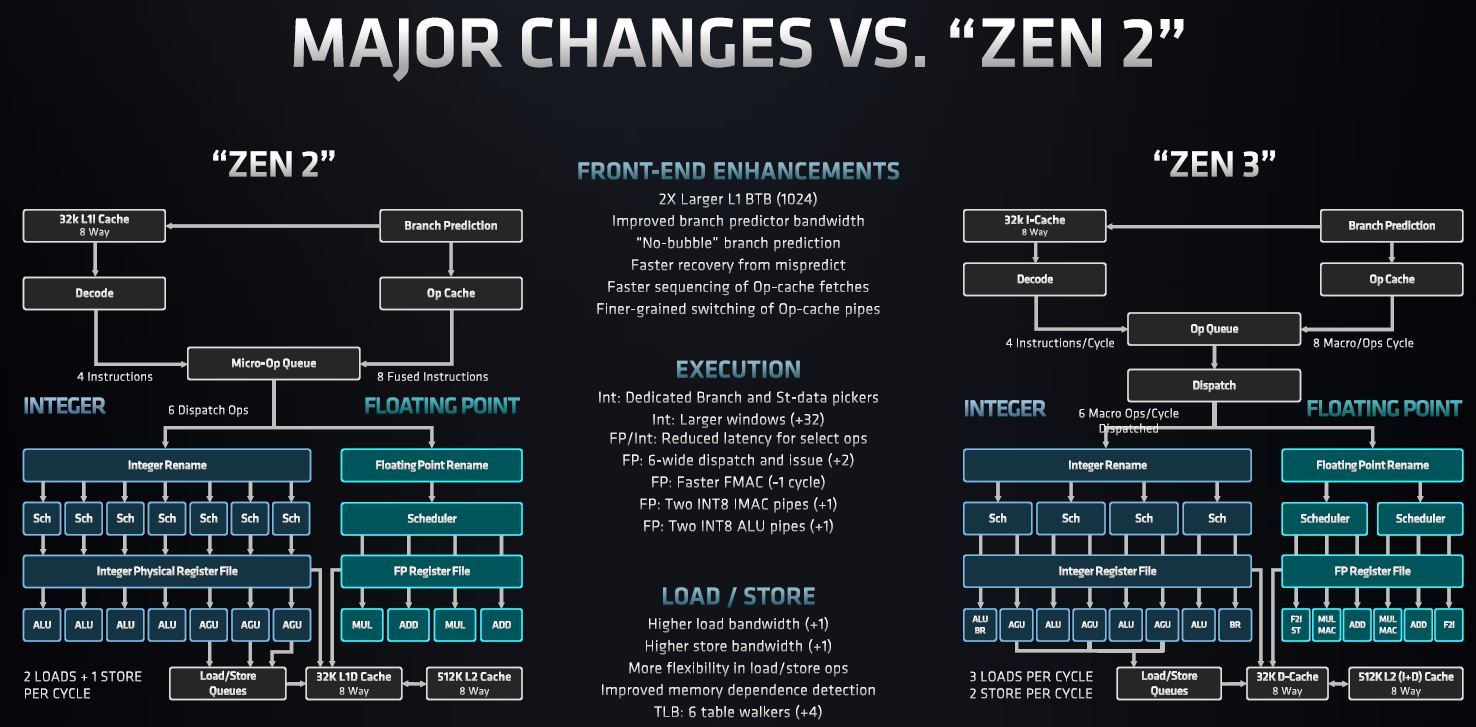

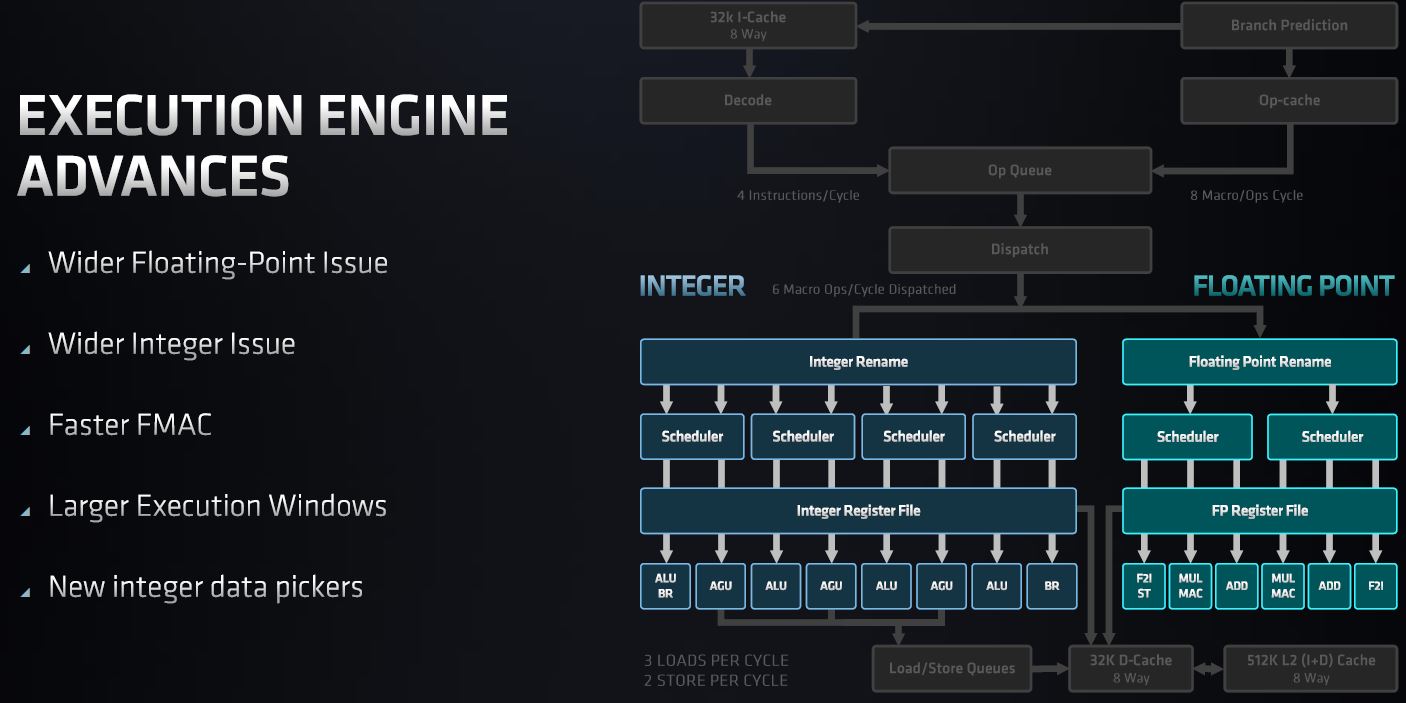

Here is a summary of major changes compared to Zen 2. For our purposes in the server space, Zen 2 is the AMD EPYC 7002 series codenamed “Rome” and Zen 3 is EPYC 7003 “Milan”. Sometimes when using these terms all day we make the incorrect assumption that everyone knows this translation.

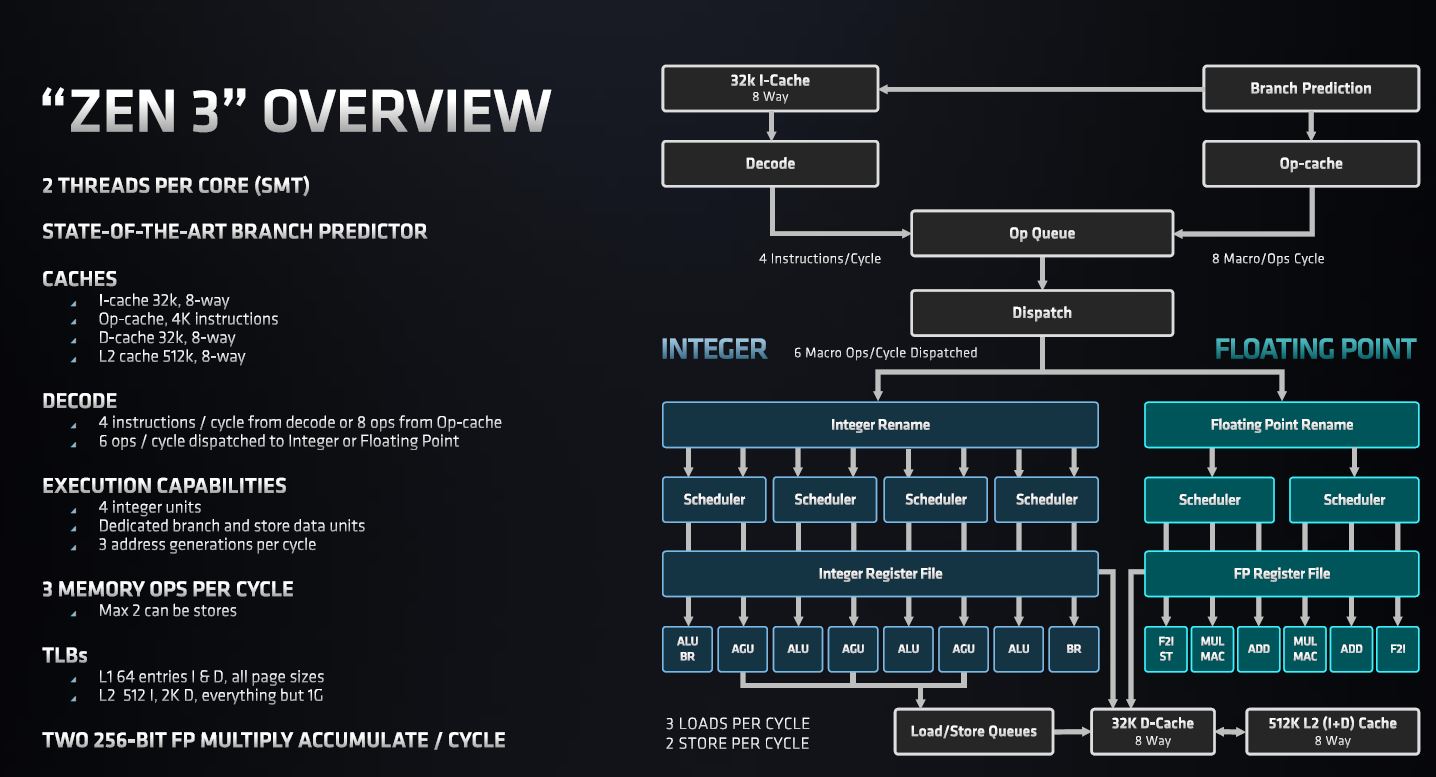

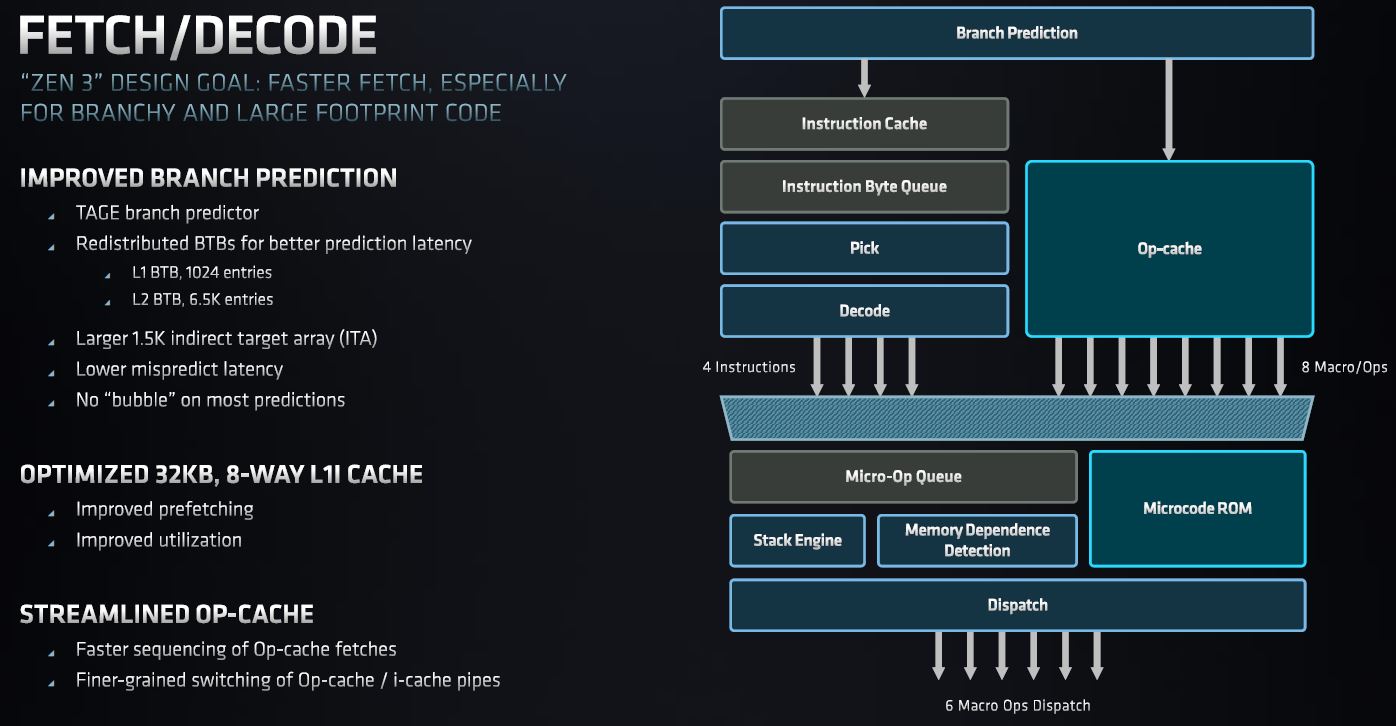

AMD has new front end that helps fill its caches. A big part of AMD’s architecture is leveraging massive on-chip caches to ensure that its execution units are not stalled waiting for data.

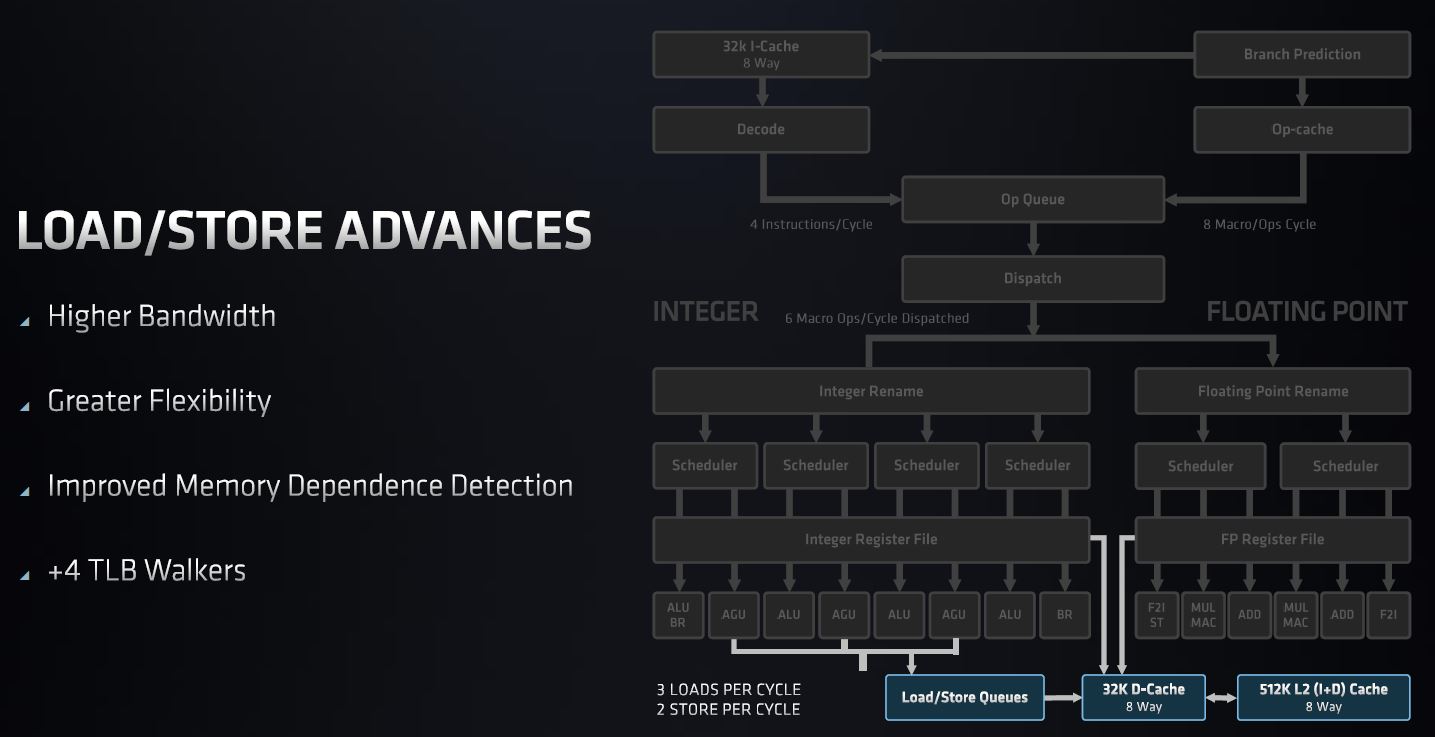

As we are seeing as a broader industry trend, we are getting wider execution engines.

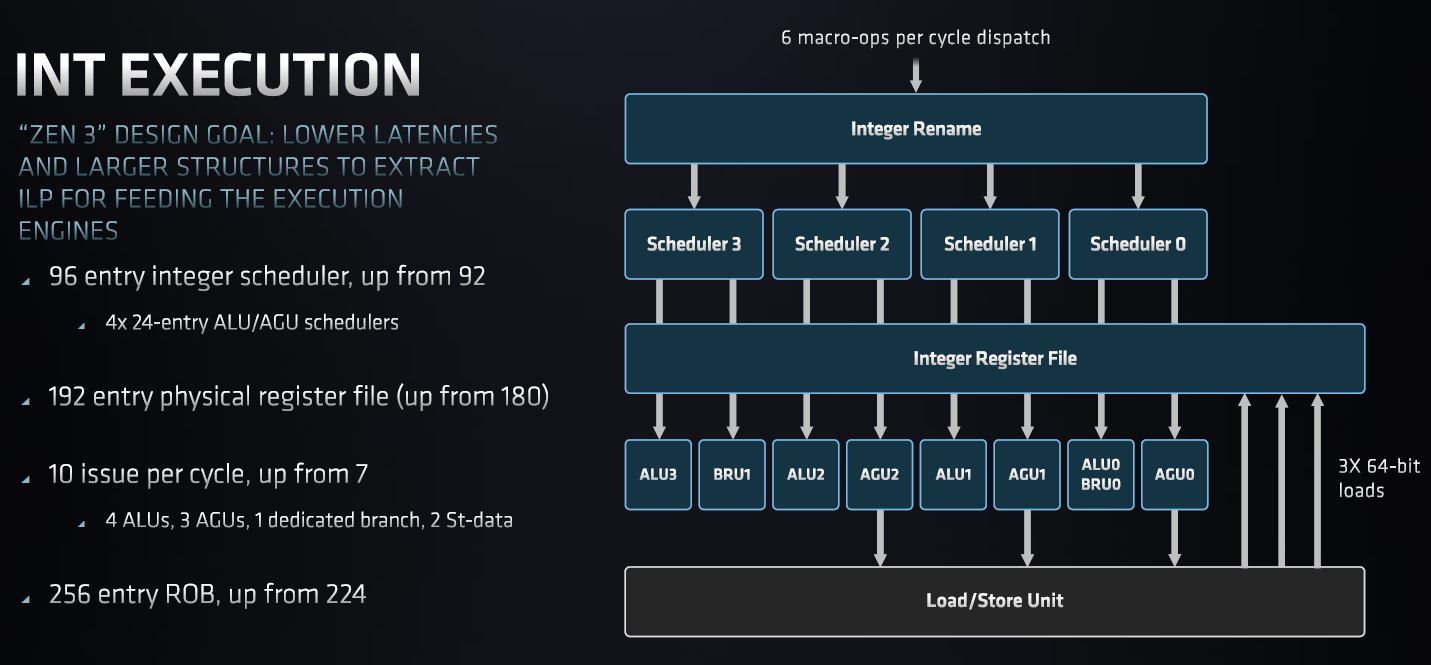

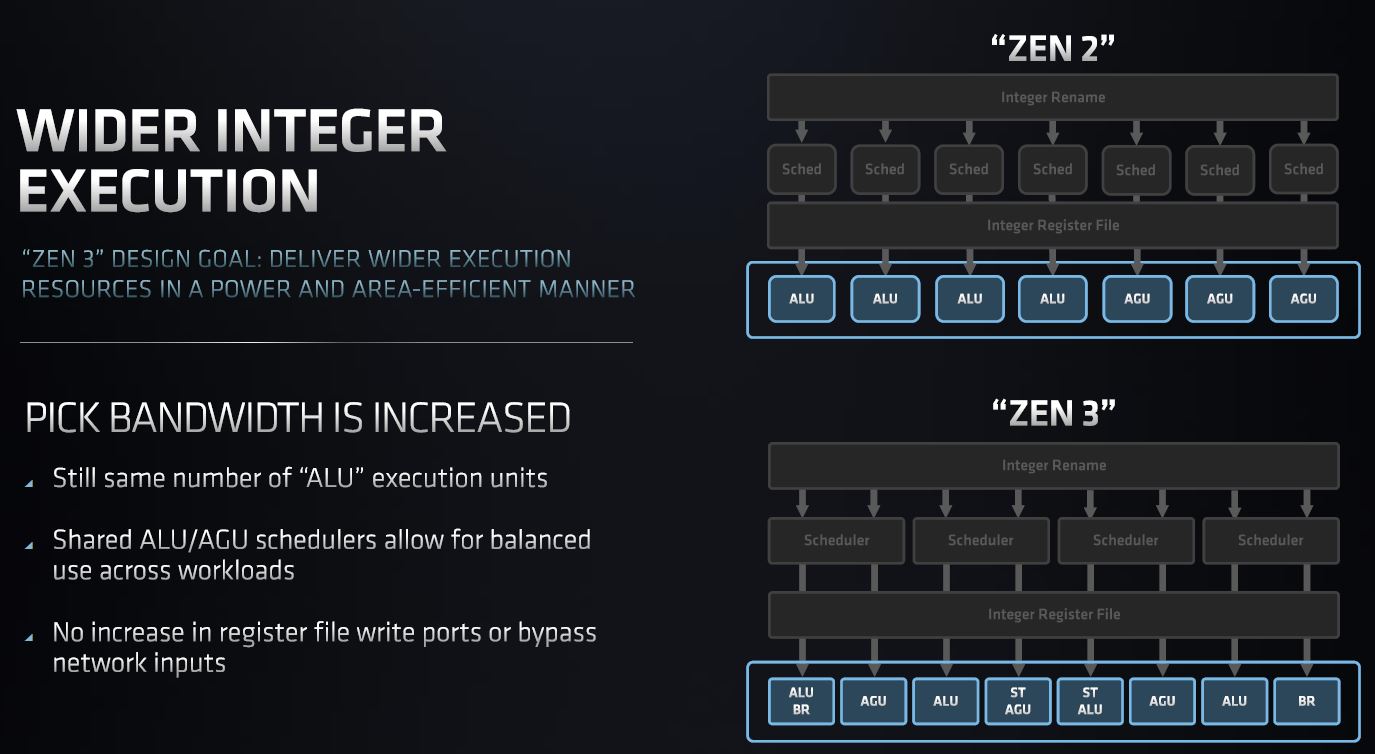

This extends to integer execution.

Typically integer operations are important in data center/ enterprise workloads making these improvements especially helpful.

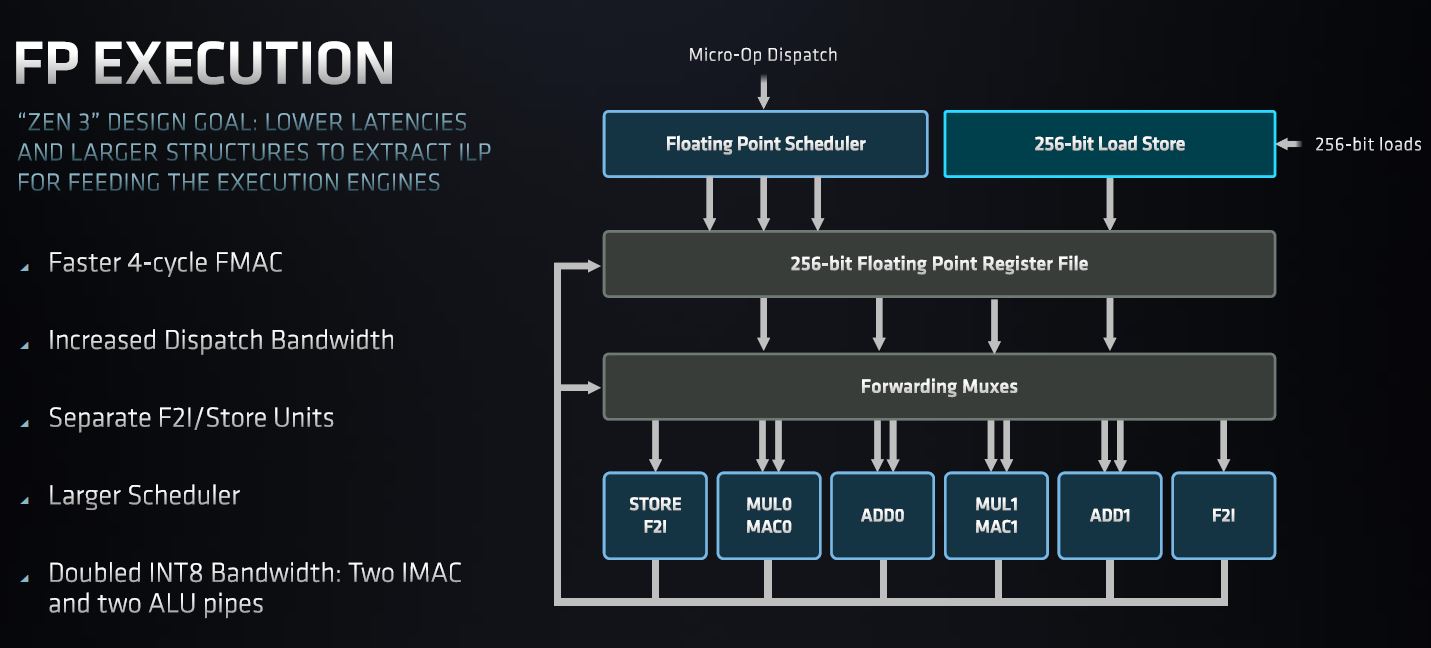

On the floating point side, we get another set of improvements. We are going to let you browse the slides if interested.

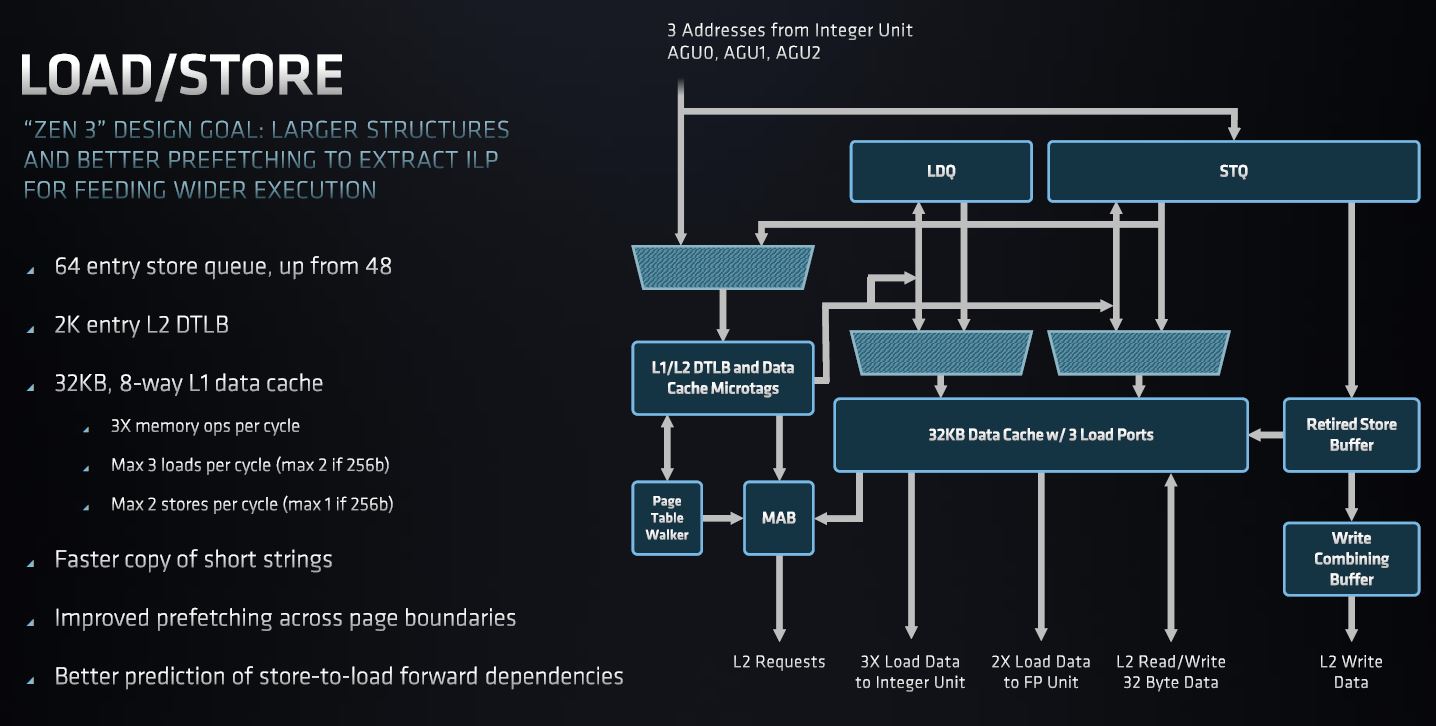

On the load/ store side, AMD again is making advancements. The key here is that AMD is tweaking its architecture with each generation. We are not getting 3-7% improvements. The large numbers of improvements mean we are getting much more than recent historical norms.

The load/ store engine is designed to keep data flowing through the execution units. This is a common processor theme. We even see AI chips focusing on this. Now that we are in an era of increasing core or execution unit counts, there is more pressure on the structures to deliver the correct data to keep those execution units doing useful work.

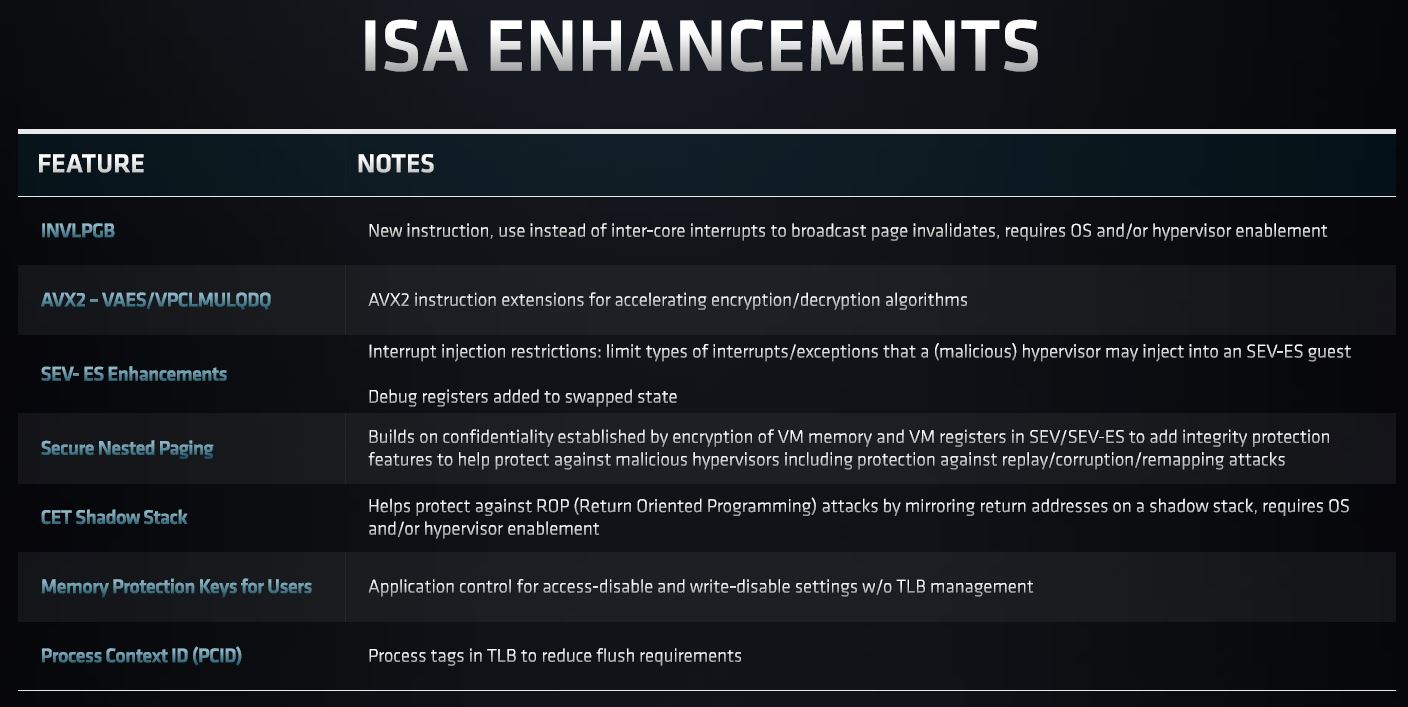

AMD also has some ISA enhancements. We are not going into these too deeply, feel free to read these if interested.

This is focused on the Zen 3 core, but an EPYC 7003 processor is much more than a core. Next, we are going to look at how AMD takes its Zen 3 core IP and creates the Milan processor.

Any reason why the 72F3 has such conservative clock speeds?

The 7443P looks as if it will become STH subscriber favorite. Testing those is hopefully prime objective :)? Speed, per core pricing, core count – there this CPU shines.

What are you trying to say with: “This is still a niche segment as consolidating 2x 2P to 1x 2P is often less attractive than 2x 2P to 1x 2P” ?

Have you heard co.s are actually thinking of EPYC for virtualization not just HPC? I’m seeing these more as HPC chips

I’d like to send appreciation for your lack of brevity. This is a great mix of architecture, performance but also market impact.

The 28 and 56 core CPUs are because of the 8-core CCXs allowing better harvesting of dies with only one dead core. Previously, you couldn’t have a 7-core die because then you would have an asymmetric CPU with one 4-core CCX and one 3-core CCX. You would have to disable 2 cores to keep the CCXs symmetric. Now with the 8-core CCXs you can disable one core per die and use the 7-core dies to make 28-core and 56-core CPUs.

CCD count per CPU may be: 2/4/8

Core count per CCD may be: 1/2/3/4/5/6/7/8

So in theory these core counts per CPU are possible: 2/4/6/8/10/12/14/16/20/24/28/32/40/48/56/64

I’m wondering if we’re going to see new Epyc Embedded solutions as well, these seem to be getting long in the tooth much like the Xeon-D.

Is there any difference between 7V13 and 7763?