At STH, we have been talking about the Intel Clearwater Forest part for what feels like a long time. The wait is not over yet since Clearwater Forest is scheduled for 2025. The chip will use new packaging technology as well as the new Intel 18A process. Last week, STH got to see the chip up close.

This is Intel Clearwater Forest the Next-Gen E-Core Xeon

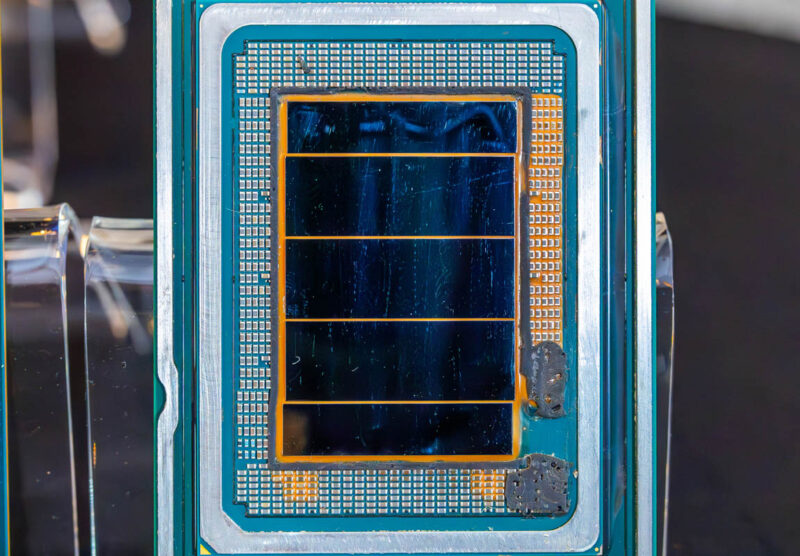

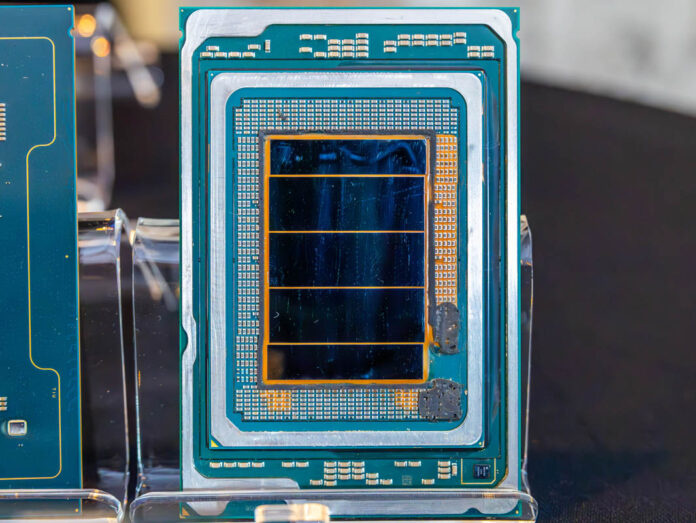

At the event for the Intel Xeon 6900P series last week in Oregon, Intel brought out some of the Clearwater Forest CPUs. What is even more exciting is that we grabbed photos of not just the new Intel Xeon 6 parts but also of the high-core count next-generation E-core Xeon. Here is a close-up of Clearwater Forest.

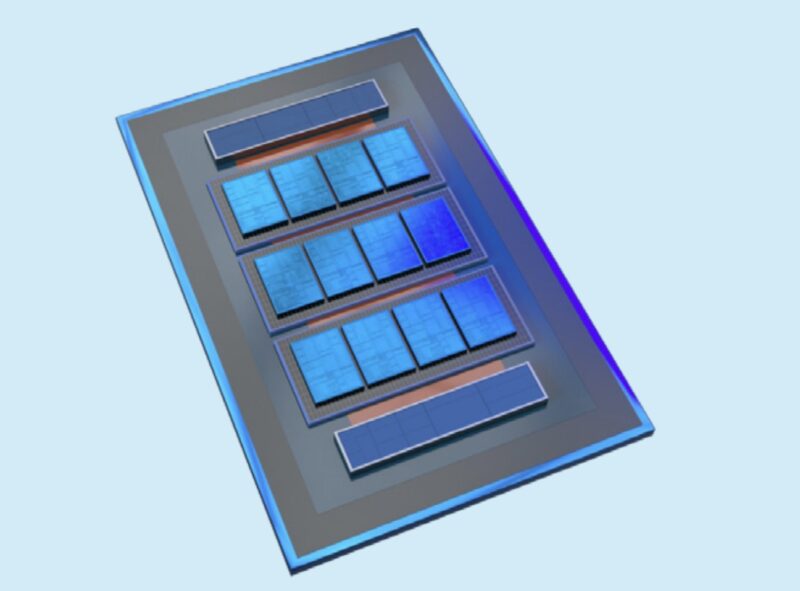

If things look a bit different on the three middle rows of compute tiles, perhaps they should. Earlier this year, Intel showed us that each of these rows look more like four small compute tiles arranged in rows.

That differs from the Intel Xeon 6900P, which has an I/O die on top and bottom, and three rows in three compute tiles.

One will also quickly notice that the CPU package itself is constructed very differently than the Sierra Forest-AP and Granite Rapids-AP parts sitting next to it here.

Something to think about is that on the Sierra Forest and Granite Rapids parts, the PCIe I/O and UPI links are in the I/O dies at the top and bottom so that they have a clear path to the north and south ends of the chip for signal routing. Likewise, memory controllers on those two parts are on both sides of the compute tiles, aligning to memory slots on the east and west sides of the package. The memory controller layout must change with Clearwater Forest and smaller compute tiles. Intel has not yet disclosed how it will change.

Final Words

Intel said Clearwater Forest is already booting. However, it feels like the chips are a long way away, given that we have not even had the Sierra Forest-AP launch scheduled for early 2025.

While we have already shown you that the 144-core Sierra Forest is becoming very competitive with Arm offerings, Clearwater Forest is the generation that will likely jumpstart the E-core CPU revolution on the x86 side. Updated cores plus updated process and packaging technology will hopefully yield a step function jump in all E-core CPUs. When discussing Sierra Forest, many in the industry say it is excellent, but Clearwater is exciting. Hopefully, we will get hands-on with those new chips, not just on display but in a system soon.

For our Substack subscribers, we put the high-resolution JPEGs of this and the rest of the Xeon 6 family that we took in Oregon. We can put much higher-resolution photos there since having 100,000+ folks download another 120MB of images is not really feasible for a main site article.

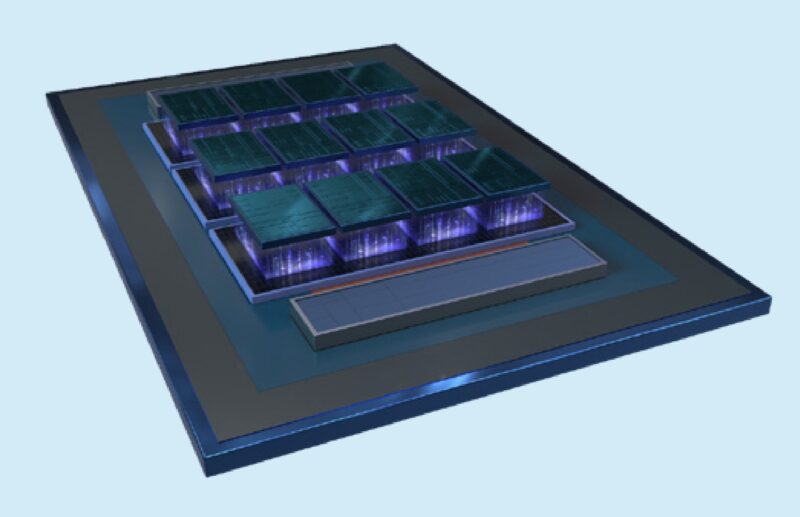

It’s worth noting that the four Intel 18A compute dies are stacked on an active Intel 3 base tile using Foveros Direct 3D. This active base tile has L3 SRAM and I would say it’s reasonable to assume that it will also contain memory controllers for the sake of easy reuse of GNR/SRF IO dies and simply having the memory controllers in the same place.