SiFive has been a major RISC-V player for the past few years. At Hot Chips 2023, the company went into the SiFive P870 processor in quite a bit of detail.

Since these are being done live from the auditorium, please excuse typos. Hot Chips is a crazy pace and this is the last of the day.

SiFive P870 RISC-V Processor at Hot Chips 2023

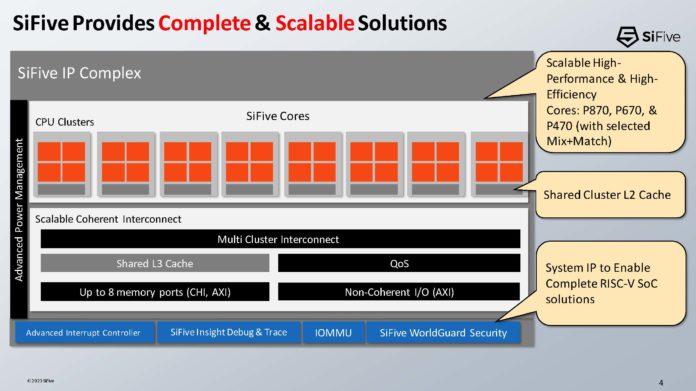

The new RISC-V CPU has standards. That is a big part of the SiFive messaging.

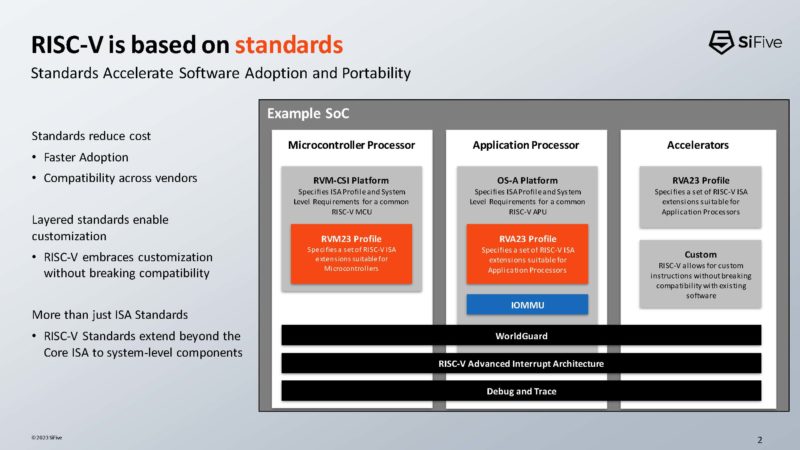

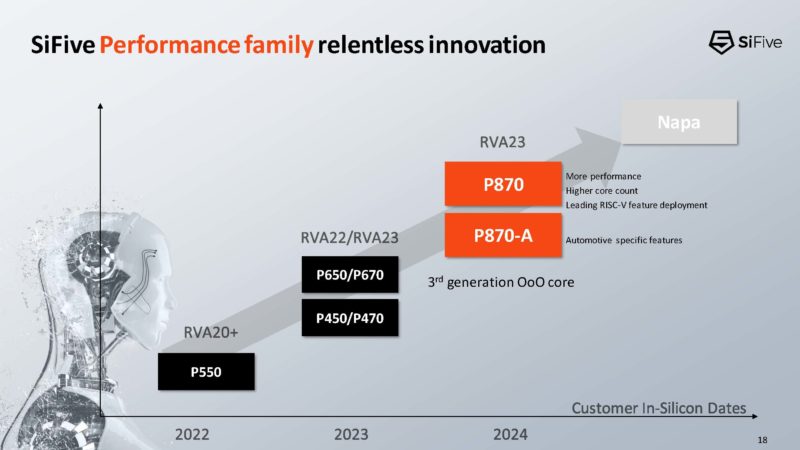

SiFive had its first out-of-order chip in the P550 in 2022. The company now has P650/P670 and the P450/P470. Now, there is the P870 and P870-A. A is for Automotive here.

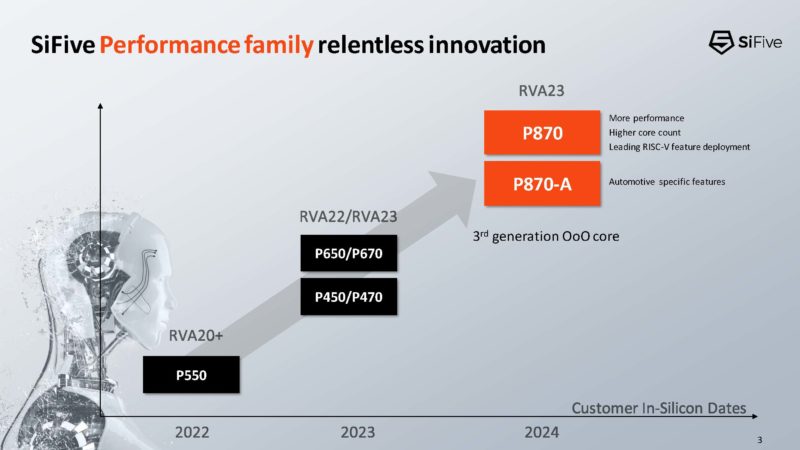

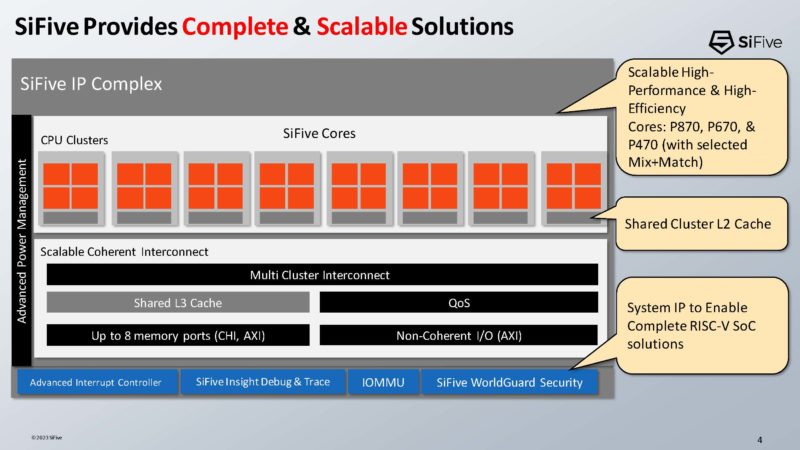

SiFive is building larger and more complex chips now. Something that is different is that the solution utilizes a shared L2 cache. Many Arm CPUs today are working on dedicated L2 caches for cloud workloads.

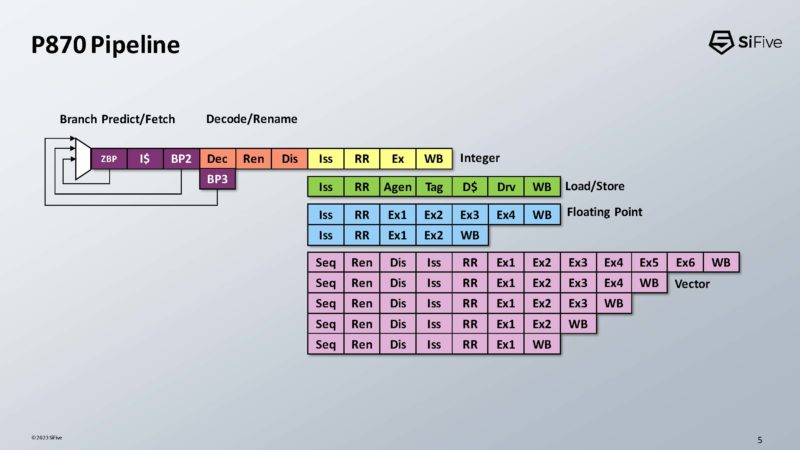

Here is the pipeline.

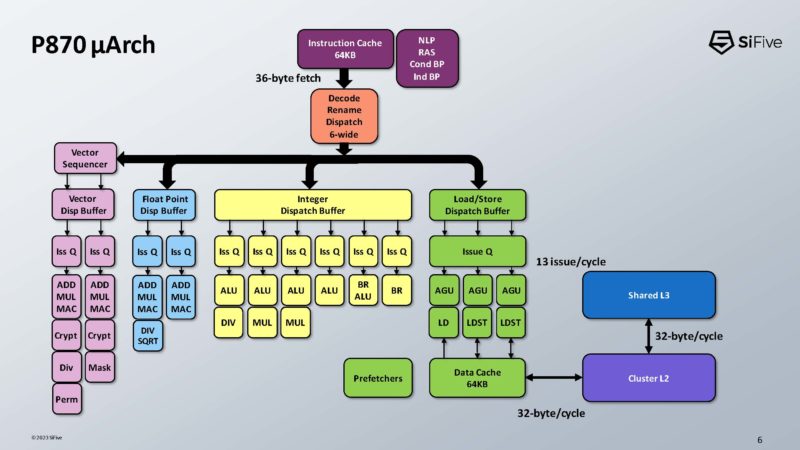

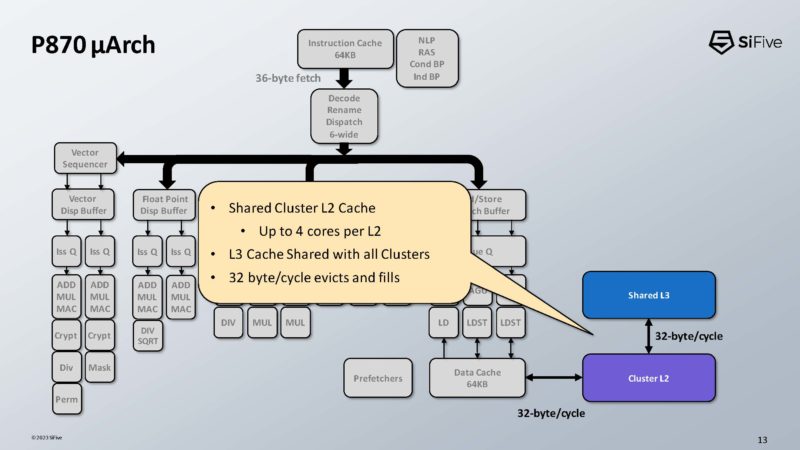

Here is the microarchitecture of the chip. This is more of an instruction flow diagram.

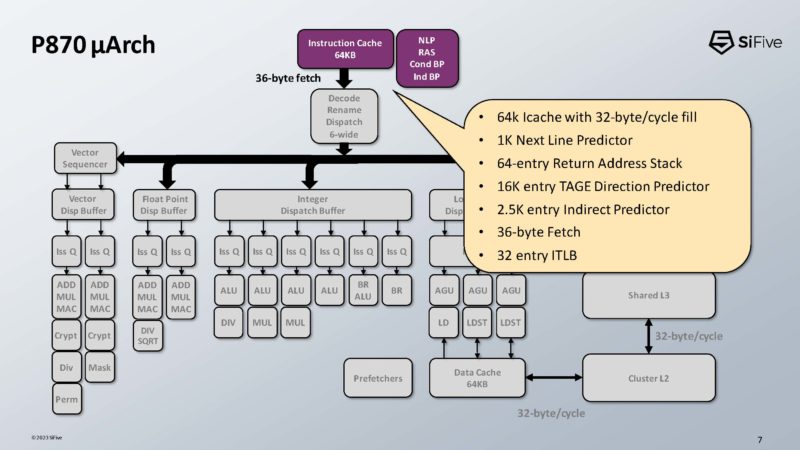

Here is the start of the walk-through on this one starting at the top.

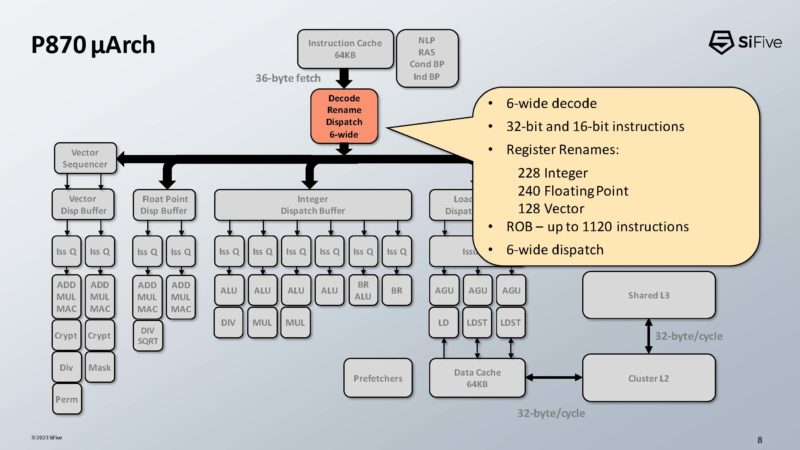

Here SiFive is handling fusion functions here and the ROB of 1120 is being noted as an extreme case. This is basically counting bundled instructions from what it sounds like (maybe this is comparable to 280 in other architectures.

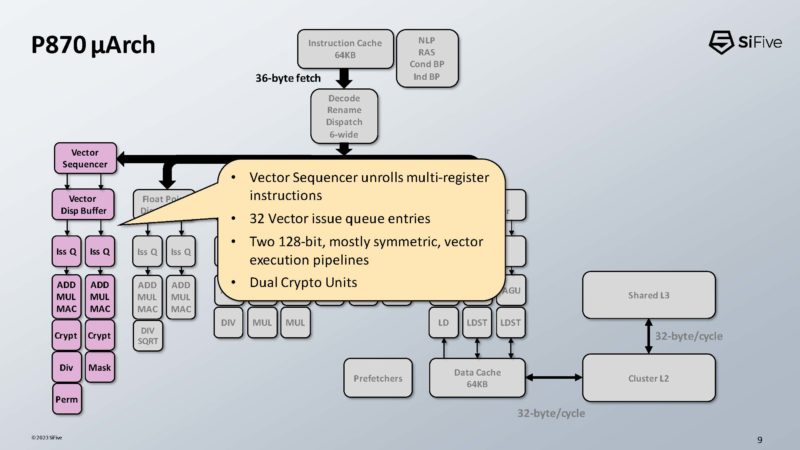

The vector sequencer is being noted as a bit of a unique feature for RISC-V.

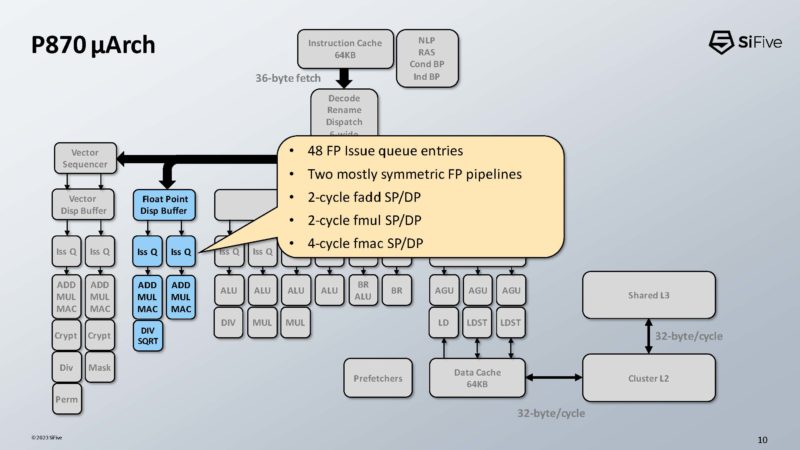

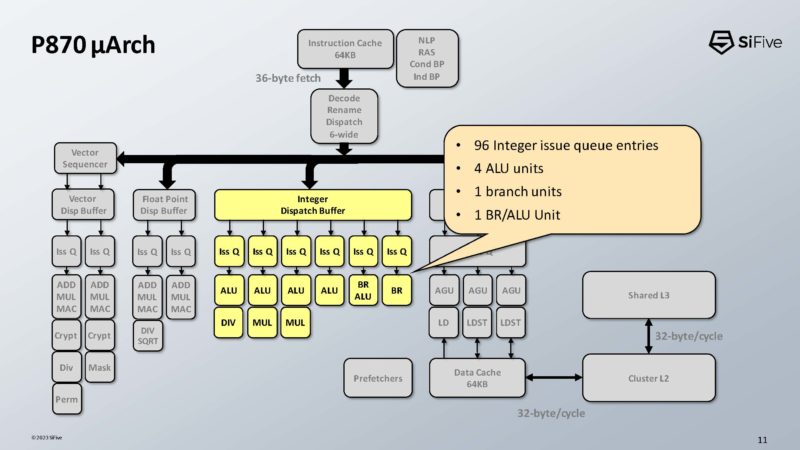

Just noting at this point that this is more complex than SiFive’s old solutions.

Still going with more microarchitecture details that one can read.

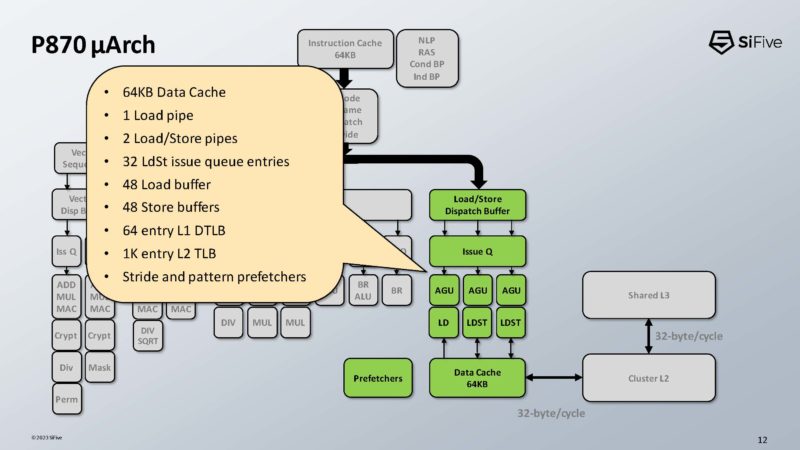

Here are the specs on the load/ store.

L2 cache is non-inclusive but not exclusive.

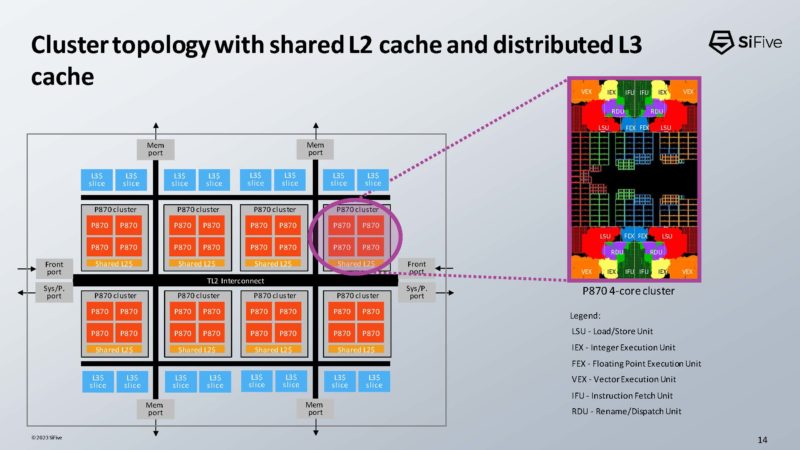

Here is what the cluster topology looks like. L1 with 16-cycle latency to a larger L2. This is designed for data sharing between cores in the cluster. This is a 32-core chip example with 8x 4-core clusters.

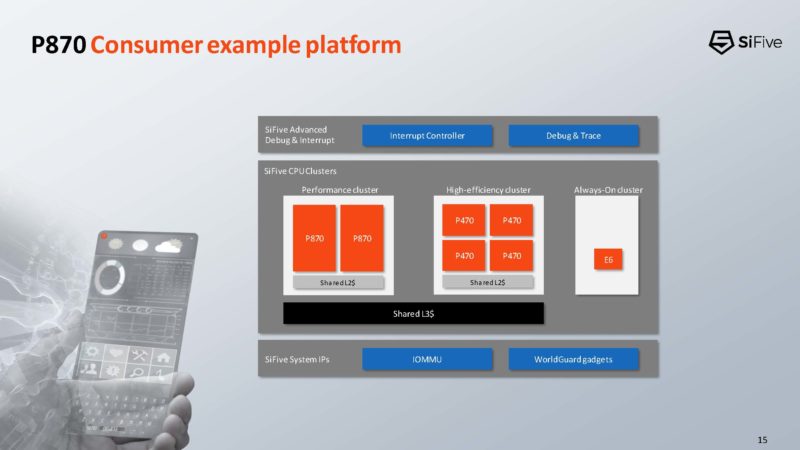

Here is a consumer topology with two P870 higher-performance cores, four P470’s, smaller more efficient cores in a cluster, and then a low-power E6 in-order core for always-on at low power.

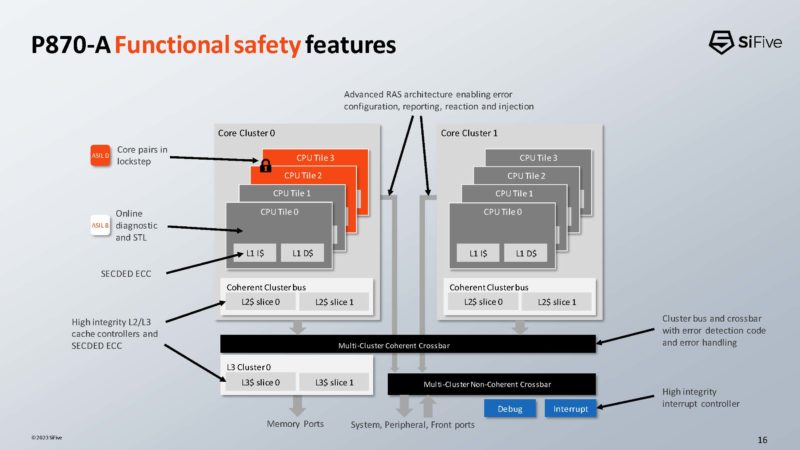

Here is the new SiFive P870-A automotive safety feature slide. Here more focus is on fault detection, reliability, and safety. The P870-A has things like parity in register files, and the caches have ECC as some examples of how this is different.

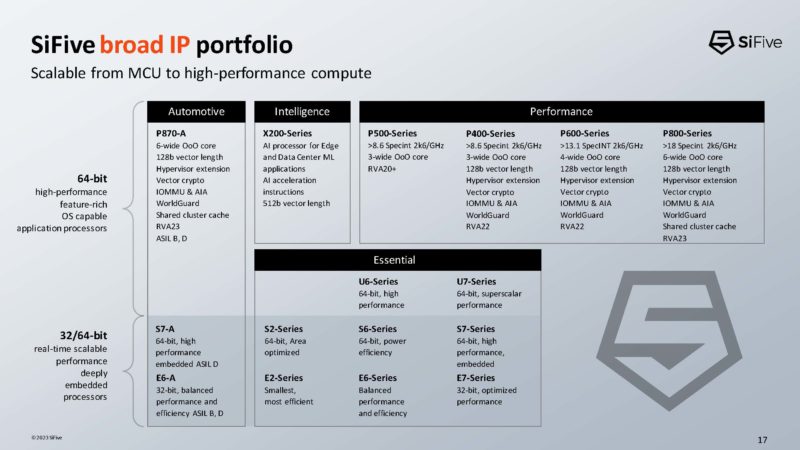

SiFive has a number of different types of IP. Here is a full list. Before seeing this list, I had no idea they had this variety of IP.

The next generation that we will hear about is the Napa core.

We did not get more information on Napa, other than it is a future performance core.

Final Words

This is not a product announcement. The product announcement will be in a few weeks apparently and the clock speeds are expected to be in the 3GHz range. This was cool to hear about. RISC-V has a lot of momentum and SiFive has been a big player. SiFive is almost starting to feel like it is trying to become the Arm of the RISC-V market but with RISC-V as an ecosystem being open.