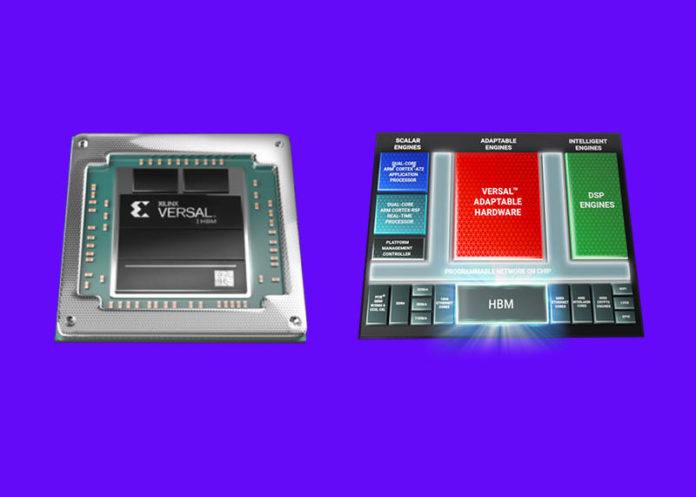

Xilinx has a new, yet quite expected next-generation product coming. Specifically, it is integrating its Versal ACAP (Xilinx’s next-gen FPGA) with HBM memory. HBM integration with FPGAs is nothing new, so this is something many will have thought already happened.

Xilinx Versal HBM

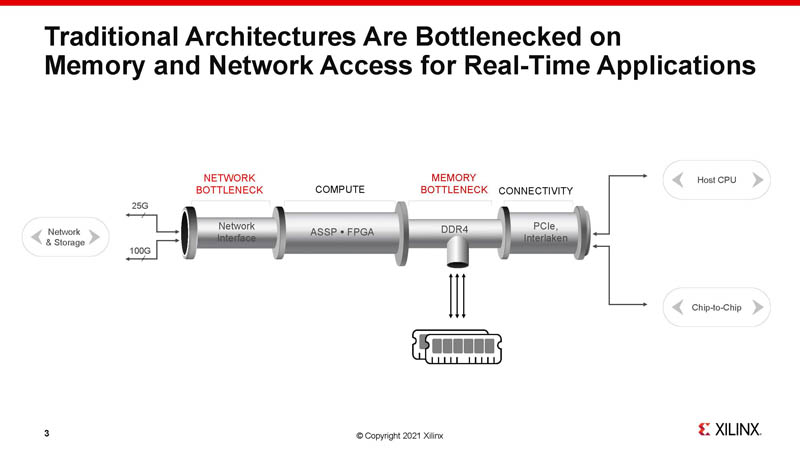

The basic setup is that in many compute elements the network interfaces bring a large amount of bandwidth and that, plus the memory bandwidth constraints of DDR4 can cause bottlenecks. This is not referring to an Intel Ice Lake Xeon or AMD EPYC processor with a 10GbE NIC, but is instead referring to applications where SoCs often have two DDR4 channels but also have several hundred GB/s of NIC bandwidth. Actually, the Mellanox NVIDIA BlueField-2 DPU can be seen as an example of this that you can readily buy today.

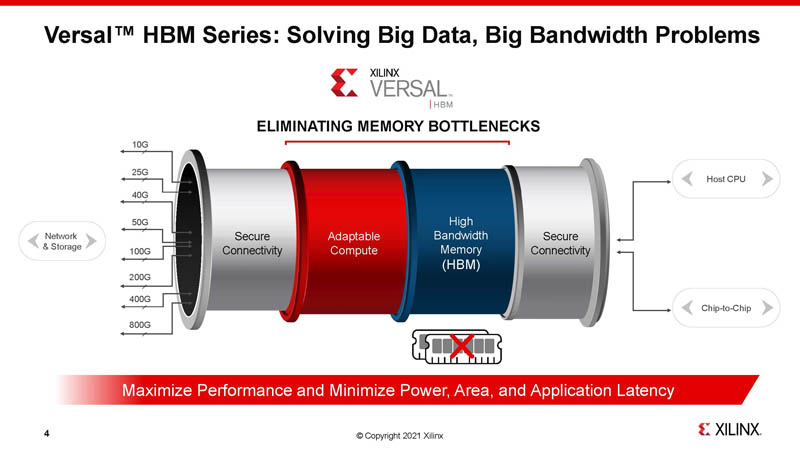

Adding HBM allows for faster and lower latency memory access which in turn increases performance.

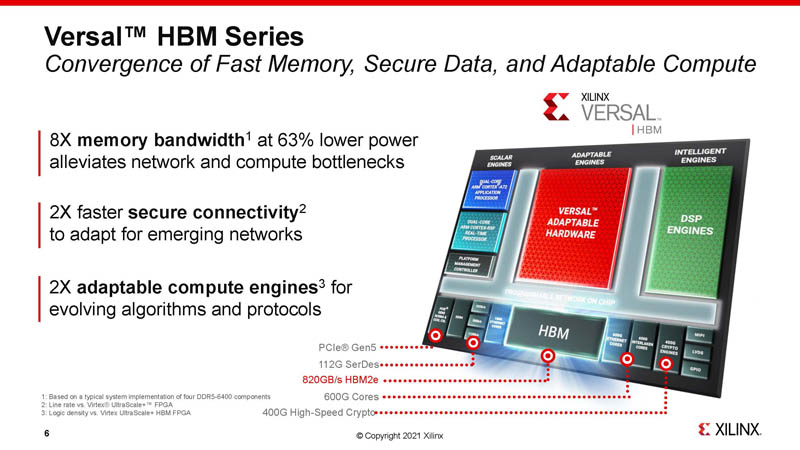

The Versal HBM series is designed to be one of the highest-end products from Xilinx. With 8x the memory bandwidth of a four DDR5-6400 implementation.

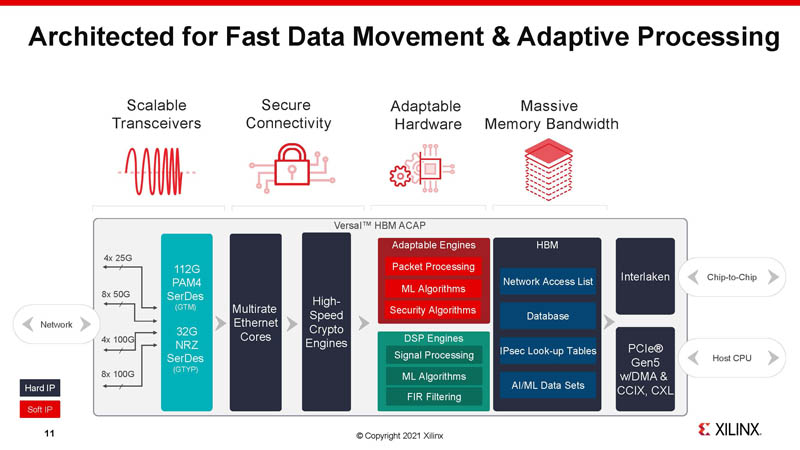

Aside from the HBM, we have SerDes for over 2Tbps of networking on the higher-end SKUs. There are various accelerators for cryptography, signal processing, and AI inference. Versal ACAPs also have Interlaken and PCIe Gen5 with CCIX and CXL for connecting to larger systems.

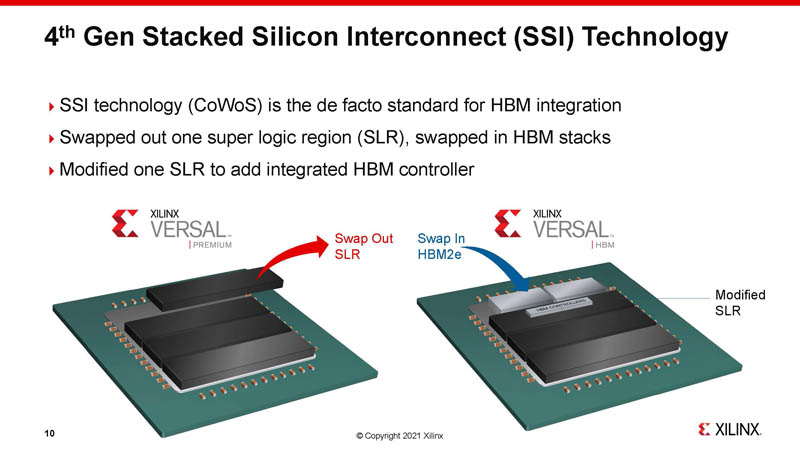

Adding HBM2e Xilinx says is relatively straightforward. It swaps one of its Super Logic Regions (SLR) out for HBM2e stacks.

Target markets seem to be higher-end applications. Xilinx makes a wide range of chips from the lower-power Xilinx Kria KV260 SOM solutions to high-end chips that sit it radar arrays and networking gear. HBM is generally a higher-cost component so that put this series into the higher-end market segment.

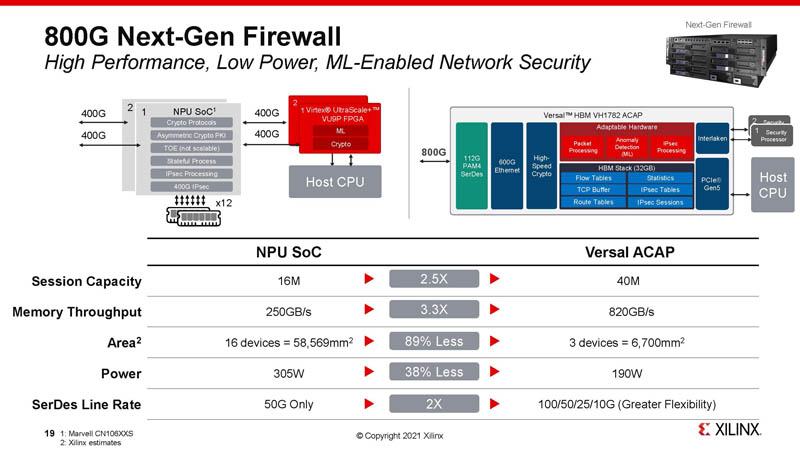

An example is showing off an 800GbE firewall. Xilinx is pitting its next-gen VH1782 ACAP versus a Marvell CN106XXS, Ultrascale+, and a host CPU. We covered Marvell’s next-gen DPU products for this space that may change this picture in Marvell Octeon 10 PCIe Gen5 DPUs announced.

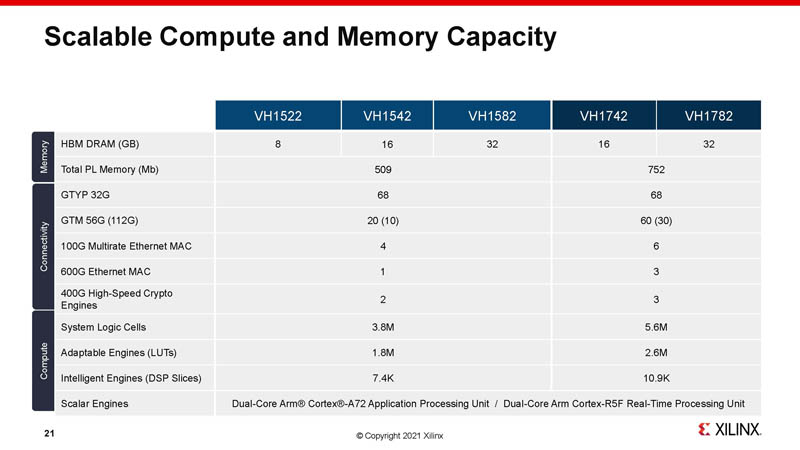

We skipped a few slides that basically just said HBM2e offers more bandwidth and lower power per bit than traditional DDR4/5 solutions. Here are the actual SKUs being launched where one can see that the VH1782 is the higher-end SKU for Xilinx.

Final Words

Since Intel Agilex has been pushing its HBM support, and Xilinx had UltraScale+ with HBM it makes sense that Xilinx’s next-gen ACAP (or is it current now?) solution also has a HBM option.

This is a product that will come to market in the future, but the company says that one can start with the Xilinx Versal Premium and then the lift to utilize HBM is relatively small once the HBM parts are available since it is all using its ACAP architecture. Still, with sampling in 2022, this is still some time out from being a product we see in servers and appliances.