Marvell is trying to get its name out there as not just a chipmaker, but as a partner for solutions beyond its own IP. One of the big benefits it is touting is its relationship with TSMC which will bring the next-node (5nm) earlier than with Intel. Most folks looking for a chip partner will likely know that Intel has faltered on process transitions. That is all over not just the technical press, but also the financial press as well. With 5nm, Marvell is aiming to expand its share of custom and semi-custom solutions.

Marvell’s Strategic Shift

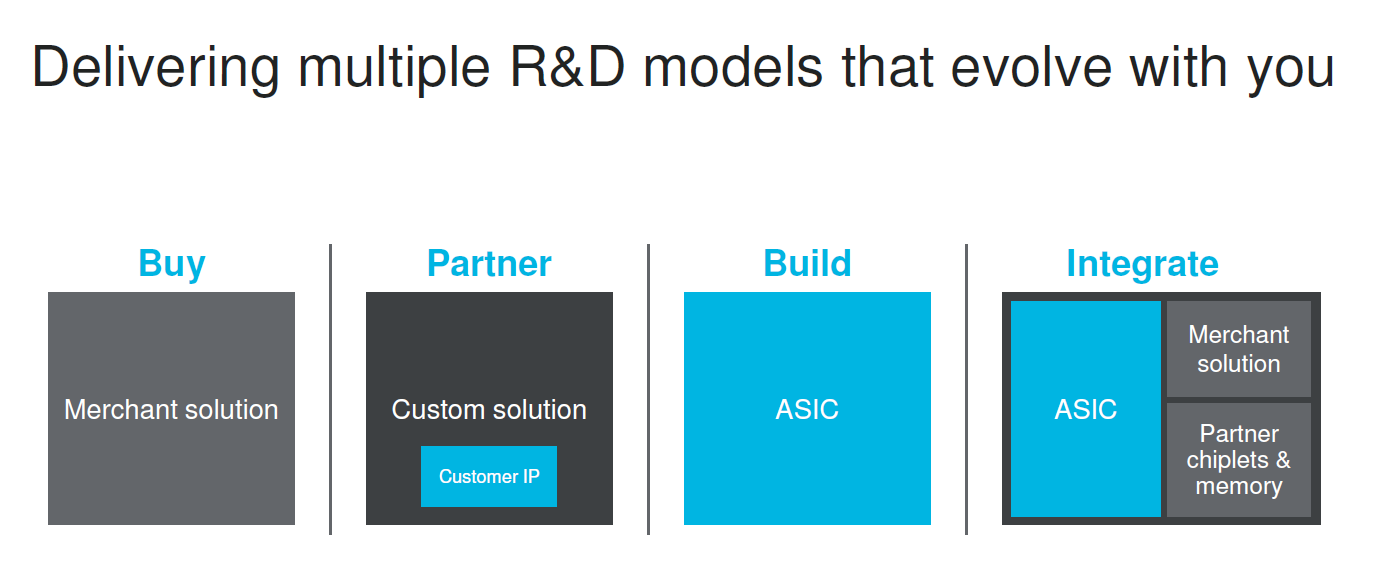

One of the biggest changes at Marvell is a move towards being a chip integrator, not just a designer. While it still has its off-the-shelf solutions ranging from Marvell ThunderX3 to OCTEON and its networking portfolio, Marvell is moving to a strategy of creating custom chips for customers including that IP.

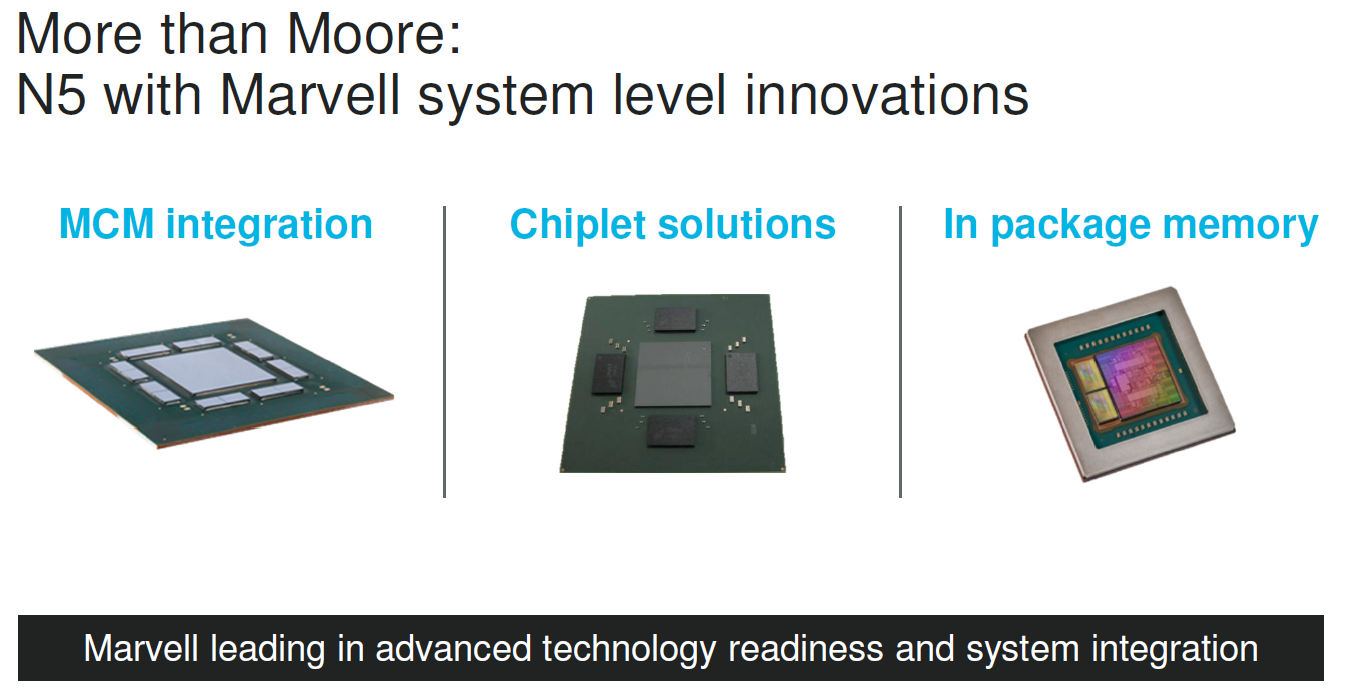

A big part of this is offering a range of Marvell solutions to integrating IP and chiplets into custom solutions for customers. Marvell is highlighting its packaging and integration capabilities, perhaps pressured by Intel’s newly disclosed future methodology.

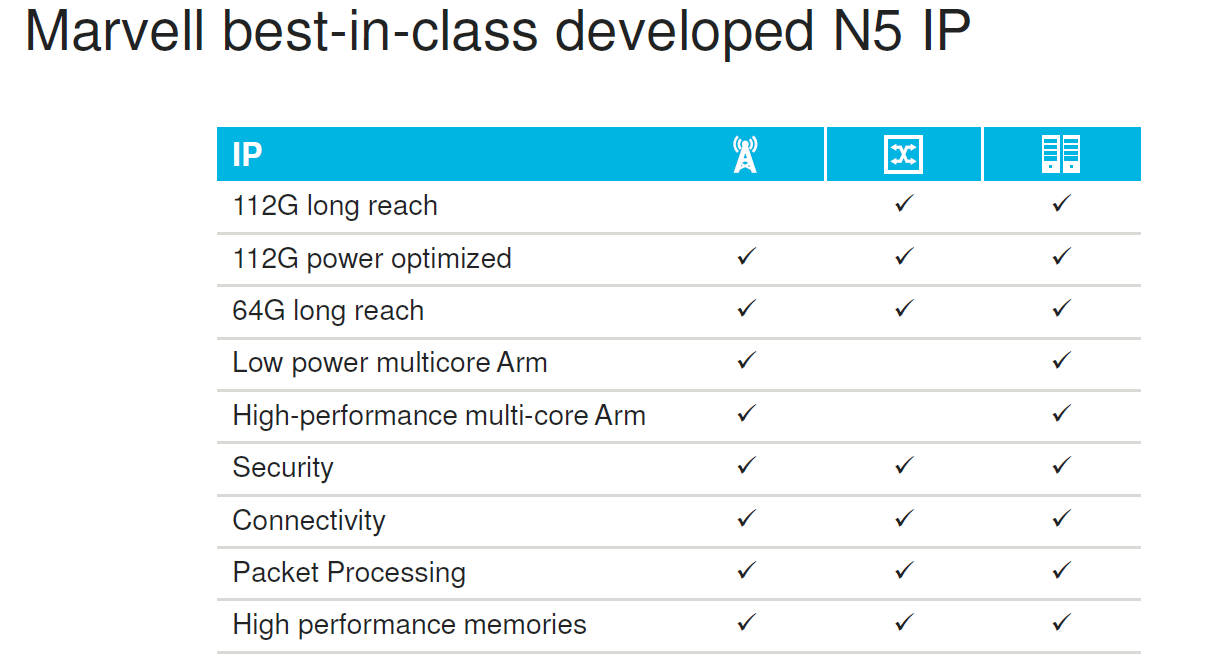

Aside from its work on its own products with TSMC where it needs to create different types of packages, Marvell also is touting the IP portfolio that it has at the ready to help customers.

If a customer needs assistance creating a custom solution, perhaps because it has a custom ASIC chiplet, but needs additional IP, Marvell is looking to package the solution with its IP.

TSMC N5 Improvements

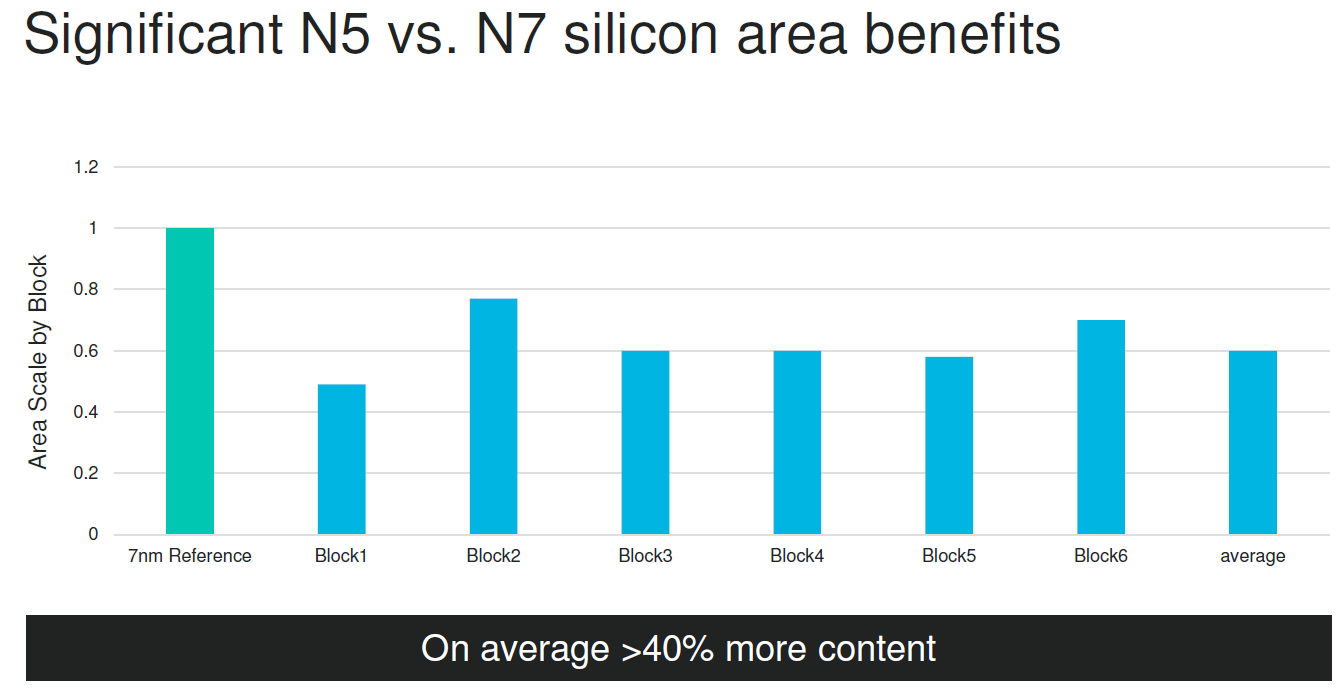

As we would expect, we are getting additional density benefits from N5. This helps reduce area. For a lot of networking and 5G applications, this can actually impact a go/ no-go decision for making a new chip.

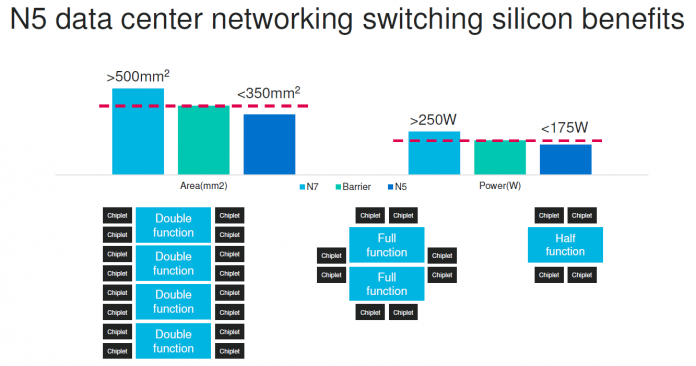

Marvell says N5 will offer not just a 40% reduction in silicon area, but also a 40% power savings over current-generation N7.

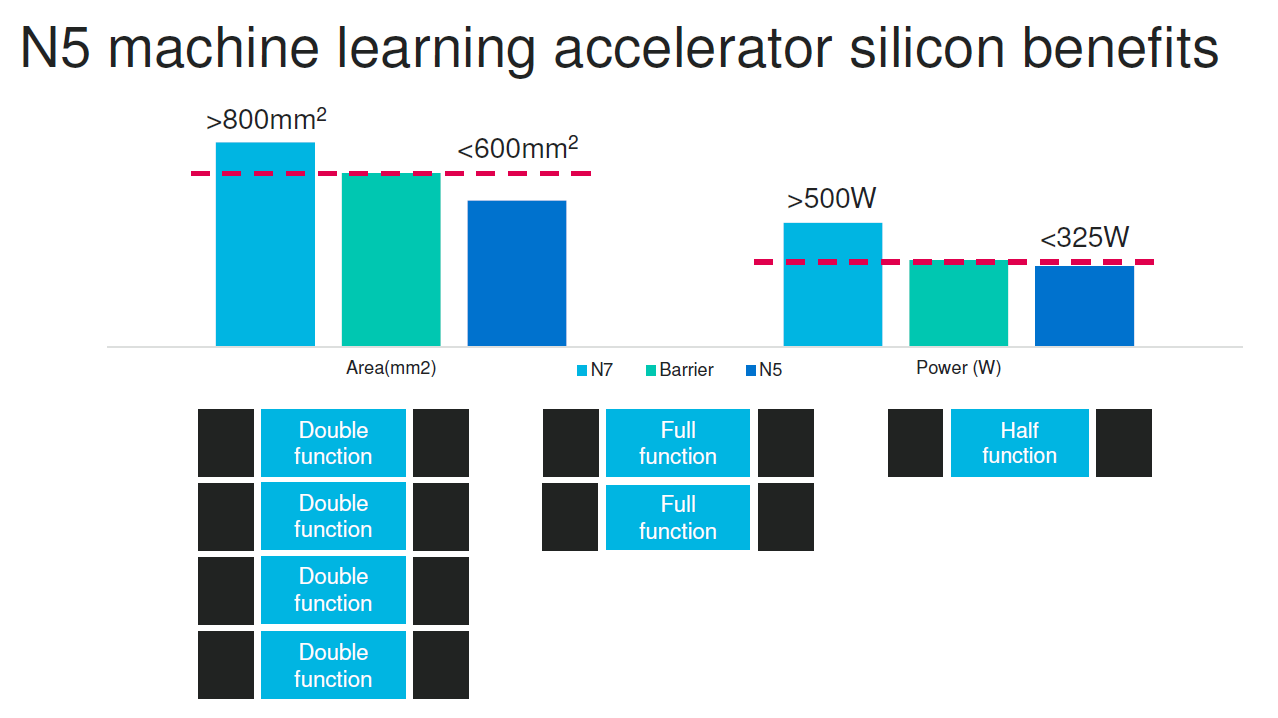

Putting this together, Marvell has a number of examples. Here, Marvell is showing different packaging using chiplets and is using a barrier condition for machine learning accelerators where perhaps on N7 chips would be too big or use too much power, but with N5 they become feasible.

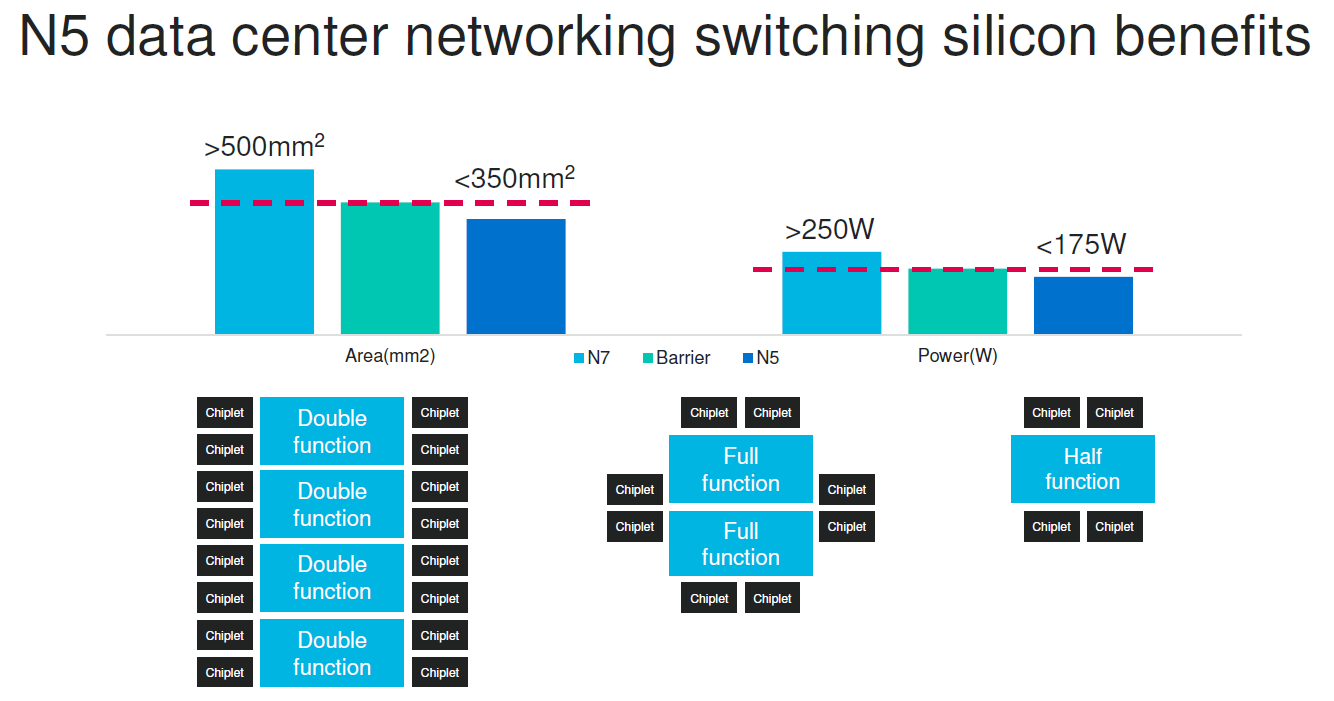

We already covered how Intel Tofino2 is using multi-chip packaging and even saw the setup with silicon photonics in Intel’s lab this year. Marvell is showing it can do something similar, again using the concept of this boundary.

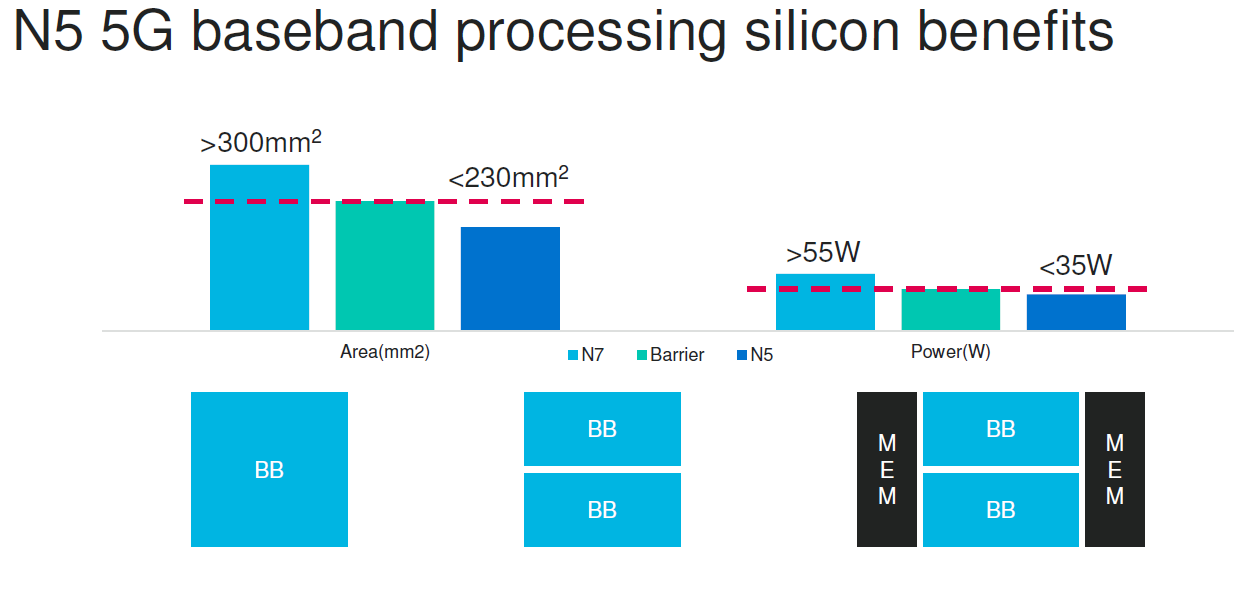

Another key market for Marvell is the 5G baseband market. Here the company is focused on providing silicon for 5G service providers inking deals with companies like Samsung. We covered this in our New Marvell OCTEON TX2 and Fusion CNF95xx 5G SoCs piece. There, many of the 5G equipment manufacturers will have their own IP whether chiplet or otherwise that they want to be integrated with some of Marvell’s IP.

This boundary condition makes sense, but realistically it is saying that we can make more powerful chips using N5. Those boundary conditions limit chips at every process node so they are well-known and everyone in the market is working around them.

Final Words

Marvell is going to adopt TSMC 5N. Going to Marvell will likely mean that smaller run outfits will have a better chance of getting 5N wafer capacity than if they go alone as a small customer. Still, if you are leaning on Marvell as your partner and your competitor is big enough to use TSMC directly, then you are staying relevant rather than getting access to something new. TSMC 5N is differentiated from Intel, Samsung, and others, but TSMC is in the business of building chips for third parties. The real benefit of going with Marvell seems to be the ability to leverage Marvell’s IP blocks and chiplet designs as well as their ability to put chiplets together.