At Hot Chips 32 (2020), Intel is revealing more about the Ice Lake Xeon generation or Ice Lake-SP. The “-SP” is for Scalable Processor which is somewhat fun to know given that this is a 1-2 socket part not the 1-4+ socket parts the “Xeon Scalable” line was named for. We are going to discuss some of the disclosures. We will also update this piece as the HC32 talk happens.

Intel Ice Lake-SP Xeon High-Level

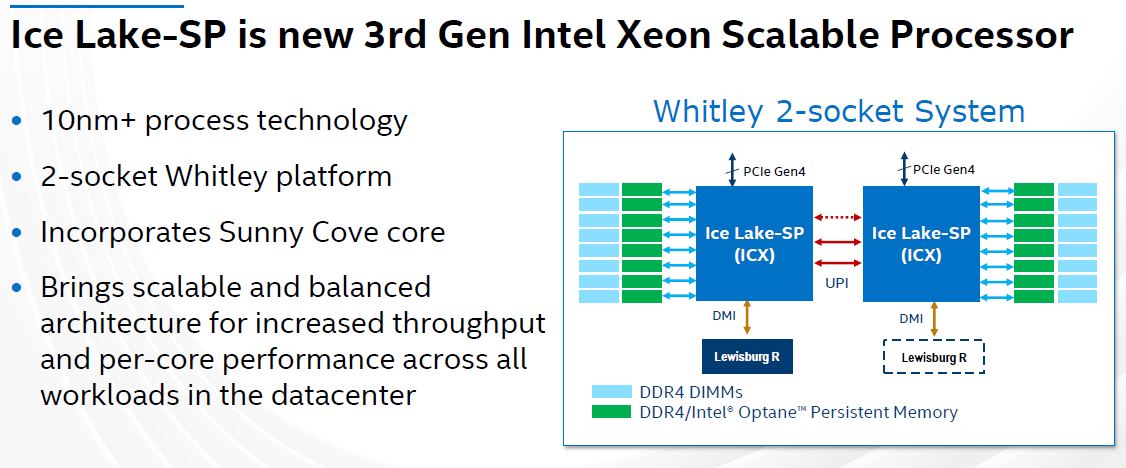

Intel has a nice slide on the Whitley platform. “Whitley” is the codename for the platform that takes Ice Lake-SP generation CPUs.

We are a little surprised to see “10nm+” process technology referenced here. Intel, at Architecture Day 2020, just disclosed they are no longer going to use the “+” and instead use terms like 10nm SuperFin and Enhanced SuperFin.

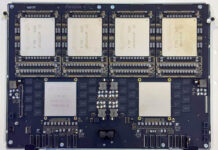

Here is what the platform looks like in an Intel testbed that we saw at Intel Shows Ice Lake Xeons and Talks Sapphire Rapids and Xeon D.

This is a different platform for Intel. After canceling the Cooper Lake mainstream part, Whitley is a single chip generation platform. You can learn more about the implications in The 2021 Intel Ice Pickle How 2021 Will be Crunch Time. We also have a video on that one:

One of the big new features is a new microarchitecture with the 10nm process and PCIe Gen4 support. Let us get to those features.

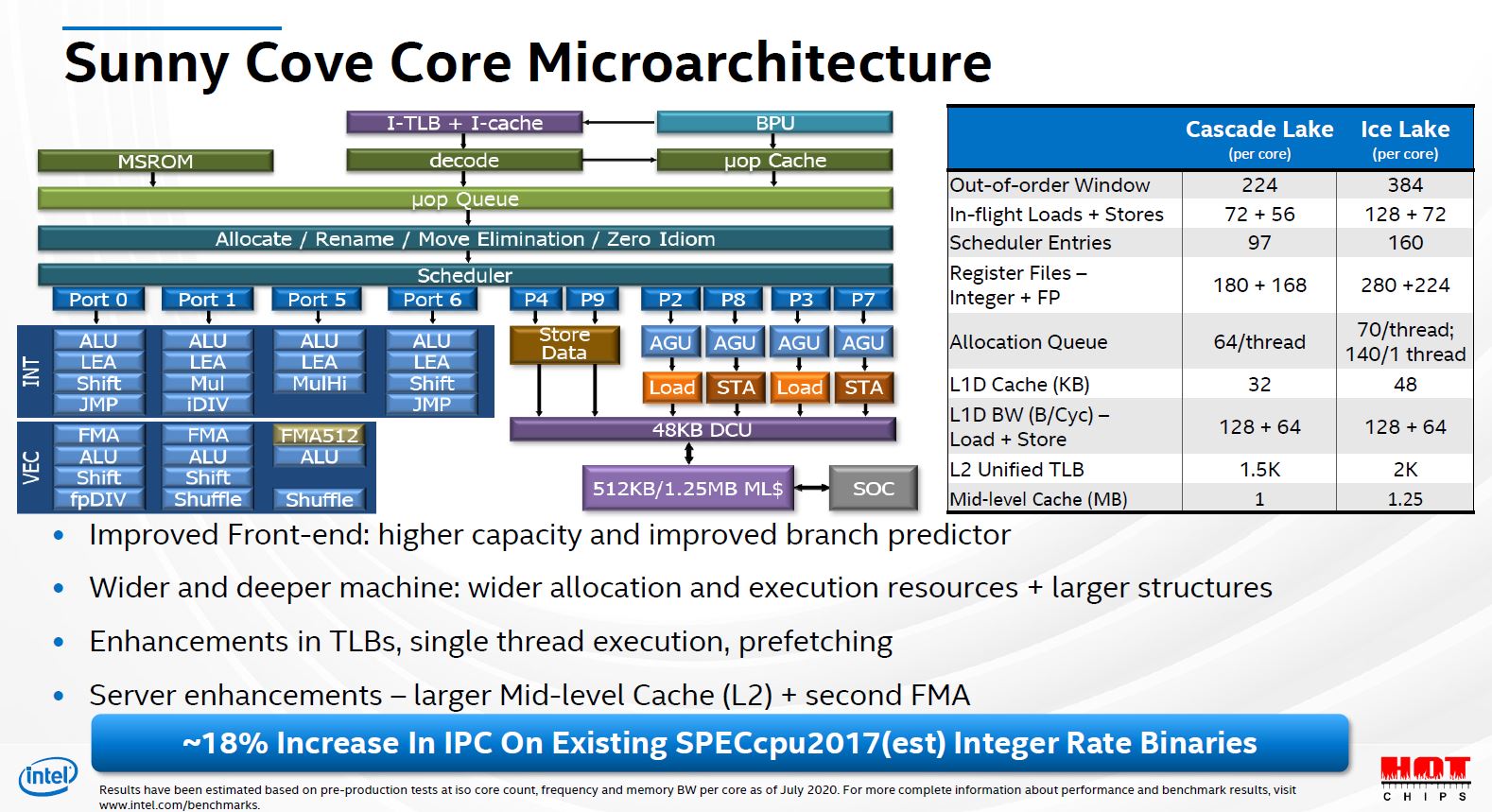

Ice Lake Sunny Cove Microarchitecture

We were hoping to get a massive download on the new confidential computing and SGX enhancements in Ice Lake-SP. We expect SGX features will be one of the big SKU stack differentiators in the Ice Lake Xeon era, but perhaps that discussion will happen later. Instead, we have some other details around the Ice Lake-SP. Those details center around the Sunny Cove microarchitecture. If it feels like you have seen Sunny Cove before on STH, that is because we covered it in Intel Sunny Cove Microarchitecture Details almost two years ago. Also, last week at Intel Architecture Day 2020.

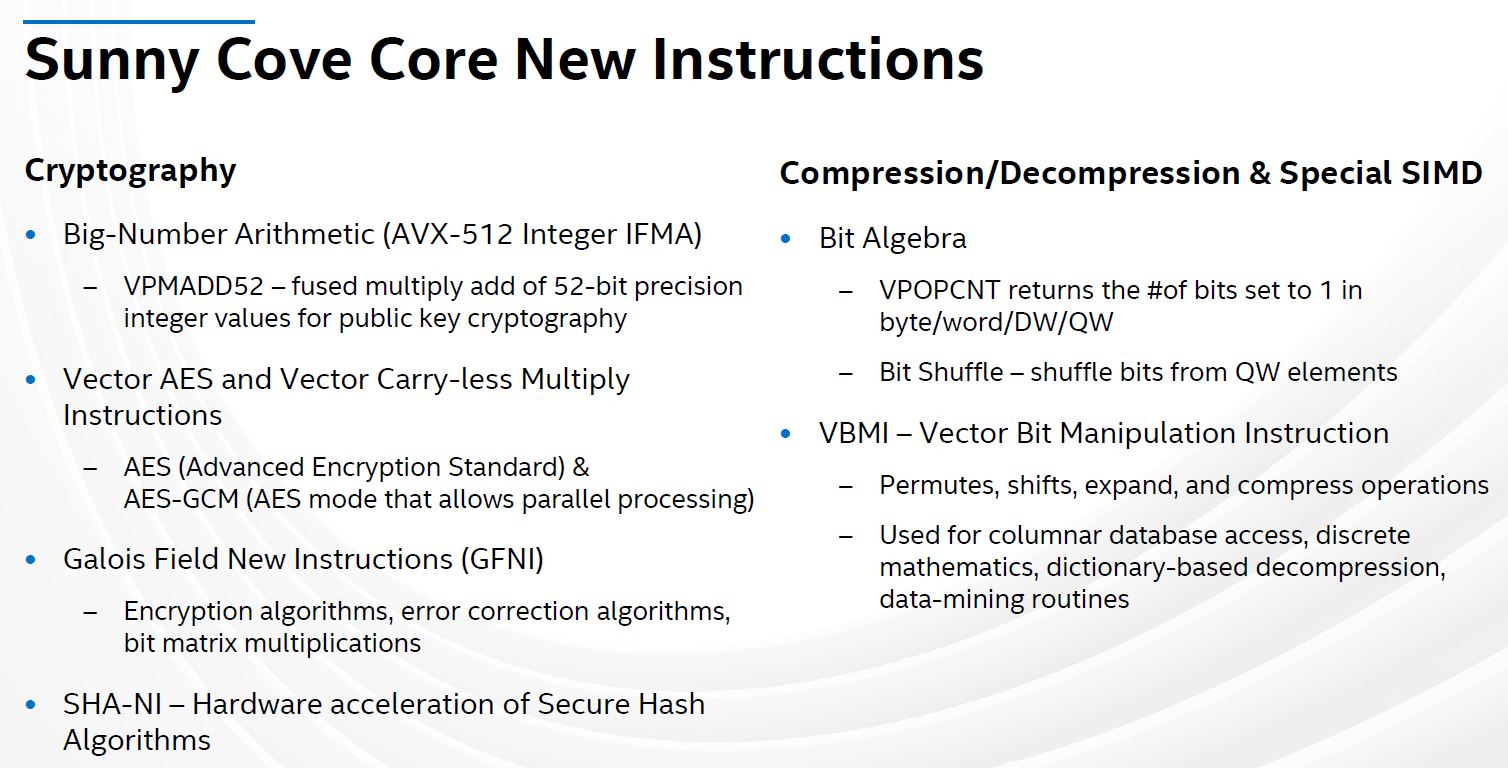

Some of the new features are a much wider and deeper pipeline with better prefetchers and branch predicters. Intel is also moving to slightly larger 1.25MB L2 caches. We do not expect when L3 cache details are out that Intel will match AMD EPYC 7002 “Rome” levels of L3 cache. Intel also is adding new instructions.

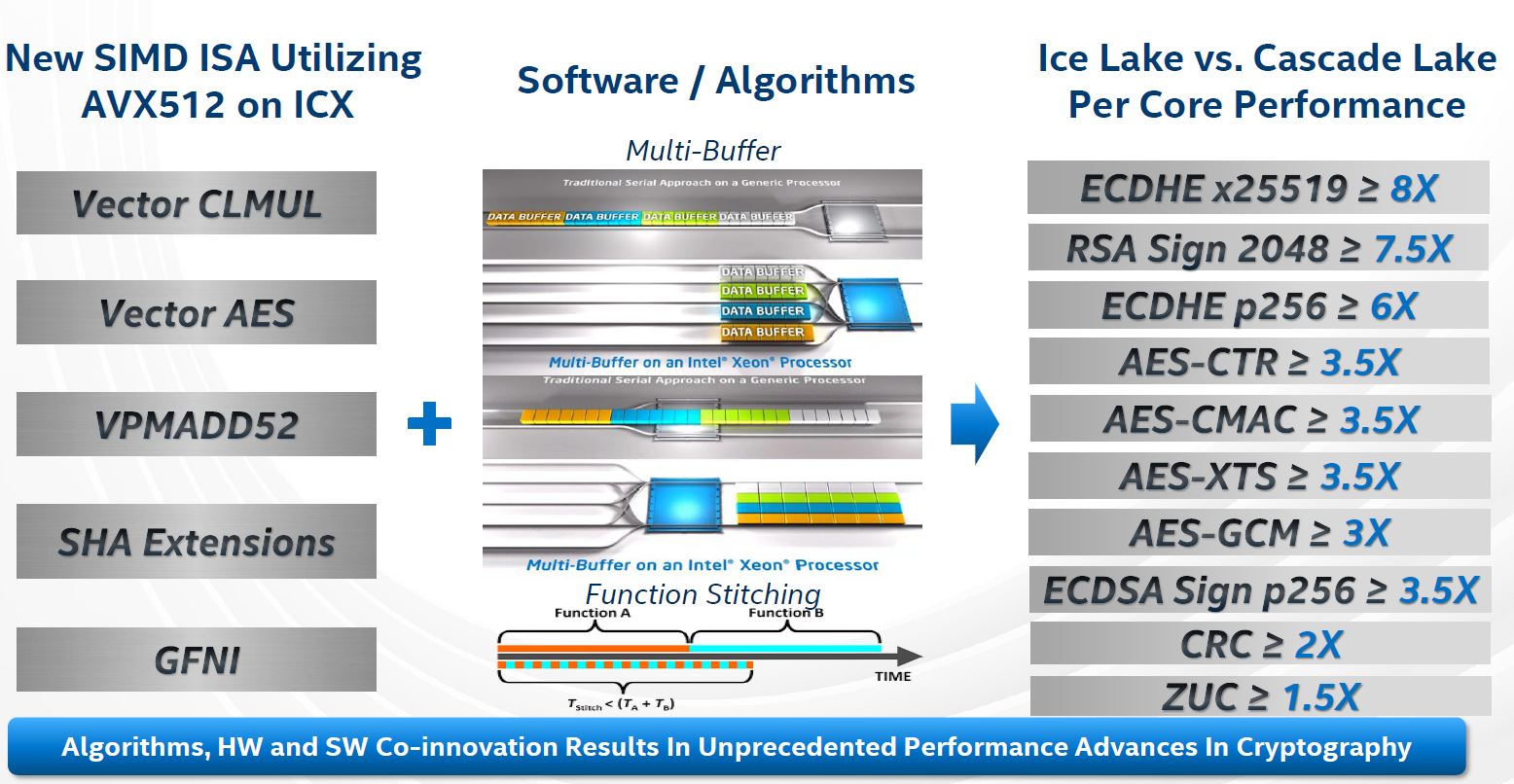

Part of the work is to increase the crypto performance of Ice Lake. One of the biggest features of Ice Lake-SP will be its focus on secure computing or confidential computing. As a result, Intel is increasing the cryptographic performance of the CPUs.

Reading into Intel’s strategy here, they are doing a lot more work on this type of enhanced acceleration versus AMD. AMD is more focused on building more cores. Intel is focused on providing more acceleration in its chips.

Something that is interesting here is that the company discussed how much better Willow Cove is versus Sunny Cove on the desktop side with Tiger Lake. We wish Intel used different server codenames.

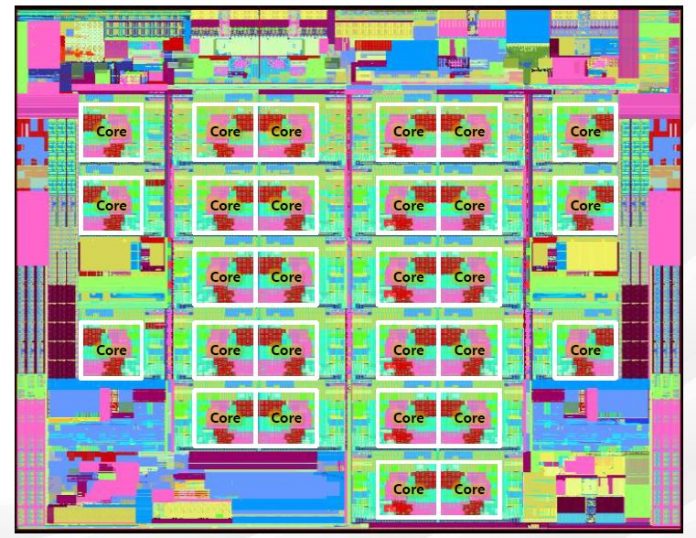

Intel Ice Lake-SP SoC

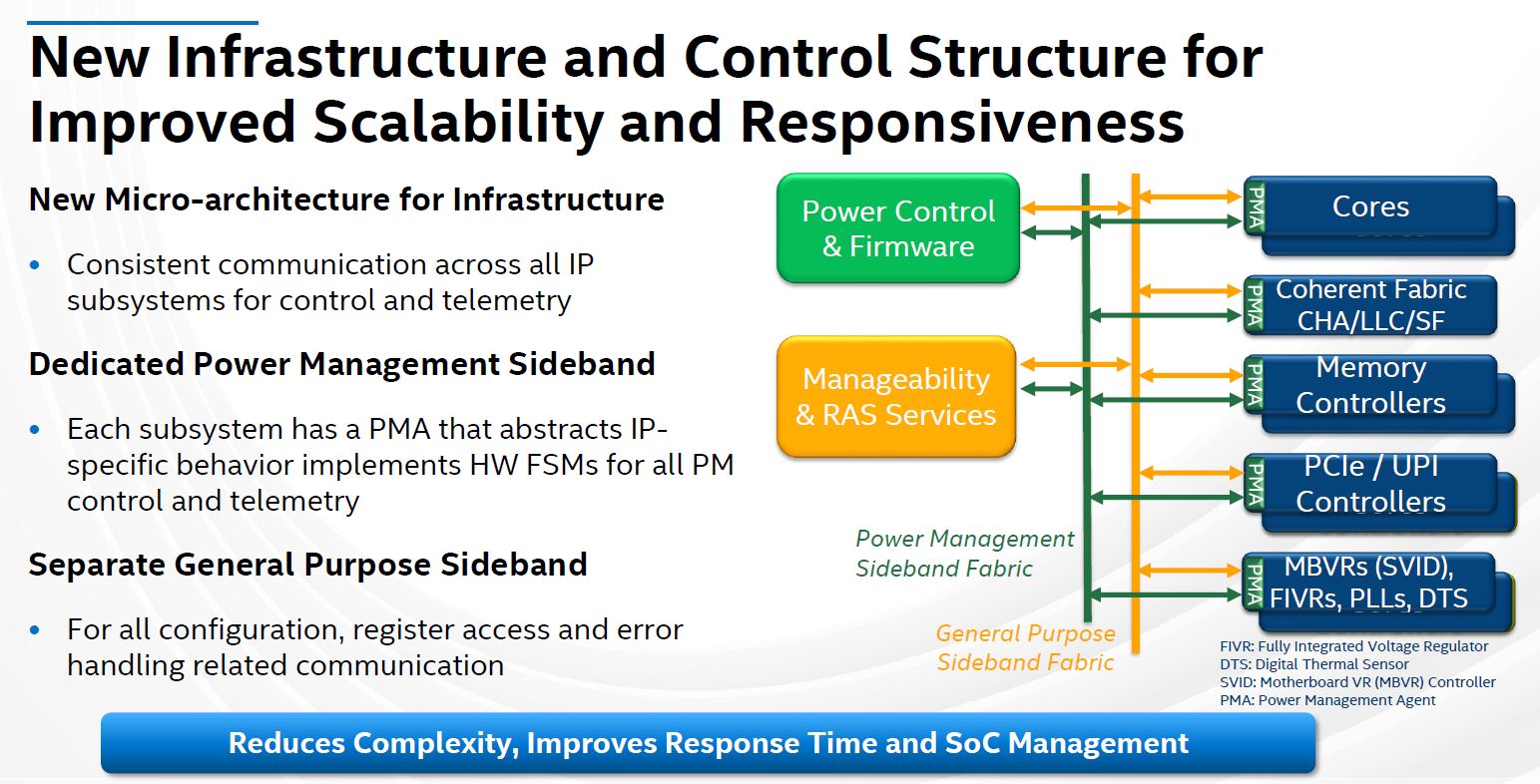

Intel is putting a lot of focus on some of the smaller architectural nuances of their new SoC. Intel will be behind on raw core count in this generation, so it needs to show how its cores and chip will be more efficient.

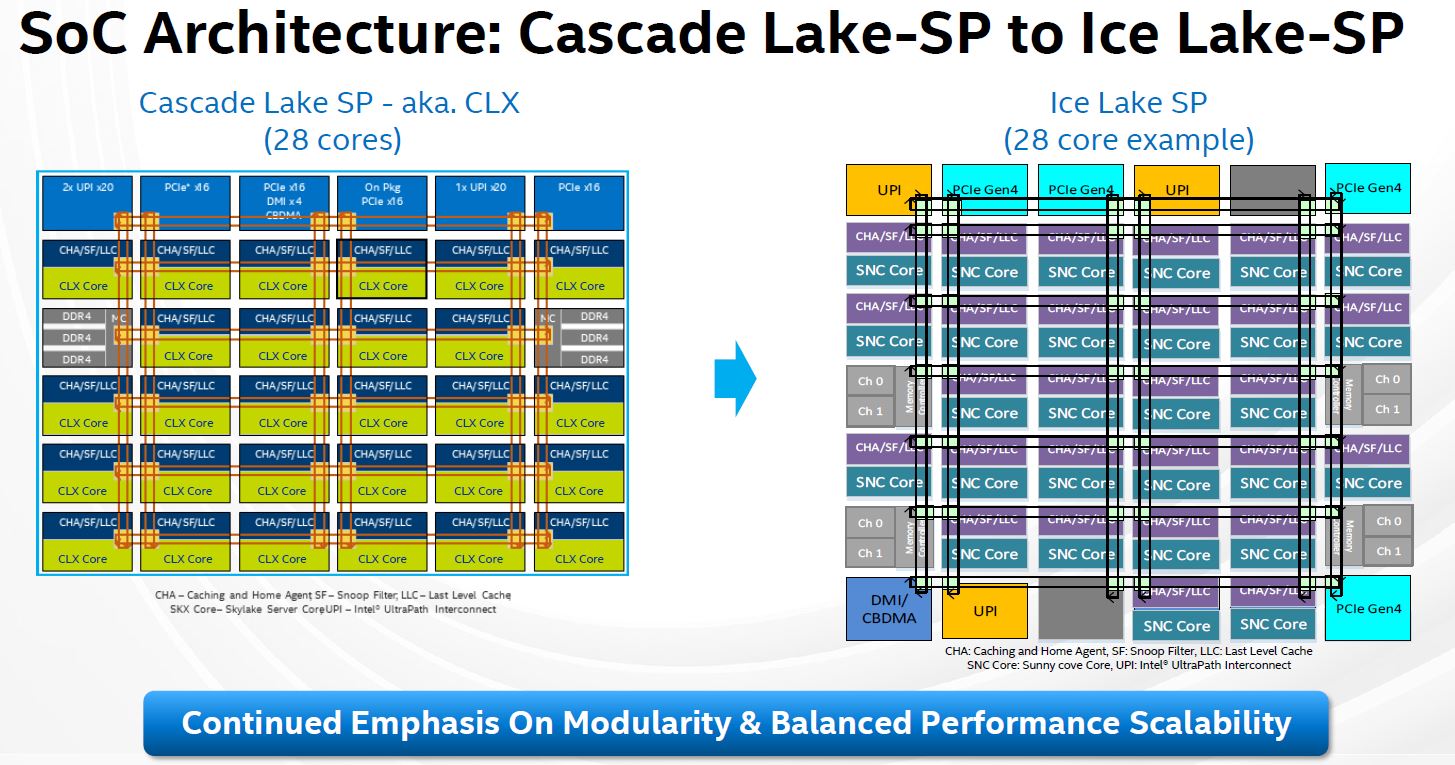

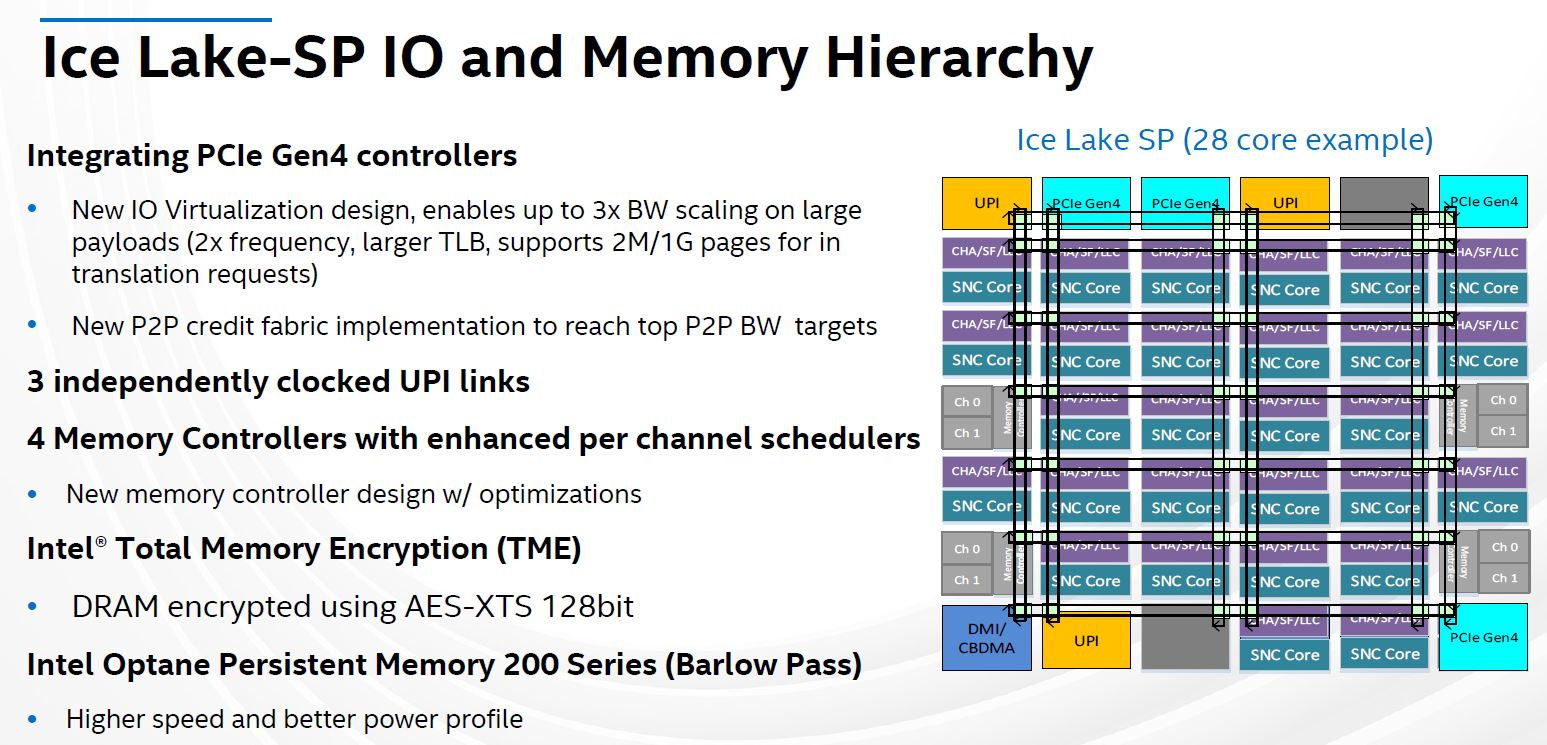

We first covered Intel’s switch from a ring to a mesh in The New Intel Mesh Interconnect Architecture and Platform Implications. That remained similar between 2017’s Skylake-SP and 2019’s Cascade Lake-SP, and even to 2020’s Cooper Lake. With Ice Lake-SP, it needs to change. For example, Intel needs to add PCIe Gen4 hops to handle mode PCIe lanes. It is not on this diagram, but to fit 64x PCIe Gen4 lanes, these four PCIe Gen4 controller blocks are likely x16 each.

On the memory side, there are now four memory controllers and thus hops on the mesh instead of two previously. In essence, Intel is moving from 2 controllers x 3 channels each to 4 controllers x 2 channels each with this generation. With this generation, Intel will finally enable Memory Mode for the Optane PMem 200 series that is not available on the Cooper Lake platform. Total Memory Encryption is enabled on this platform which will help Intel catch up with other offerings and provide platforms to be competitive with Google Cloud Confidential Computing Enabled by AMD EPYC SEV when combined with SGX enclaves.

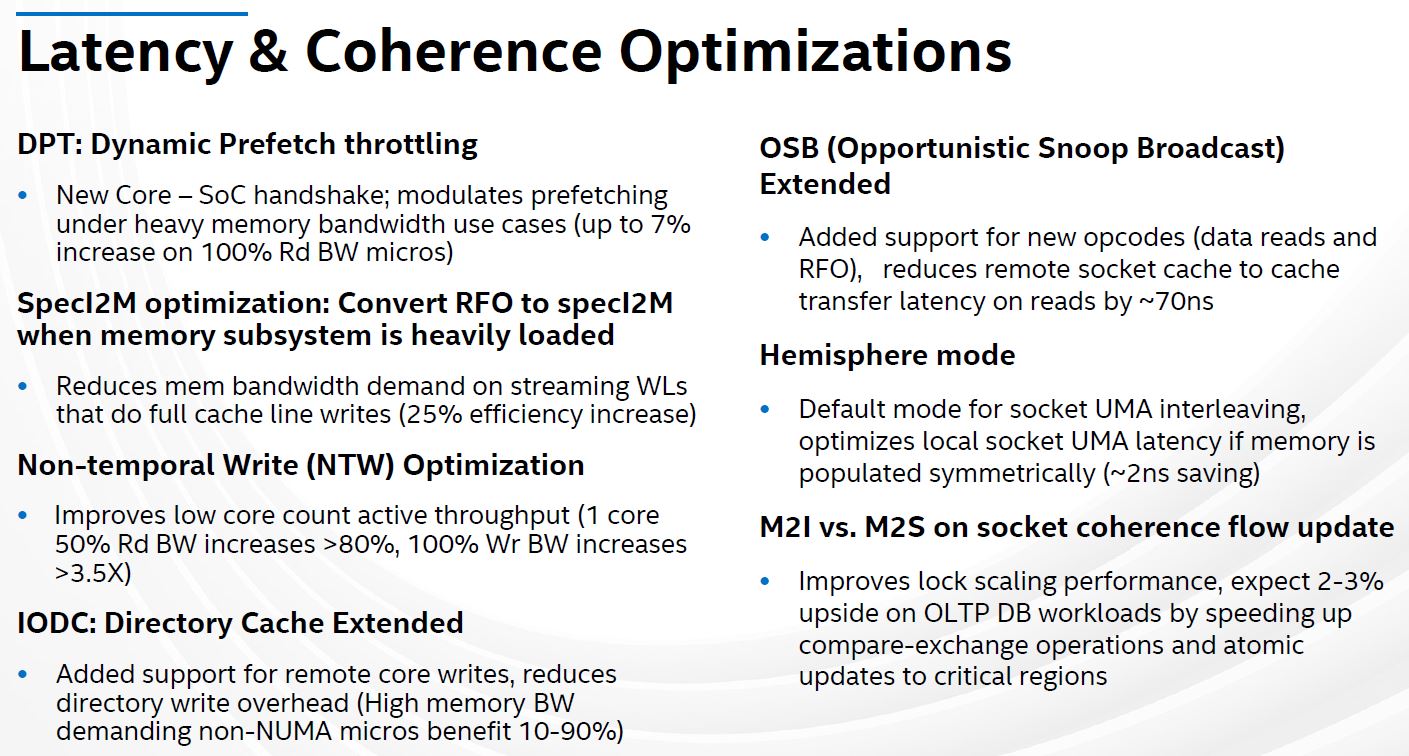

Intel is focusing a lot of effort on their latency and coherence optimizations. This is just a wall of text so we will let our readers simply read these.

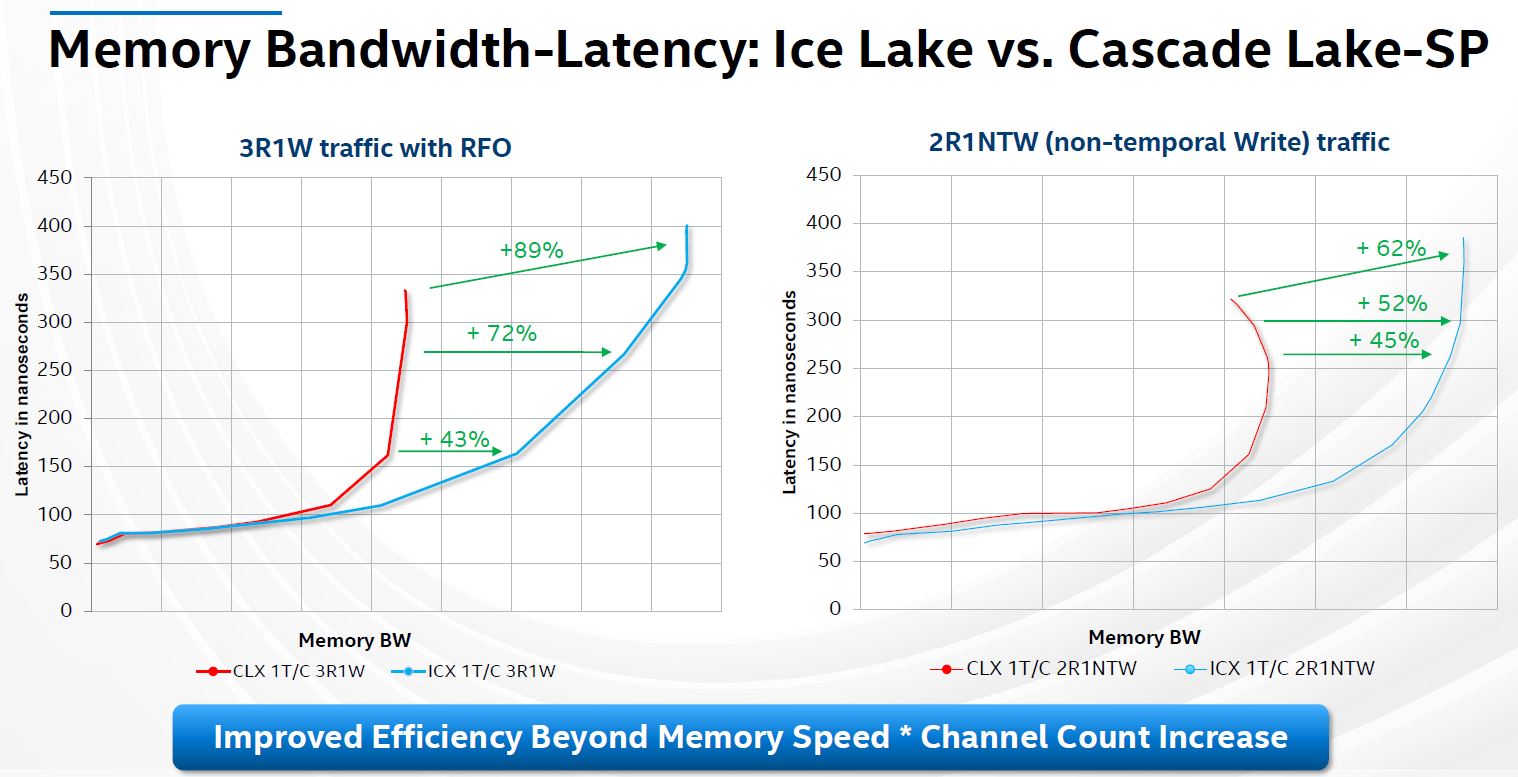

Here we have something interesting. Intel gets a fairly large benefit in terms of memory bandwidth for this generation. With 8 channels, Intel gets 33% more just from that. Intel also will move from DDR4-2933 in Cascade Lake-SP to DDR4-3200 in Ice Lake-SP which is over a 9% gain as well. Intel is saying that it gets more benefit than those two sources of additional bandwidth.

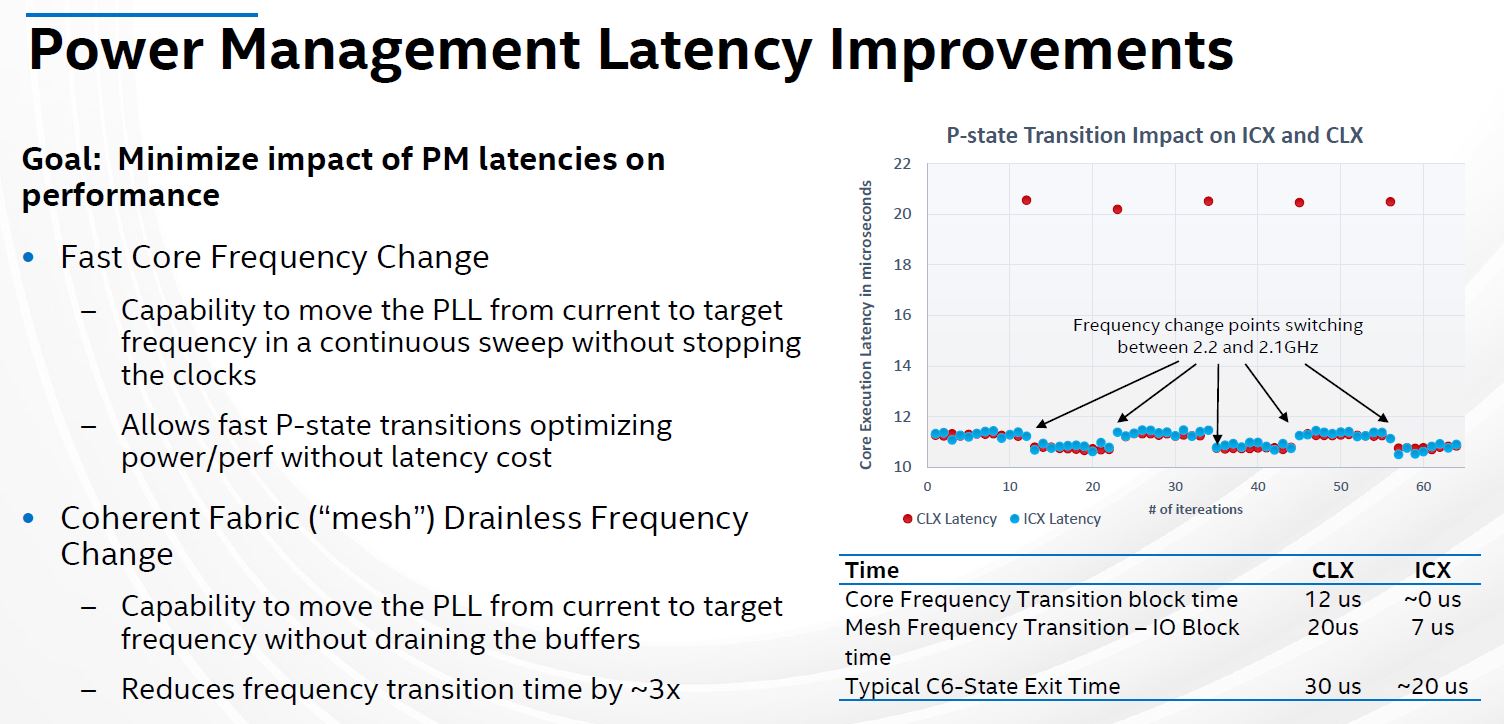

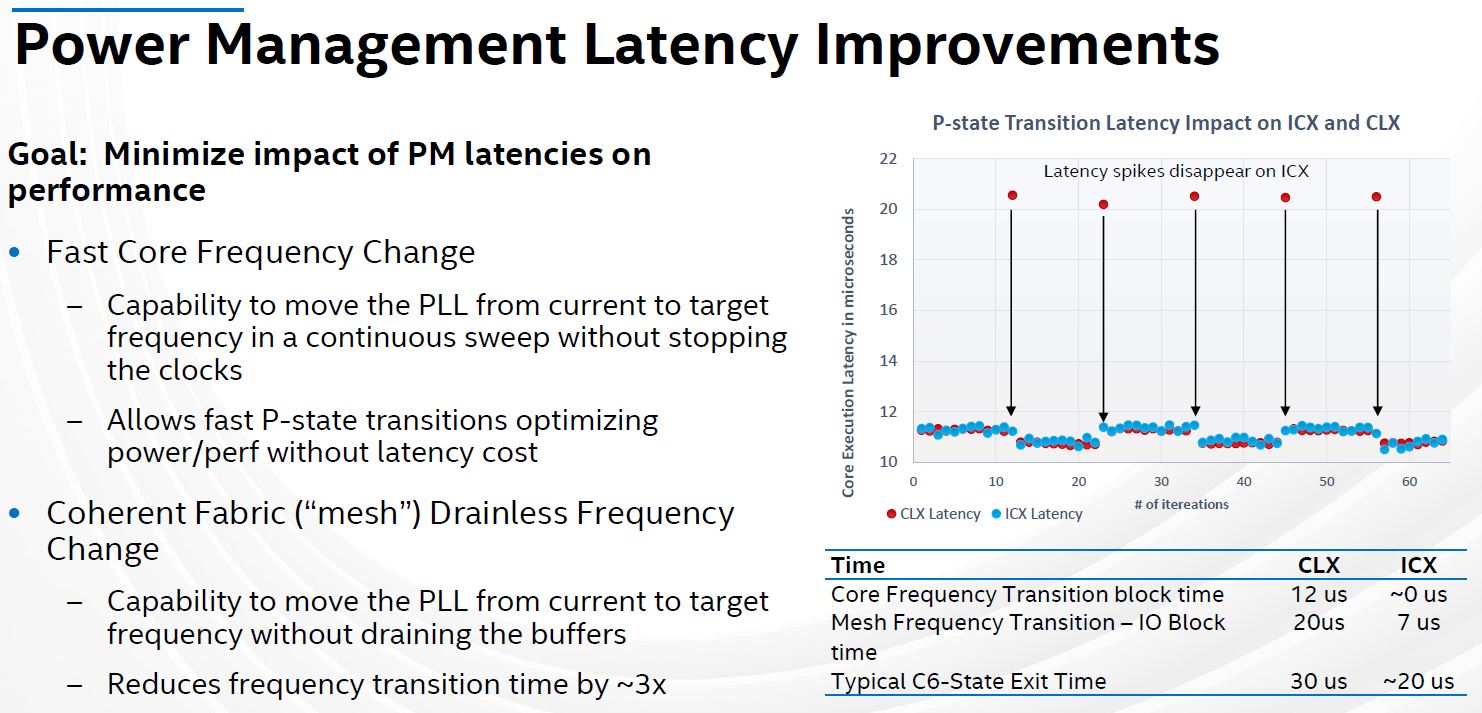

Intel is also changing how fast it can change frequencies. By pushing cores to lower P-states the chip can save power.

One of the biggest concerns is that bringing the cores back to ideal operating frequencies often takes several clock cycles which introduces notable latency. Intel says it is addressing that in this generation.

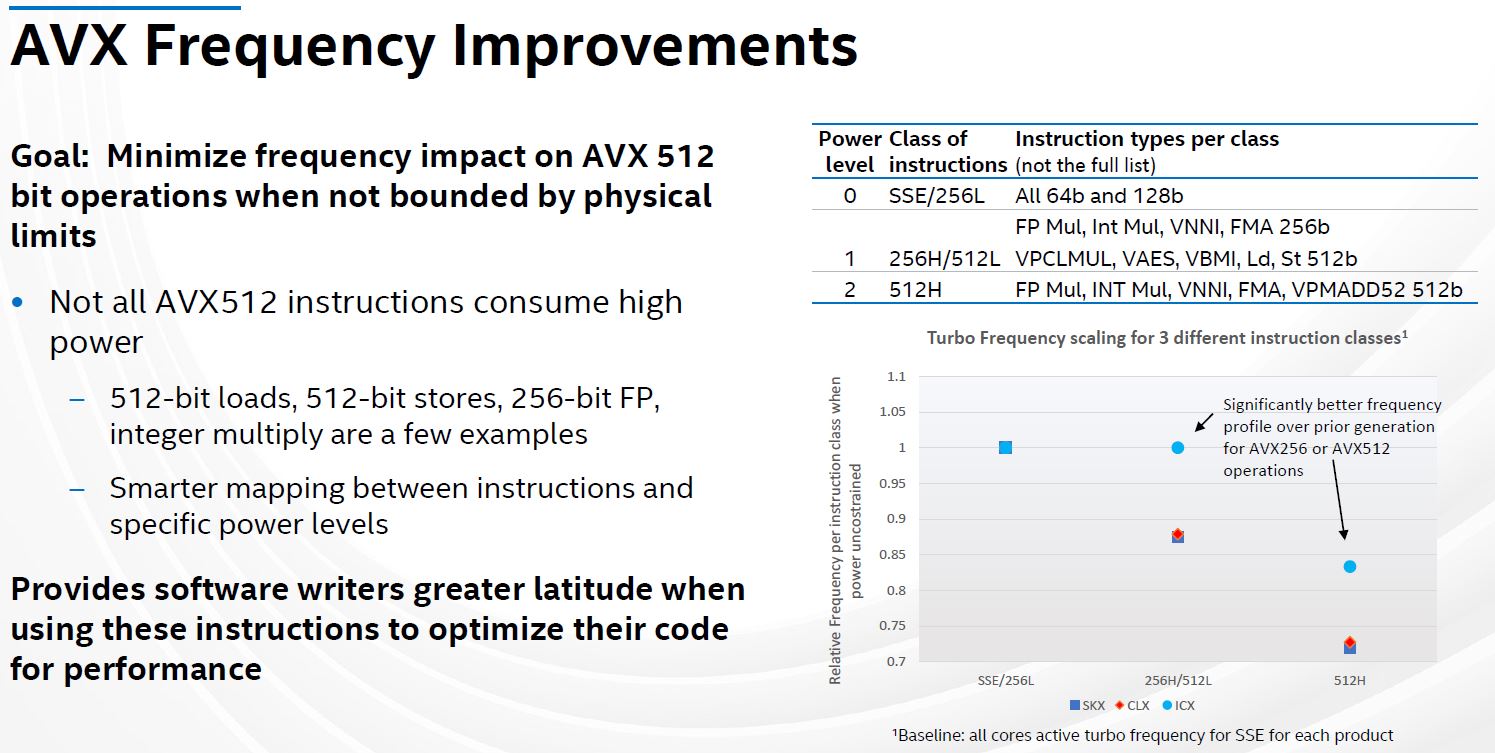

A fairly common case where that clock scaling latency came into play was switching from integer frequencies to AVX-512 frequencies. These cause massive changes in operating frequencies within a core and so there are cases where there would be noticeable latency switching workloads.

Overall, these are some tantalizing details, but Intel is still, for some reason, not going into full disclosure mode as we saw with IBM POWER10 even though that chip is further out.

Final Words

These are exciting times for sure. Intel needs to get these chips to market to push the industry to PCIe Gen4, but also to remain competitive given how the rest of the ecosystem is moving.

I don’t quite get this. 10nm+ is equal to 10nm SuperFin? So Ice Lake-SP is using 10nm SuperFin like Tiger Lake?

And why is Ice Lake-SP using Sunny Cove Cores when Tiger Lake is already using Willow Cove Cores? is this due to the continued delays Ice Lake-SP experienced and they adjusted the used fabrication node, but not the architecture itself?

Steve

Ice Lake SP has been planned for quite some time. The Cooper Lake (4 & 8S) and Ice Lake SP (1 & 2S) are transitional and will not be long lived.

Sapphire Rapids (2021)(10nm will likely be on the SF process) and is based on Willow Cove cores. One of the main features is there will be a unified platform from 1-8 sockets – rather than the split (Cooper Lake 4-8S and Ice Lake SP 1-2S) Sapphire Rapids also introduces DDR5 & PCIe5

Ice Lake SP will be important, and is a well balanced server, but ultimately short lived. If you don’t need DDR5 or PCIe5 – then Ice Lake SP will fit the bill and will se significant uptake.

Four NUMA Nodes or two (Hemipsphere Mode = some kind of RAS?)?

Too little, waaaay too late. AMD’s Milan and its new unified 8-core CCX’s are going to absolutely roflstomp this right into the ground (aka 1x CCX per chiplet instead of 2x, which should fix Zen’s performance in a lot of those super latency sensitive edge cases where Intel still dominates, and regular cross-CCX communication & cache hops reeeeeally messed with performance without doing lots of Zen specific code optimization).

What would really help with our planning would be for Intel to commit to a general availability time frame for the Ice Lake-SP Core based server CPUs and the Jacobsville Atom based micro-server SoCs.

I wish Intel and others would not use product names for IC’s that are by nature, disassociate at the subject matter level, such as Cooper Lake, Broadwell…, to AMD Naples, Rome…, thus not share any sense of physical design, a sort of stuck in the mud, image (form) over content (function).