Xilinx is launching a new solution for video transcoding. This includes a new Xilinx Alveo U30 PCIe card with hardened transcoding logic, its existing Alveo U50 PCIe product, software to make everything work without knowledge of FPGAs, and a partner ecosystem to deliver via on-prem and cloud-based channels. In short, Xilinx is getting out of just making the ASICs and low-level programming tools and is transforming into a solutions provider. In this case, Xilinx is targeting its solution at a timely and growing segment around live video transcoding.

Transcoding Challenge Background

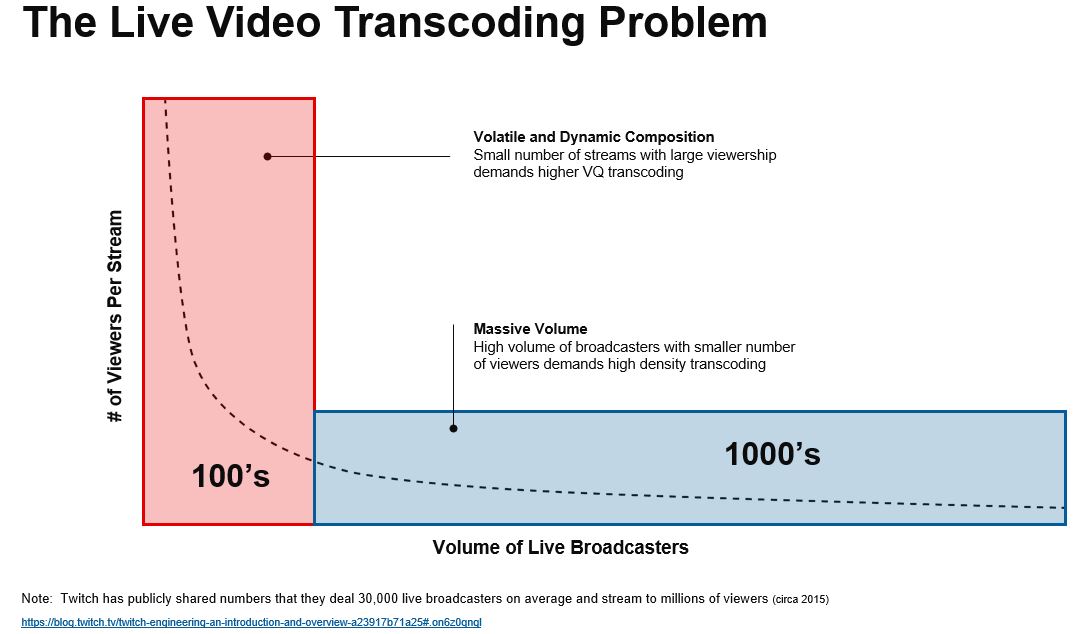

As many intuitively noticed, shelter-in-place orders in 2020 have caused a massive spike in video streaming. More content is being generated and being viewed more often by consumers on different devices. This is simply the nature of digitizing human interaction through video. Major video streaming services have found that the 80/20 rule applies to transcoding as well. 20% of the streams use 80% of the bandwidth and processing needs while there is a tail of 80% of the streams that are low-volume and require less bandwidth and processing power.

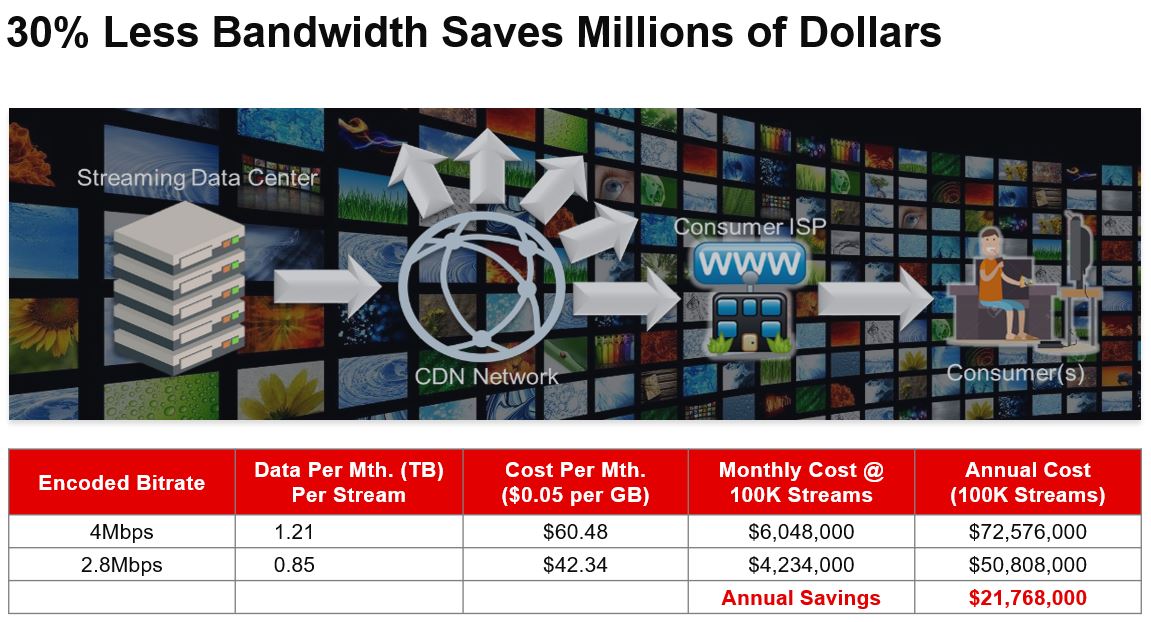

While Xilinx terms this as a “Tanscoding Problem” perhaps it is better labeled as a Transcoding OFG, or “opportunity for greatness” as the economic impacts can be substantial. Xilinx lays out an example scenario here:

Xilinx’s data per month per stream is effectively taking the bitrate and assuming it runs continuously for a month. Multiplying that by $0.05 per GB one gets a bandwidth cost. Assuming one can more effectively encode to a lower bitrate, that is where one gets savings from. Xilinx’s OFG here is in the direct savings which is a hard cost for streaming platform providers.

Xilinx Video Transcoding Solutions

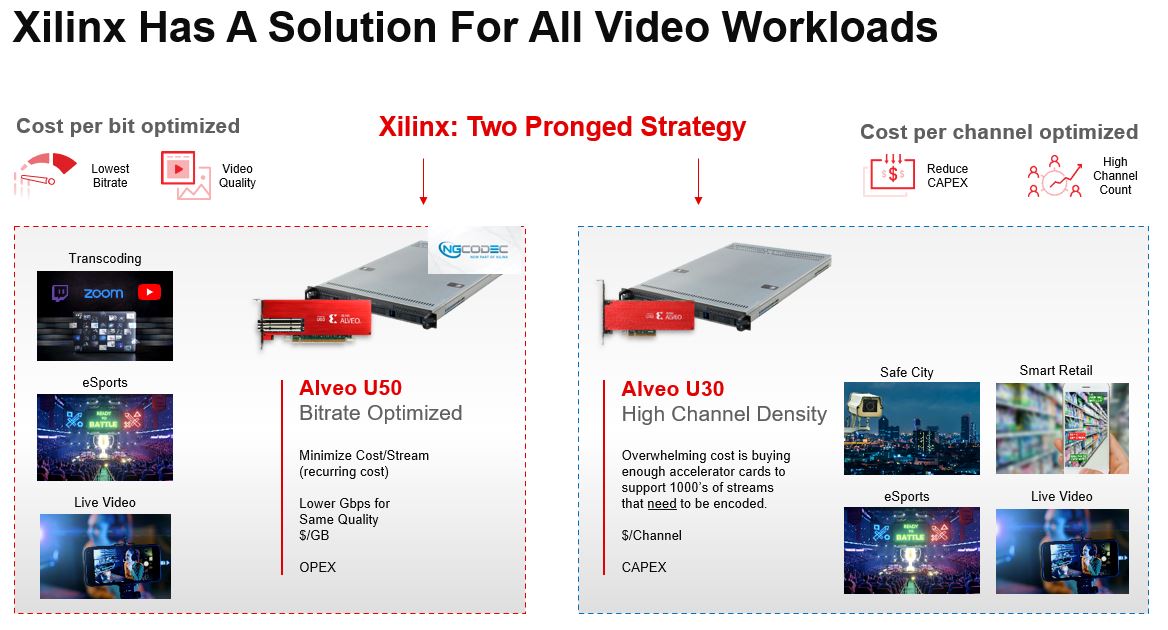

To address the Transcoding OFG, Xilinx is producing a solution that addresses both sides of the 80/20 rule challenge.

For the higher-capacity streams, it is using the more powerful Alveo U50. For the lower viewer streams that are higher in number, it has the new Alveo U30 at a lower cost.

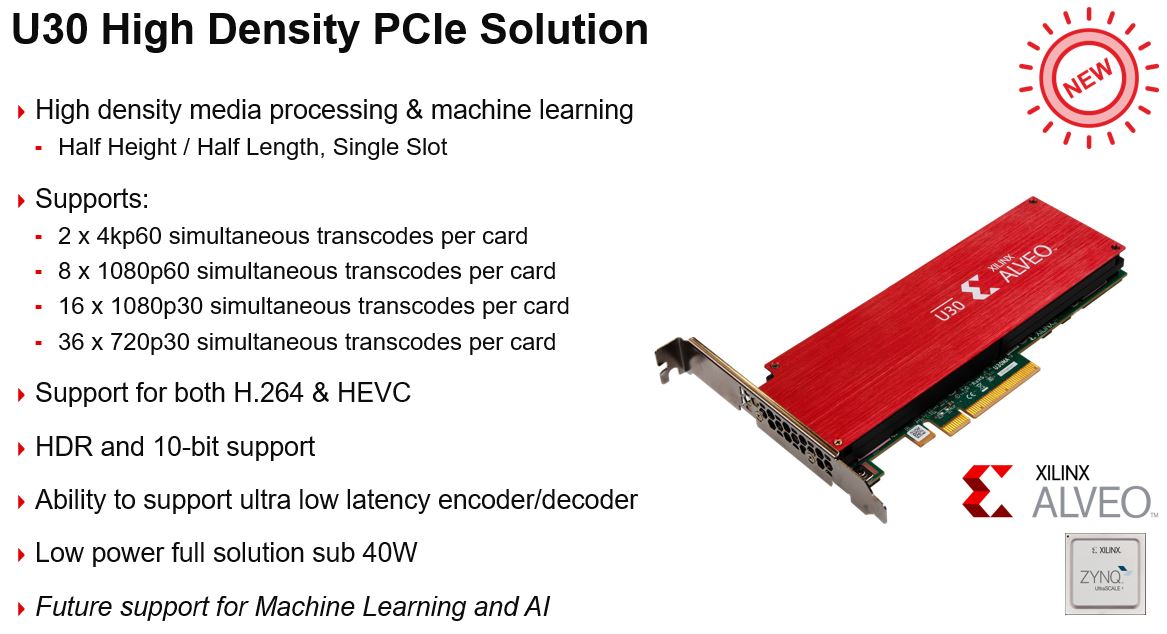

We already covered the Xilinx Alveo U50 FPGA Card for Data Center Acceleration but what is new is the Alveo U30 card for this space. The Alveo U30 is a low-profile PCIe card with hardened transcoding logic to accelerate a number of transcoding streams. This is still using the Zynq UltraScale+ architecture, not the newer Xilinx ACAP architecture. At the same time, it is a more mature part that has the hardware to compete in this space. Specifically, this is a sub-40W TDP, low profile, single-width card. That means it can be densely packed into most modern servers to drive up supported stream counts per server.

Xilinx making PCIe cards packing two Zynq UltraScale+ chips is a fairly big deal. The offering goes beyond that to offer a solution stack specifically tailored for the transcoding market.

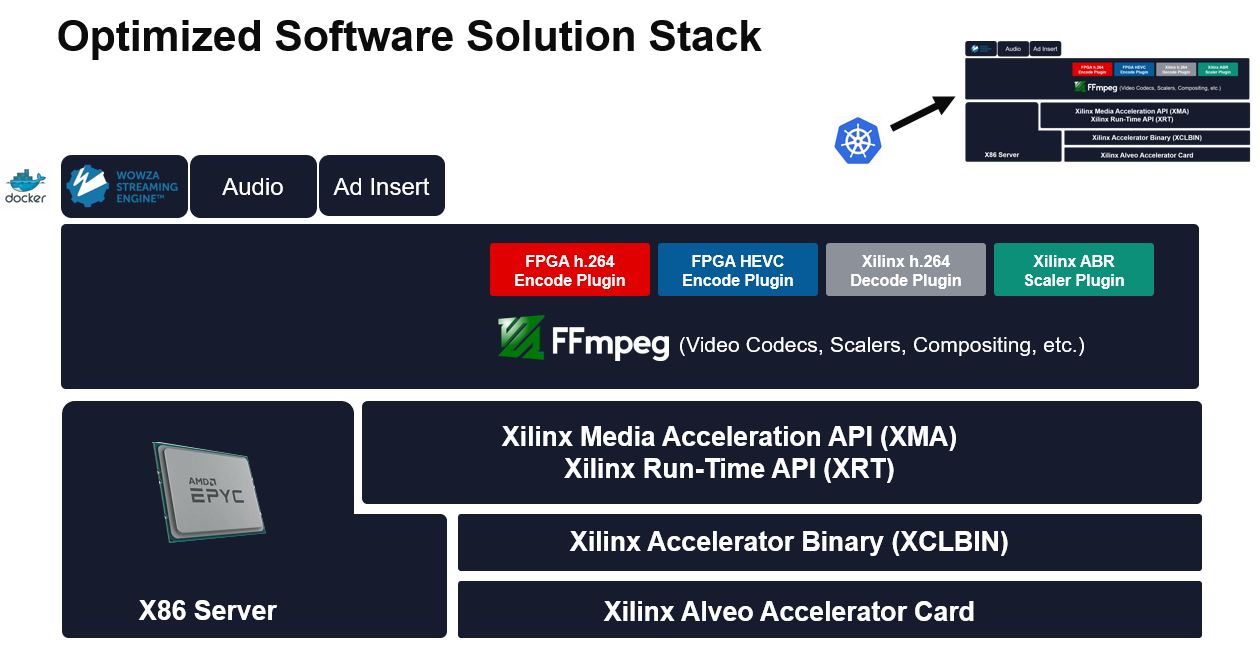

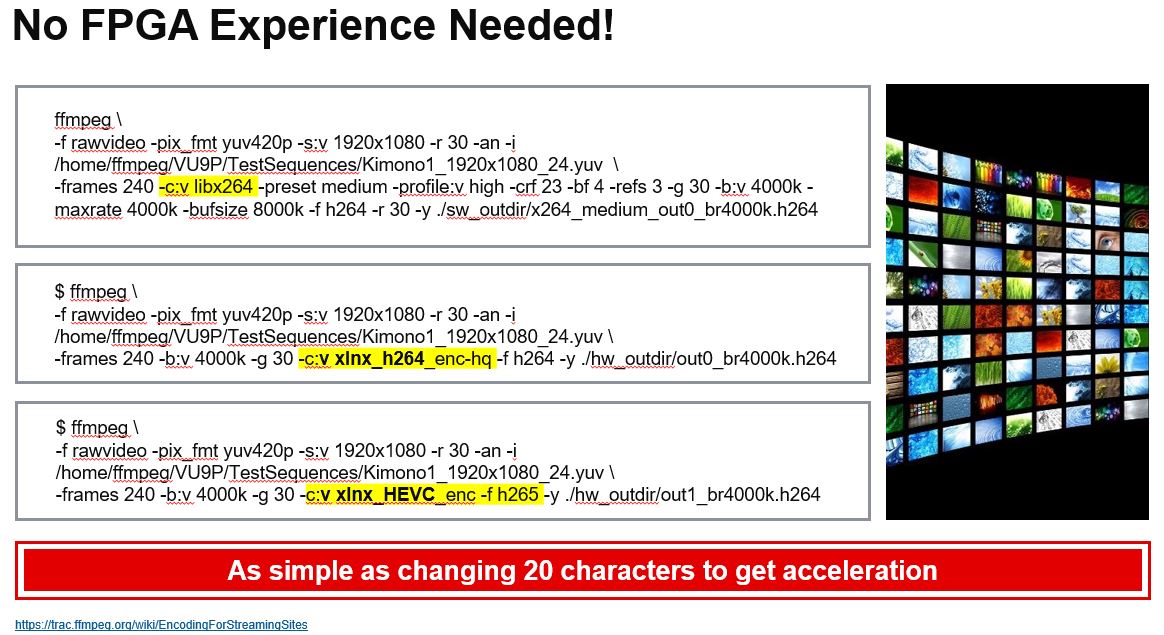

Key here is that the solution is designed to get organizations up and running with hardware transcoding without needing to program RTL. Instead, one can start transcoding using plugins that Xilinx provides.

Naturally, the concept is that beyond basic transcoding, the FPGA logic elements can be used to layer value-added services (such as ad insert noted two images above.)

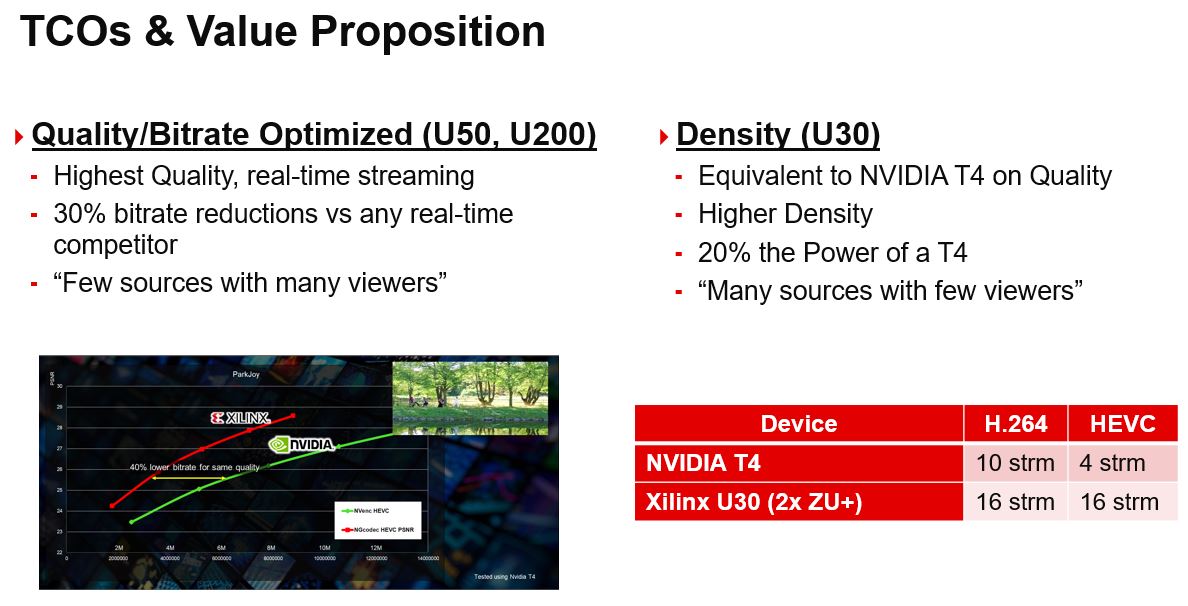

Xilinx has its solution compared to both Intel Xeon CPU transcode as well as NVIDIA T4 GPUs. We gave some feedback on the comparisons being drawn. For example, the Intel Xeon Platinum 8275CL is probably not the best server cost comparison point given the Big 2nd Gen Intel Xeon Scalable Refresh CPUs. We do not have the exact pricing for the Xilinx Alveo U30, but our sense is that it will need to be priced somewhere in the middle of a $1250-$1750 range to be successful.

To its credit, Xilinx has a number of go-to-market partners such as AMD, HPE, Wistron, and others to bring this offering out. While that may seem basic in the context of an NVIDIA GPU launch, or an Intel Xeon launch, it is a new and vital go-to-market strategy change for Xilinx which traditionally sold chips for others to integrate.

Final Words

I asked on the pre-briefing call with Xilinx the somewhat obvious question, why a FPGA versus just using a transcoding ASIC? Broadcom, for example, makes a transcoding ASIC for a hyper-scale customer that is not generally available. The answer I received back was refreshingly honest. There are ASICs being used, but the Xilinx solution is beyond just the transcoding. While there is an opportunity to use the standard PCIe cards, with the Xilinx FPGAs and hardened transcoding logic today, using FPGAs allows these providers to add additional services later. For example, instead of simply transcoding, doing analytics, or even adding additional data to the stream (e.g. adding overlays.) In essence, the solution is built to offer better than NVIDIA T4 acceleration today, then add more functionality post-deployment. That is a similar value proposition to how NVIDIA positions the T4, yet Xilinx is bringing more hardened codec logic and FPGA flexibility.

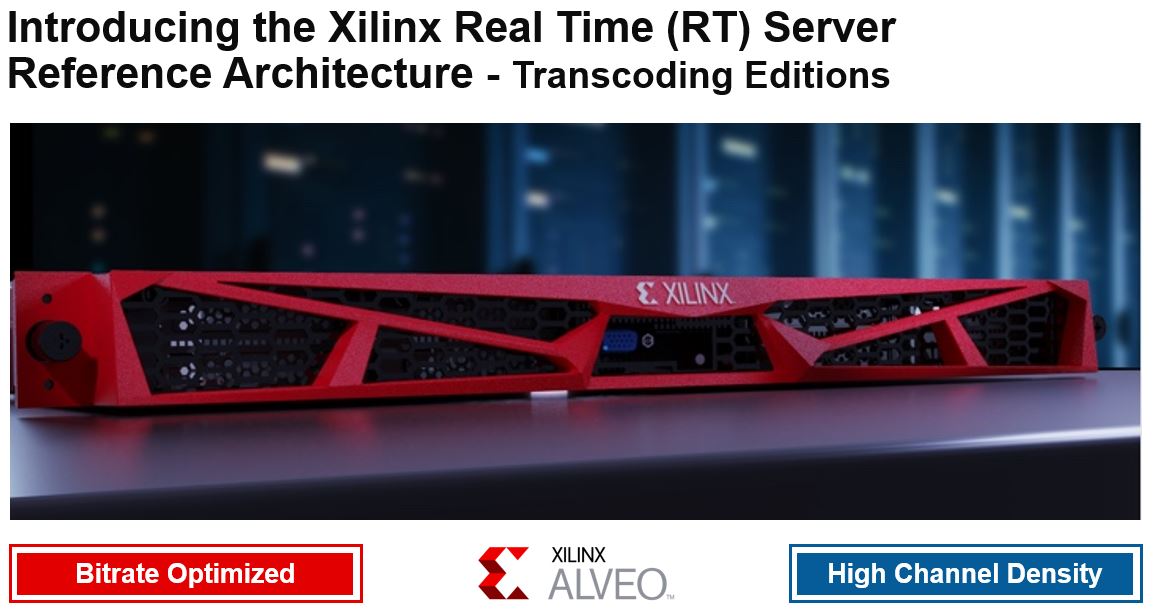

On a lighter aside, how about that Xilinx-Wistron server faceplate? The image Xilinx gave us was too small to be a STH cover image. After doing my morning read-through of this piece before it went live, I thought that it needed to be the cover image. So I got a little “artsy” and we now have a bigger image. Maybe not the best, but it is what it is. Custom faceplate, meet custom STH cover image.

They claim 30-40% bitrate reduction at the same quality, where quality is measured by PSNR. The only issue is that PSNR is an absolutely shitty metric that has only the loosest relationship to subjective video quality.

State of the art psychovisual optimizations found in the best software encoders, like x264 are well known to make PSNR and SSIM worse, while greatly improving perceived video quality.

I am disappointed that Xilinx is trying to get away with that BS. And I think you should have called them out on trying to slide that by.