Over the weekend, Charlie at SemiAccurate caused a bit of a buzz with his story that Intel was cutting a major server platform. Since SA is a subscription service, we typically will not scoop their articles but Intel reached out to us proactively, and I spoke to Charlie yesterday before getting this online. The big news is that the “Cooper Lake” generation of Xeon processors is being canceled in the next-generation mainstream Whitley server platform. Let us dissect what that means, and why it is important.

Next-gen Intel Xeon Cooper Lake Changes

Intel has already disclosed a lot on its next-generation platform. First at the 2018 Intel Data-Centric Innovation Summit. Just before the AMD EPYC 7002 series “Rome” launch, Intel disclosed a 2020 Cooper Lake socketed CPU with 56 cores and bfloat16 support. Even before that at the Intel OCP Summit 2019 Keynote it showed off its 2019 Cooper Lake Xeon lineup.

I was sitting in front of the speakers instead of the projector, so I apologize for the angle. What you will see is a 2-socket Whitley platform that will be shared with the next-generation Intel Ice Lake Xeons. This will be the platform that will bring 8-channel DDR4 to the Intel Xeon world as you can count by the DIMM slots shown on the OCP-Intel-Microsoft-Facebook branded slide. This is actually the platform most relevant to the new disclosure.

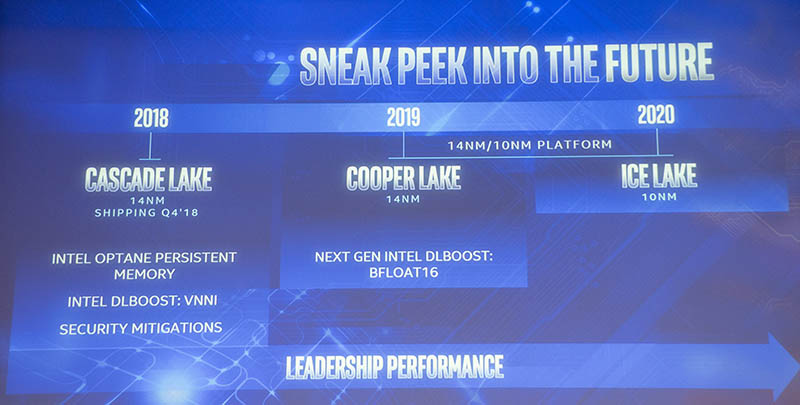

Here is an Intel Roadmap from the Q3 2018 Intel Datacentric Innovation Summit. As you can see, the 14nm Cooper Lake and 10nm Ice Lake platform was expected to be a combined platform that we now know as “Whitley.”

On the right side of the OCP Summit 2019 picture two images above, you will see 4-socket and 8-socket platforms. These will be the Cedar Island platform that is set to launch in the first half of 2020. Specifically, with bfloat16 support (important for AI training for example) and this multi-socket flexibility, we know that this is a part that Facebook and others are very interested in. We would have expected to hear more about this platform at the OCP 2020 Summit had that event happened as planned earlier this month.

Summing that up, we were set to see Cooper Lake CPUs in Cedar Island for 4-socket and 8-socket configurations. We were then expecting to see another Cooper Lake variant effectively launch the next-generation Whitley platform that will eventually replace the Purley/ LGA3647 platform. Purley supports first and second-generation Intel Xeon Scalable processors. That Whitley platform will then be re-used for the Ice Lake Xeon generation that brings 10nm and features such as PCIe Gen4.

That was the state before last week. Now to the new disclosures.

Intel Statements on Cooper Lake Xeon Status

We received an official communication over the weekend on the status of Cooper Lake Xeons from an official Intel spokesperson. Here are the points that we received from Intel:

- Intel constantly evaluates our product roadmaps to ensure we are positioned to deliver the best silicon portfolio for data center platforms.

- Given the continued success of our recent expansion of 2nd Gen Xeon Scalable products, in addition to customer demand for our upcoming 10nm Ice Lake processors, we have decided to narrow the delivery of our Cooper Lake products that best meets our market demand.

- Intel’s upcoming Cooper Lake processors will be supported on the Cedar Island platform, which supports standard and custom configurations that scale up to 8 sockets.

- We continue to expect delivery of Cooper Lake starting in the first half of 2020.

- Customers, including some of the largest AI innovators today, are uniquely interested in Cooper Lake’s enhanced DL Boost technology including the industry’s first inclusion of bfloat16 instruction processing support. We expect strong demand for the technology and processing capability with certain customer segments and AI usages in the marketplace that support deep learning for training and inference use cases.

- Intel’s upcoming 10nm Ice Lake processors will be introduced on the upcoming Whitley platform.

- Intel remains on track for delivery of 10nm Ice Lake CPUs later this year.

(Source: Intel)

That is a lot. Let us discuss what that means.

Impact of Cooper Lake Status Change

What is effectively happening is that Cooper Lake on the Cedar Island platform for 4-socket and 8-socket servers will still be released next quarter. Our sense at STH is that this will be later rather than earlier in the quarter but these things may change given the state of the economy and world events. Still, Intel will launch this since it has large customers (e.g. Facebook) who want this part.

We first heard that Cooper Lake on Whitley was in jeopardy in October 2019. A few vendors started mentioning that engineering sample chips were coming in late. I asked the obvious question, “if Cooper pushes to within a quarter or two of Ice, what happens?” The answer was generally that vendors may drop Cooper support in Whitley to lower the cost of their platforms. As a note, we hear a lot at STH, but we do not post every rumor around which is why this is the first many of our readers will hear of this. Still, it makes sense given the context. If whatever events, health, economic, or simply product readiness have pushed Cooper too close to Ice, then it probably makes sense to streamline the portfolio.

In the market, that will have some impacts. We know that bfloat16 is a huge feature along with increased core counts that have many organizations excited for Cooper Lake. For larger platforms, Intel will have chips with new features and core counts designed to be competitive for out-scaling AMD EPYC 7002 systems. Assuming the current direction holds, by this summer we will see 4-socket Intel Xeon “Cooper Lake” generation parts have more cores than AMD’s “Rome” generation in a system. Even if they have lower core counts per CPU, Intel will have competitive features such as their new instructions. We do not see these as becoming the mainstream Xeon alternative which we discussed recently in Why All Servers Are Not 4-Socket Servers.

On the 2-socket mainstream Xeon side, this is a big change. Intel is now in-market with their big 2nd Gen Intel Xeon Scalable Refresh parts. These “R” SKUs are specifically for one and 2-socket systems. Effectively this was Intel releasing a line that will carry through 2020 until Ice Lake Xeons launch later this year. Depending on when AMD launches Milan, that means that Cascade Lake Refresh SKUs may be the mainstream Xeon parts when Milan launches. Ice Lake Xeons promise a host of new features that we are excited about, but without Cooper Lake, that is all we will have.

There is another impact. For the server OEM/ ODM community, that means their next major mainstream Intel product launch is later in 2020. Those same platforms that were launched alongside the Intel Xeon Scalable Processor Family (Skylake-SP) will be still top-of-the-line more than three years later. Platform refreshes are important in the industry since they help vendors initiate sales conversations with customers as well as bring new technologies. For example, we would have significantly more PCIe Gen4 NVMe SSDs in-market at this point if Ice Lake was already out. The other side of this is that by rationalizing the release schedule, partners will not have to do two launches of the same platform in 2020. If Cooper Lake hit in late 2019 as that OCP Summit 2019 Intel Keynote slide said, then that is a different story. As the timeline compressed, this makes sense which is what we heard from OEMs last year.

Final Words

Overall, this is a big deal. Intel has rationalized a platform as SemiAccurate originally scooped and Intel confirmed to STH yesterday. The impact of these changes will trickle through the ecosystem over the next year.

We should also be mindful that there is a lot of global economic uncertainty at the moment. Perhaps it is wise to focus energies on one launch later in the year rather than launching a shorter-term product.

For those saying Cooper Lake is “dead”, Intel confirmed that it is still on track for the first half of the year. We pressed for a date, but as one can imagine, scheduling is fluid with major events being postponed or canceled. What we can say is that we will keep STH readers up-to-date with Cooper Lake when it does launch on the Cedar Island platform.

This is unreal. They’ve cancelled the launch only a few months away at most? What about all the OEMs? Surely they’ve all made systems that were waiting.

I don’t think that the OEMs were giddy about Cooper Lake. With Milan and Ice not that far away, you’re looking at pretty much HPC only, and they could go for the 9200 series if they really want that 56 cores (yes I know bfloat16, but my point is that they are the people going for 9200 now) and look at the market interest for that. Cooper (especially Cooper below 250W) would’ve been dead on arrival anyway.

Isn’t Cooper in Cedar Isle supposed to be the platinum 9200 replacement?

Eh @Steffen I don’t know if that’s completely true. With Ice Lake supposedly only going up to 38 cores per socket, Intel is going to really but at a huge deficit in the regular mass market 2S server space. The idea of 56 core Cooper Lake in a regular socket was seemingly designed to combat that, but with it dead Intel has nothing to compete with Rome/Milan.

Rome/Genoa and direct Epyc CPU to Radeon GPU/Accelerator Infinity Fabric interfacing and who knows what AMD would do about any 4P products if some client with deep pockets requests that capability. On TSMC’s 5nm and just how many CCDs would fit in and around the I/O die on that MCM, And what about the I/O die getting a shrink as well if needed and Intel’s must be more terrified of AMD’s Zen/Generational update cadence that’s really impressive and maybe more than 64 cores across more than 8 CCDs is possible at 5nm to make things Intel/4P not so attractive once again. And AMD’s Infinity Fabric is just that scalable and 4P and more CCDs per MCM are not too difficult a task via some semi-custom contract where the client may be covering some/all of the R&D/engineering costs. But I’m in favor of Epyc 96 core options at 5nm being possible and offered to any of Intel’s 4P diehard customers.

Intel will have little help in the next few years minimum it will take for Intel to right its foundry ship and TSMC/AMD are not a static target what with AMD’s/TSMC’s respective CPU Micro-architectural and Fab node update cadence showing no signs of slowing down. If Intel tries and hurry it’s 7nm node and try to produce the same density as TSMC’s 5nm Intel may risk it’s 10nm issues all over again and really Intel’s 10nm is not really considered a success by anyone, including Intel! But AMD/TMSC are the moving target that’s out ahead and getting further out with no signs of slowing down. Intel had issues with 14nm(1) as well before that 14nm became the basis of Intel’s post tic-tock fall back and the pluses king. So really Intel painted itself into a far corner this time around with that coming while TSMC/Others where ahead or at parity with Intel’s 14nm.

(1)

“Intel pushes back production of new ‘Broadwell’ chips

By Damon Poeter October 17, 2013”

https://www.itproportal.com/2013/10/17/intel-pushes-back-production-of-new-broadwell-chips/

It’s a lot more important that Intel explicitly disclose which new generation chips don’t and which ones do still use partial addresses!

@A Person

What do you mean nothing? 4 or 8 CPUs multiple by 56 cores i definetly more then 2 CPUs multiple 64 cores. It looks like that whitney platform is for ice lake mainly and vendors dont want to support copper lake there. Maybe it will be like that. 4/8S copper like, 1/2S ice lake.

@mjwhite : I think your conclusion is what Intel wants to communicate going forward:

1/2S = Ice Lake and 4/8S = Cooper Lake

For ost of us that are more interested in1/2S, Cooper lake is basically dead and would anyways be overshadowed by Ice Lake which is THE chip that Intel will be competing with against Amd.

Exciting new few years for sure and I really hope Amd continues to keep Intel on their toes going forward!!

Intel needs to sponsor F1 auto racing, where car upgrades and even whole launches are constantly being updated in this manner.

There’s nothing at all unusual about what Intel is doing, which is only what any competitive engineering specialist does normally.

This signifies that we have real competition in both camps for whatever reason nobody’s slacking or resting on their laurels. Moreover this rearranging indicates to me intelligent reallocation of resources and that isn’t done late in the day unless you are getting gains from doing so or truly awful waste or non improving development in the cancelled order downplayed roadmap points.