This week in San Jose, California I had the opportunity to join the 2019 RISC-V Summit. I wanted to do a short piece giving some thoughts on the summit itself while also covering a few of the big announcements from Western Digital, Microchip, and SiFive.

RISC-V Summit Growth

I attended the 2018 Summit at the Santa Clara Convention Center. The 2019 Summit was moved to the San Jose Convention Center which is a larger space. For some context, it is the same building that houses NVIDIA GTC, Arm TechCon, and OCP Summit among others.

It may have partly been due to the new venue, but this year’s RISC-V Summit felt bigger. The exhibitors seemed to have a bigger presence and there were more people involved. Even in the bigger space, it felt more crowded. Attendance was up by over 27% year/ year from around 1100 attendees to around 1400.

With the RISC-V ecosystem still developing, it is important to see the show becoming larger. It is still a far way from the size of an Arm TechCon, but growth is good. This is something many of the press releases focused on products will miss, but we wanted to show anyway.

Western Digital Highlights at RISC-V Summit 2019

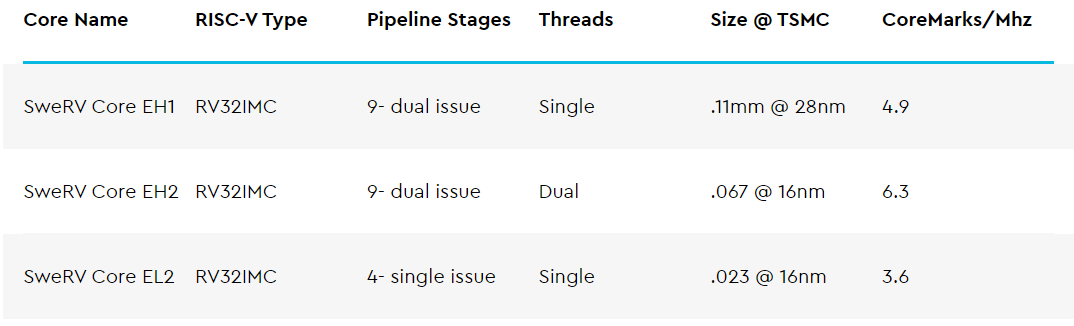

At the RISC-V Summit 2019, Western Digital announced two new RISC-V cores the SweRV Core EH2 and SweRV Core EL2. It is fairly easy to see where the company is going with this. Coming from a volume manufacturing background, building its own cores gives some per-unit savings that then turn into margin dollars.

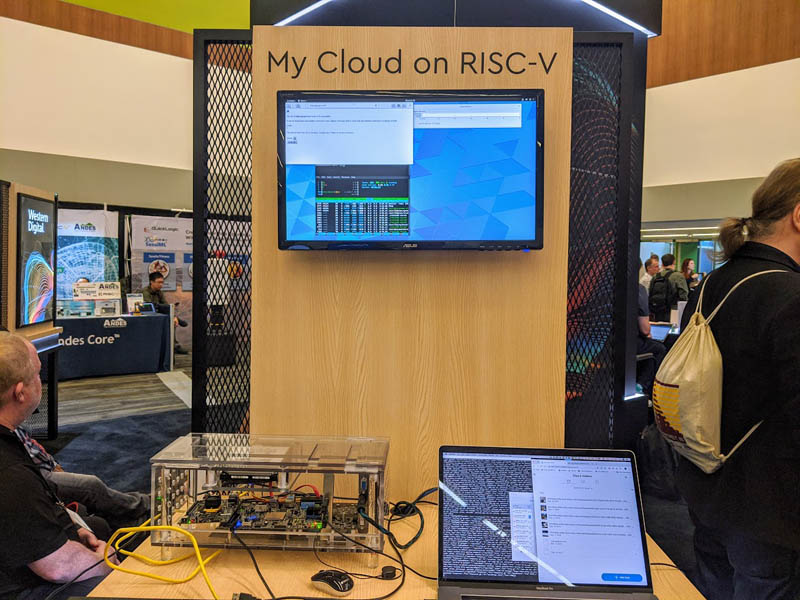

There was certainly some of this. A great example is an update to the WD MyCloud shown last year. At the 2019 Summit, this demo now had mobile app access via a smartphone.

WD went beyond simply showing new cores and consumer demos. The company showed off its OmniXtend cache coherent memory fabric running atop some big FPGA boards.

The company also showed off RISC-V hypervisors. There was a lot of talk at the show about different RISC-V technologies moving from proof of concept to ready to deploy. This is one that still seemed like it needed a bit more time to mature.

The key takeaway here is that WD is pushing RISC-V well beyond simple low-end network devices and has technology projects to extend the reach of RISC-V.

Microchip Highlights at RISC-V Summit 2019

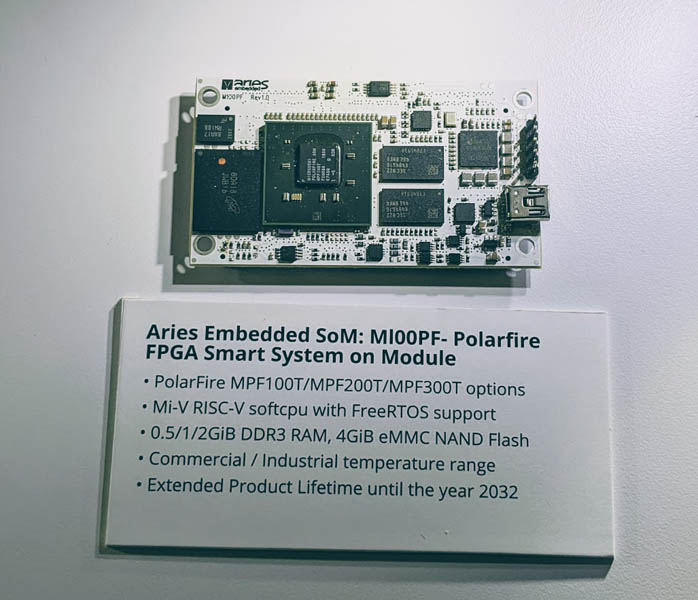

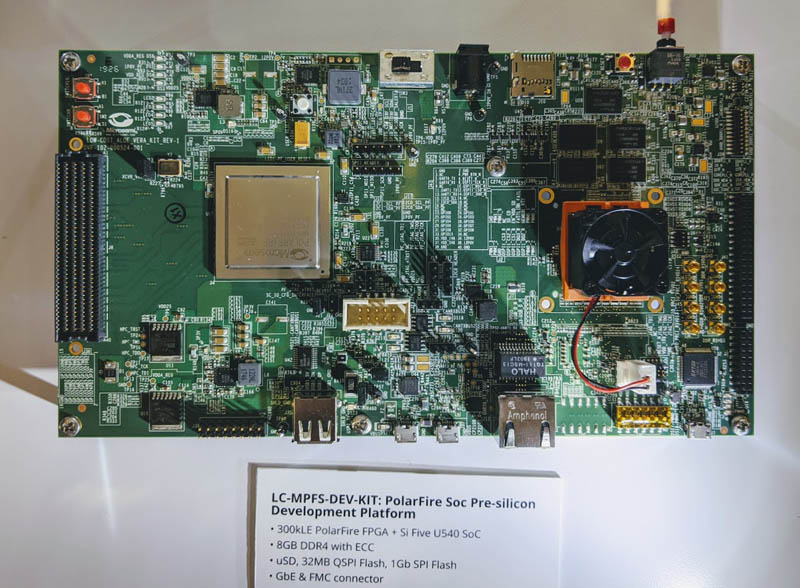

Microchip was all over the summit. The company is pushing its PolarFire FPGAs as solutions to the RISC-V developer community. There was an entire display case full of boards, we wanted to show two.

The first is a Aries Embedded SoM called the MI100PF that integrates a FPGA-based system on a module. This particular module also incorporates DRAM and eMMC and sports an extended product lifecycle. On the FPGA is a Mi-V RISC-V softcpu. This is a good looking option for those that are developing based on RISC-V but cannot use the larger boards.

Another intresting example was a pre-silicon development platform called the Microchip LC-MPFS-DEV-KIT. This is a much higher-end part that incorporates a larger PolarFire FPGA plus a SiFive U540 SoC, more memory, and more I/O.

Microchip products were all over the show floor in different booths. The company is doing a great job going after the developing RISC-V market.

SiFive at RISC-V Summit 2019

The other company that was seemingly everywhere is SiFive. SiFive is the leader in the ecosystem. It has chips that are incorporated in other products such as the Microchip board above. In the photo below, the gentleman in the booth was using a demo of a small SiFive/ RISC-V sensor board that connected directly to AWS and was being used to control cloud game input based on gestures.

SiFive was all over the conference between sessions, in their own booth, with big-name partnerships, and in many of the booths at the show. It is clear that SiFive’s first-mover advantage is translating into it being the current go-to company for collaboration on new solutions.

The company announced its new Apex series of processors along with the RISC-V vector extension called RVV.

Final Words

Seeing continued growth and investment in RISC-V is a good sign for the industry. RISC-V is not something we expect to replace Intel Xeon in 2020. At the same time, all of those Intel Xeon servers have BMCs like the Aspeed AST2600 that are vulnerable to an Arm to RISC-V switch in the near future as vendors look to provide increasingly secure and differentiated management platforms.

2019 was a year of growth for RISC-V, but there is still a lot of work to be done until it is seen as an Arm or x86 competitor. I wanted to show off the show floor and attendance numbers to show that that work and growth is happening.

Are there any similar summit for POWER?

Ed, are you thinking of the OpenPOWER Summit?

I like MIcrochip, but its PolarFire has yet to prove its cost-effectiveness against the likes of Lattice’s ECP5.

Lattice sels 12K LUT chips for friggin $6 per chip. Radiation hardening is nice, but how many folks need their design to run inside unclear core ?

Had PolarFire had CPU core as hard macro, that’d be another matter, but so far ECP5 stays champion for me…

It will be nice to see their successor on 28nm process and Nexus platform during 2020….