There is an absolute ton of innovation happening at Intel in the data center space. 2017 is going to be an exciting year. As part of our Trends in Server Compute 2017 series, we are going to discuss some of Intel’s new server chips that we will see in 2017. We are going to honor Intel embargos where they exist and only use information already discussed on STH. Even with that said, over the next few quarters we are about to witness Intel use multiple architectures to target silicon for every server compute market.

Low-end Due for a Refresh

When the thread of AppliedMicro X-Gene and Calexeda (now defunct) pushed Intel in Q3 2013 we got the Avoton and Rangeley CPU lines. These low power SoC’s were good enough that the low-end ARM competition largely disappeared for over three years. We saw the Intel Xeon D lineup launch with Broadwell-DE in Q1 2015 and expand in 2016 which also pushed designs like the AMD Opterion A1100 “Seattle” SoC out of the market.

We are expecting Denverton to hit in 2017. The Avoton and Rangeley lines are still on a 22nm process while consumer Atom parts have seen generations at 14nm. It is clearly time for a new low power system. On the flip side here is that Denverton has been delayed, repeatedly.

There are a few key points to Denverton. First, we expect it to have much lower IPC than Broadwell-DE as it will use lower end cores and caching. While Broadwell-DE still has decent compute capabilities even for low end virtualization, Denverton will be focused on embedded systems and I/O. We expect 10GbE to be available as well as flexible I/O that we have mentioned in the past as coming with Skylake-EP. This will be the ability for the motherboard maker to choose whether to use SoC I/O as either PCIe or SATA. We expect SATA III to be supported, but not SAS. We also expect the number of SATA ports in most platforms to exceed 6 as even the Intel Xeon E3 range has moved to 8 SATA III ports.

If/ when Denverton is (ever) released, we expect this to be a hot-topic for storage and networking appliances. We have seen platforms but have been asked by Intel not to publish them before their eventual release date and are honoring that request.

Skylake-EP: What we have been waiting 5 years for

Since 2012’s Sandy Bridge-EP release, we have seen a cookie cutter template for mainstream dual-socket platforms. There are two 2011 pin sockets (LGA 2011 and 2011-3) along with quad channel memory with up to three DIMMs per socket and 80 PCIe lanes from the CPUs. Sure we have seen upgrades in areas such as the onboard PCH’s SATA controller but the fact remains, these systems have been extremely consistent for years.

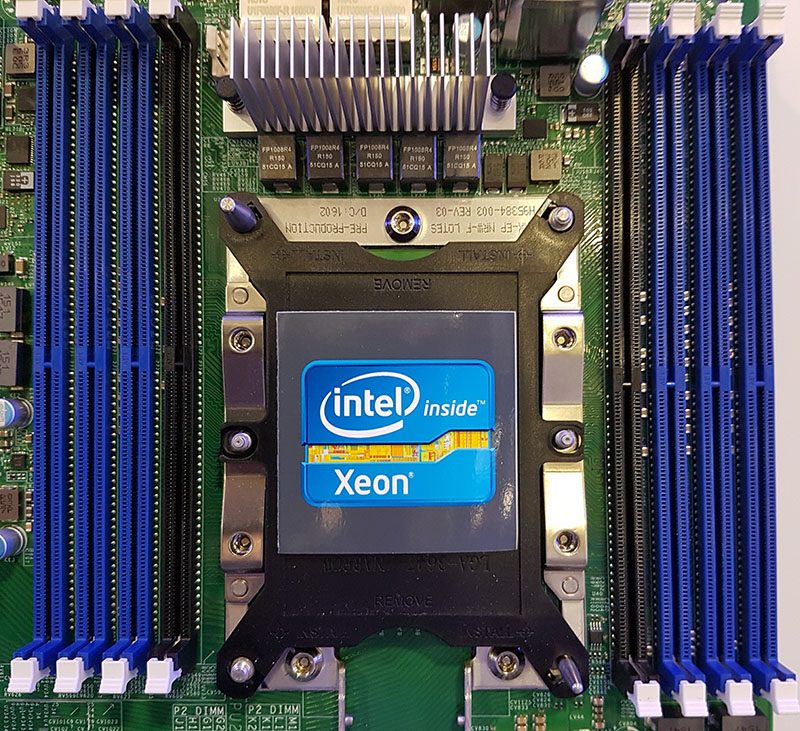

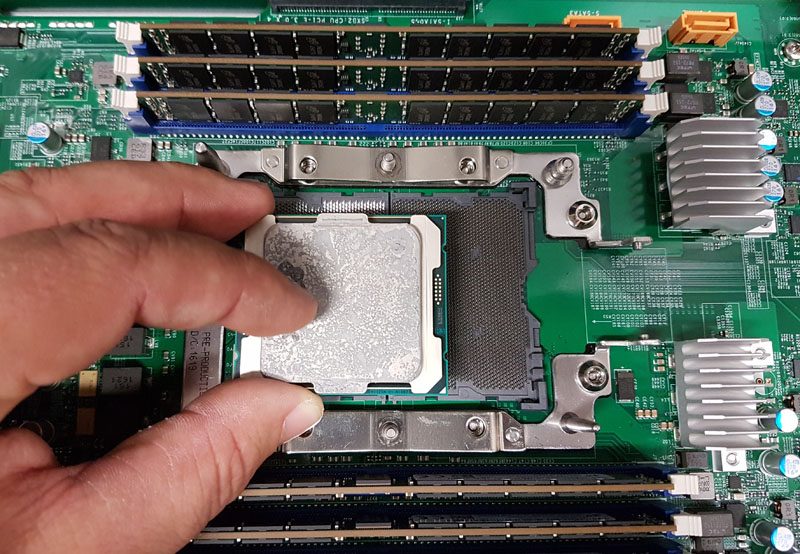

The fact that Intel has had such a consistent platform has had a large impact on the adoption of new technologies. For example, when we asked why 2.5″ NVMe adoption has been so slow, one of the most common answers we hear “system vendors are releasing few new designs until Purley.” Purley is Skylake-EP’s platform. The fact is that we are seeing some major design changes with Purley/ Skylake-EP. For those wondering, the LGA3647 chip pictured here is a Skylake-EP part.

Large customers are already getting access to Skylake-EP and Optane drives. We expect that by the mid-2017 official “launch” of Skylake-EP large system vendors will have some awesome designs. We know that these systems will have Apache Creek (Optane in DIMM form factor) support. We know that we will see the larger LGA 3647 socket similar to Knights Landing. We also know that we will have a 6-channel memory controller and that I/O is going to get a re-vamp.

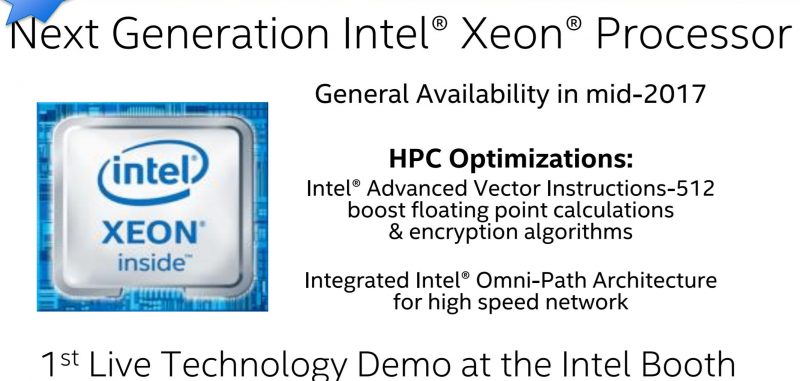

The other exciting side is networking. Omni-Path will be an on-package option. If pricing is similar to Omni-Path on Knights Landing, we will see 100Gbps networking on CPU packages added for under $300/ CPU. To give a sense of why this is exciting, today’s Mellanox EDR Infiniband cards cost upwards of $1200/ each. Beyond this, we expect Purley to include both 10GbE as well as flexible I/O as we mentioned with Denverton.

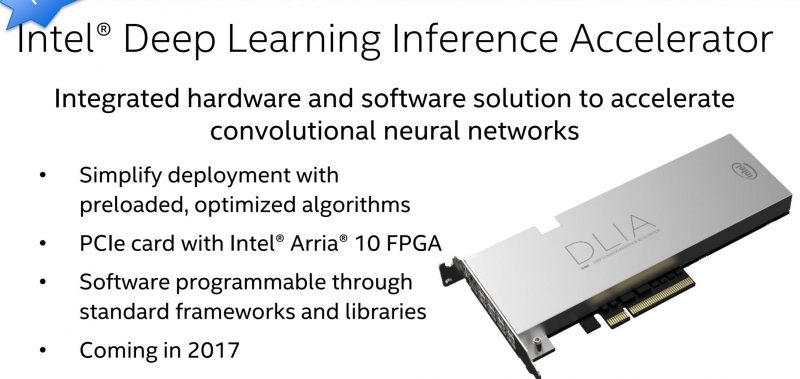

With the larger LGA 3647 socket, we also expect to see co-processors go on-package. We already reported on Broadwell-EP with Altera FPGAs. We expect to see more of this integration with larger core-count x86 processors along with FPGAs. Intel will be adding AVX512 instructions with their Skylake-EP chips so mainstream Intel CPUs will get the specialized compute instructions we can only get with Knights Landing today.

The other expectation we have is that we will see 200W and eventually 300W+ CPUs on the LGA3647 platform. There is a reason there were so many water cooling demonstrations at SC16 this year.

Divergence

One other area we expect to see a major divergence on is with desktop platforms. The LGA 3647 socket is too large and in desktop markets using a minimum of 6 DIMMs to get full bandwidth is simply cost prohibitive. While enthusiasts today enjoy being able to use LGA2011 and LGA2011-3 platforms, with Purley and Skylake-EP this will change. We expect a bridge socket, much like the LGA1356 socket we saw with Sandy Bridge-EN which may fill the space vacated by single/ dual socket LGA2011-3.

We will likely continue to see the Intel Xeon E3 line live on including eventual Kaby Lake updates. At the same time, the focus is not going to be on the E3 line as Intel has better server options. An end user may not do much more than they did a few years ago, but when you can virtualize servers, getting larger resource pools can be important. We are particularly excited about Intel’s Iris Pro graphics for virtual desktops due to Intel’s low cost/ free licensing. We do have Intel Xeon E3-1500 V5 series platforms in the lab so more will be forthcoming on this subject.

On the topic of divergence, we are also moving away from a quite homogeneous Intel x86 server compute world. There are going to be major differences in packages with Skylake-EP and major differences in families with the new generations of chips coming forth. It has been many years since we will have had so many options in the server space.

Knights Mill

Since we have been working with Knights Landing, the next iteration in 2017 will be Knights Mill. Again, expect 300W+ monsters when these chips arrive hopefully in mid-2017. Intel is keenly aware that a major HPC area is machine learning so we expect Knights Mill to do better than current Knights Landing.

Some of the form factors we have seen for HPC nodes that will go live around Knights Mill generations are absolutely awesome. Suffice to say these will be bigger, badder, many core chips and with even higher power thresholds. Watercooling will become more commonplace as air cooling dense arrays of Knights Mill will be challenging.

FPGAs and Nervana for AI/ Machine Learning

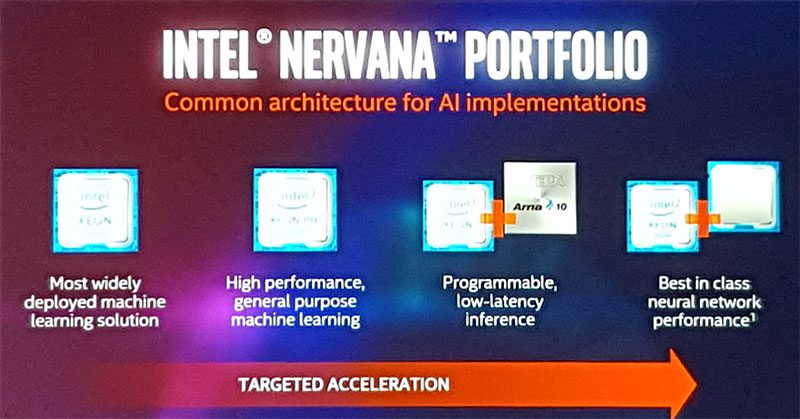

Intel is aware that they need a way to make their Altera FPGAs more accessible to the machine learning communities. It is also telling that at Intel AI day we saw Nervana become the default branding for Intel’s AI efforts.

Perhaps the most exciting part here is that Intel is betting non-x86 in an opportunity worth tens or hundreds of billions of dollars worth of hardware over the next few years. Intel is also investing in the education regarding how to use these non-x86 architectures. If you want to see an innovation engine at Intel, this type of thinking is perhaps the most exciting aspect as it is thinking outside of the x86 box to target a megatrend in AI/ machine learning.

Final Words

There is, of course, more than the above that Intel has planned for 2017. We did not want to discuss anything we have not already talked about on STH. Products do get delayed so timing may be more fluid than some people would want. The bottom line here is that Intel’s innovation engine in 2017 is going to look completely different from what we saw in 2016. While 2016 had relatively mundane updates to product lines (aside from the official launch of Knights Landing), 2017 has a slew of new technologies that will reshape how we look at servers by the end of the year. Intel also faces stiff competition on every front which is great since it is driving much of this innovation. Beyond purely compute numbers adding portfolio capabilities like x86 with FPGAs, Optane and Omni-Path into Skylake-EP sockets is going to be unlike the gradual march we have seen between Sandy Bridge (2012) and Broadwell (2016.)